大家好,又到了每日学习的时间了,今天我们来聊一聊基于FPGA的异步FIFO的实现。 一、FIFO简介 FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,它与普通

2018-06-21 11:15:25 6164

6164

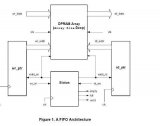

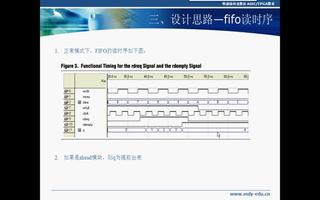

之前介绍了 SelectIO 逻辑资源,本篇咱们就聊一聊与SelectIO 逻辑资源水乳交融、相得益彰的另一个概念IO_FIFO。 1个IO_FIFO包括1个IN_FIFO 和1个OUT_FIFO

2020-11-29 10:08:00 2340

2340

FIFO是队列机制中最简单的,每个接口上只有一个FIFO队列,表面上看FIFO队列并没有提供什么QoS保证,甚至很多人认为FIFO严格意义上不算做一种队列技术,实则不然,FIFO是其它队列的基础

2022-07-10 09:22:00 1338

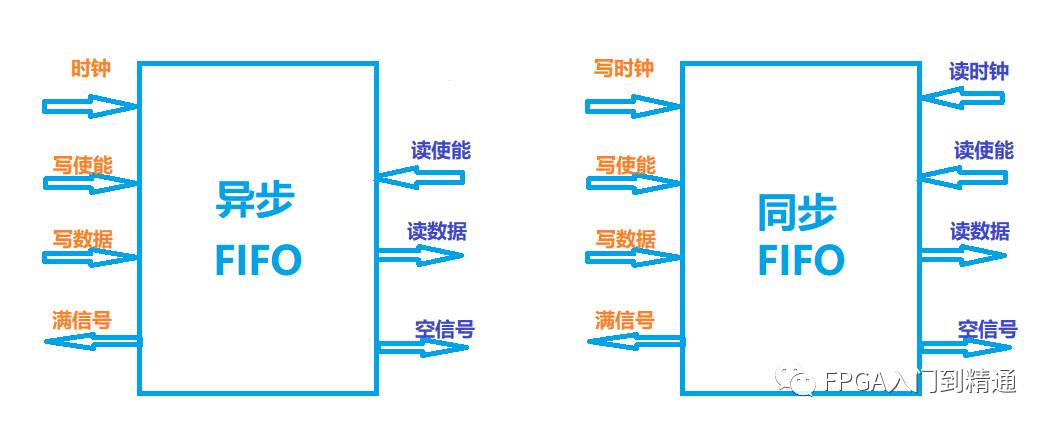

1338 FIFO (先入先出, First In First Out )存储器,在 FPGA 和数字 IC 设计中非常常用。 根据接入的时钟信号,可以分为同步 FIFO 和异步 FIFO 。

2023-06-27 10:24:37 1199

1199

FIFO自带的set_max_delay生效? 对于异步FIFO,复位信号的使用要特别注意,如下图所示。复位信号必须和wr_clk同步,如果异步,要在wr_clk时钟下同步释放,否则会出现数据无法写入

2023-11-02 09:25:01 475

475

最近加的群里面有些萌新在进行讨论**FIFO的深度**的时候,觉得 **FIFO的深度计算比较难以理解** 。所

2023-11-28 16:19:46 347

347

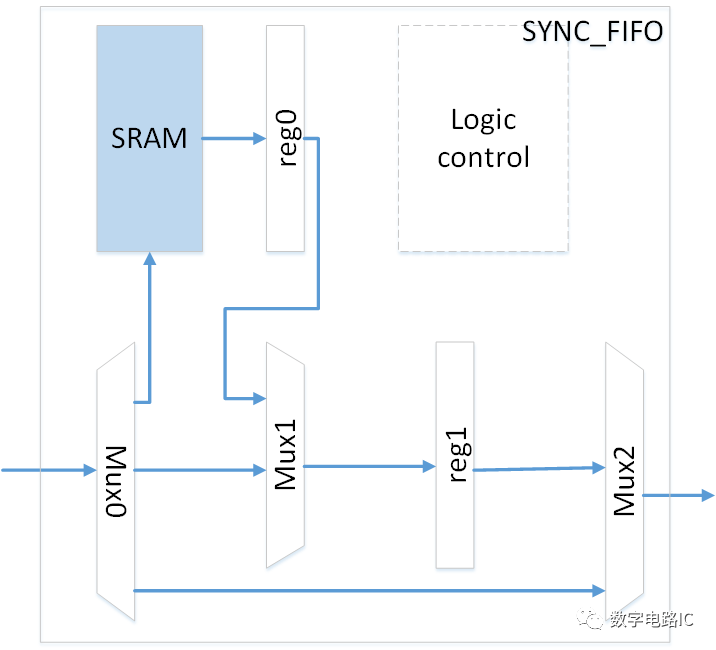

按照正常的思路,在前文完成前向时序优化和后向时序优化后,后面紧跟的应该是双向时序优化策略了,不过不急,需要先实现一下握手型同步FIFO。

2023-12-04 14:03:49 263

263

。向FIFO中读出一个数据,读地址加1。可以将FIFO想象成一个水池,写数据和读数据分别对应着注水和抽水。当注水速度快时,水池会满。当抽水速度快时,水池会空。根据读写时钟,可以分为同步FIFO和异步

2023-04-12 22:44:21

我想问一下什么情况下需要用异步FIFO,什么情况下用同步FIFO?

2014-11-03 17:19:54

本帖最后由 630183258 于 2016-11-7 10:47 编辑

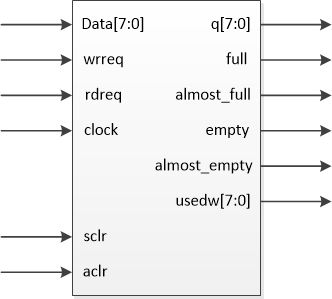

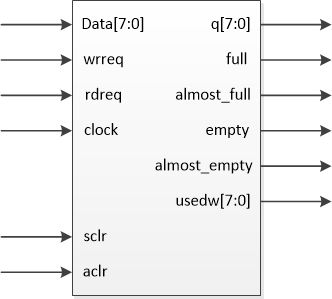

1、原理图管脚定义:fifo_in输入数据fifo_out输出数据write写使能信号,高电平有效fifo_full写

2016-11-07 00:18:04

跨时钟域处理 & 亚稳态处理&异步FIFO1.FIFO概述FIFO: 一、先入先出队列(First Input First Output,FIFO)这是一种传统的按序执行方法,先进

2022-02-16 06:55:41

异步fifo是用于跨时域时钟传输的,但是同步fifo做缓存我就不是很理解了,到底这个缓存是什么意思,这样一进一出,不是数据的传输吗,为什么加个fifo,还有,如果是两组视频流传输,在切换的过程中如何能保证无缝切换?希望哪位好心人帮我解答一下

2013-08-27 19:23:36

嗨,在我设计的FIFO同步填充在两6mbs,流媒体数据来自和ADC,用胶水逻辑关系(这是和软件无线电的应用)。如果我使用同步端点大小的1024包和1包每微帧,带宽约为8mbs。由于USB端比FIFO

2019-04-19 11:19:17

如图所示的异步FIFO,个人觉得在读写时钟同步时会产生两个时钟周期的延时,如果读写时钟频率相差不大,某一时刻读写指针相等,当写指针同步到读模块时会产生延时,实际同步到读模块的写指针是两个时钟周期之前的,这样就不会产生空满信号,要两个周期之后才能产生空满信号,结果是写溢出或读空

2015-08-29 18:30:49

首先介绍异步FIFO 的概念、应用及其结构,然后分析实现异步FIFO的难点问题及其解决办法; 在传统设计的基础上提出一种新颖的电路结构并对其进行综合仿真和FPGA 实现。

2009-04-16 09:25:29 46

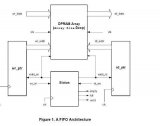

46 Applications often require FIFO buffers deeper than those offered by discrete devices. By depth

2009-05-25 14:29:36 20

20 1.什么是FIFO?FIFO是英文First In First Out 的缩写,是一种先进先出的数

2009-07-22 16:00:48 0

0 FIFO中文应用笔记

2009-07-28 10:03:31 30

30 系统在上电复位时,SPI工作在标准SPI模式,禁止FIFO功能。FIFO的寄存器SPIFFTX、SPIFFRX和SPIFFCT不起作用。通过将SPIFFTX寄存器中的SPIFFEN的位置为1,使能FIFO模式。SPIRST能在操作的任一阶

2009-09-29 10:38:26 33

33 设计一个FIFO是ASIC设计者遇到的最普遍的问题之一。本文着重介绍怎样设计FIFO——这是一个看似简单却很复杂的任务。一开始,要注意,FIFO通常用于时钟域的过渡,是双时钟设计

2009-10-15 08:44:35 94

94 本文主要研究了用FPGA 芯片内部的EBRSRAM 来实现异步FIFO 设计方案,重点阐述了异步FIFO 的标志信号——空/满状态的设计思路,并且用VHDL 语言实现,最后进行了仿真验证。

2010-01-13 17:11:58 40

40 给出了一个利用格雷码对地址编码的羿步FIFO 的实现方法,并给出了VHDL 程序,以解决异步读写时钟引起的问题。

2010-07-16 15:15:42 26

26 介绍了异步FIFO在Camera Link接口中的应用,将Camera Link接口中的帧有效信号FVAL和行有效信号LVAL引入到异步FIFO的设计中。分析了FPGA中设计异步FIFO的难点,解决了异步FIFO设计中存在的两

2010-07-28 16:08:06 32

32 摘要:使用FIFO同步源自不同时钟域的数据是在数字IC设计中经常使用的方法,设计功能正确的FUFO会遇到很多问题,探讨了两种不同的异步FIFO的设计思路。两种思路

2006-03-24 12:58:33 680

680

什么是fifo (First Input First Output,先入先出队列)这是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令。1.什么是FIFO

2007-12-20 13:51:59 11835

11835 摘要:首先介绍异步FIFO的概念、应用及其结构,然后分析实现异步FIFO的难点问题及其解决办法;在传统设计的基础上提出一种新颖的电路结构并对其进行

2009-06-20 12:46:50 3667

3667

基于FPGA的FIFO设计和应用

引 言

在利用DSP实现视频实时跟踪时,需要进行大量高速的图像采集。而DSP本身自带的FIFO并不足以支持系统中大量数据的暂时存储

2009-11-20 11:25:45 2127

2127

1 FIFO概述

FIFO芯片是一种具有存储功能的高速逻辑芯片,可在高速数字系统中用作数据缓存。FIFO通常利用双口RAM和读写地址产生模块来实现其功能。FIFO的接口信号包括异步

2010-08-06 10:22:04 5019

5019

本文采用VHDL描述语言,充分利用Xilinx公司Spartan II FPGA的系统资源,设计实现了一种非对称同步FIFO,它不仅提供数据缓冲,而且能进行数据总线宽度的转换。

2011-01-13 11:33:43 1744

1744 为了解决基于LabVIEWFPGA模块的DMAFIFO深度设定不当带来的数据不连续问题,结合LabVIEWFPGA的编程特点和DMA FIFO的工作原理,提出了一种设定 FIFO 深度的方法。对FIFO不同深度的实验表明,采

2011-09-26 13:45:17 6923

6923

关于fifo摄像头的有关资料,非常全,还内有代码

2015-11-03 11:22:07 0

0 FIFO_学习心得。 FIFO_学习心得

2015-11-09 14:07:47 6

6 异步FIFO结构及FPGA设计,解决亚稳态的问题

2015-11-10 15:21:37 4

4 基于FLASH的FIFO读写,介绍的比较详细,值得一读。

2016-04-28 10:30:27 22

22 最经典的FIFO原理,详细讲述了FIFO的原理,适合入门新手,仔细分析阅读,也适合高手查阅。

2016-05-03 15:15:08 0

0 VHDL例程 FIFO程序,感兴趣的小伙伴们可以瞧一瞧。

2016-11-10 17:12:34 4

4 FIFO 很重要,之前参加的各类电子公司的逻辑设计的笔试几乎都会考到。

2017-02-11 06:51:50 4652

4652

FIFO的使用非常广泛,一般用于不同时钟域之间的数据传输,比如FIFO的一端是AD数据采集,另一端是计算机的PCI总线,假设其AD采集的速率为16位100KSPS,那么每秒的数据量为100K

2017-09-16 09:09:09 1

1 基于FIFO的高速A_D和DSP接口设计

2017-10-19 14:10:23 9

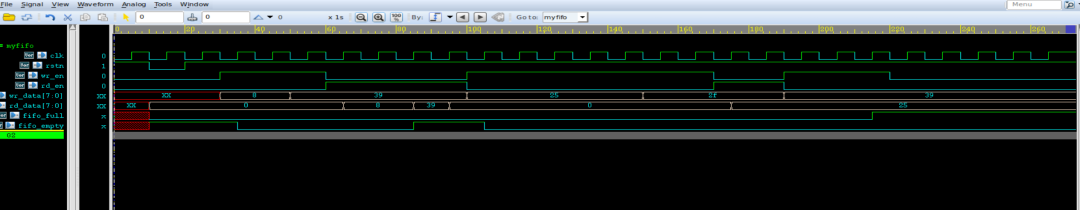

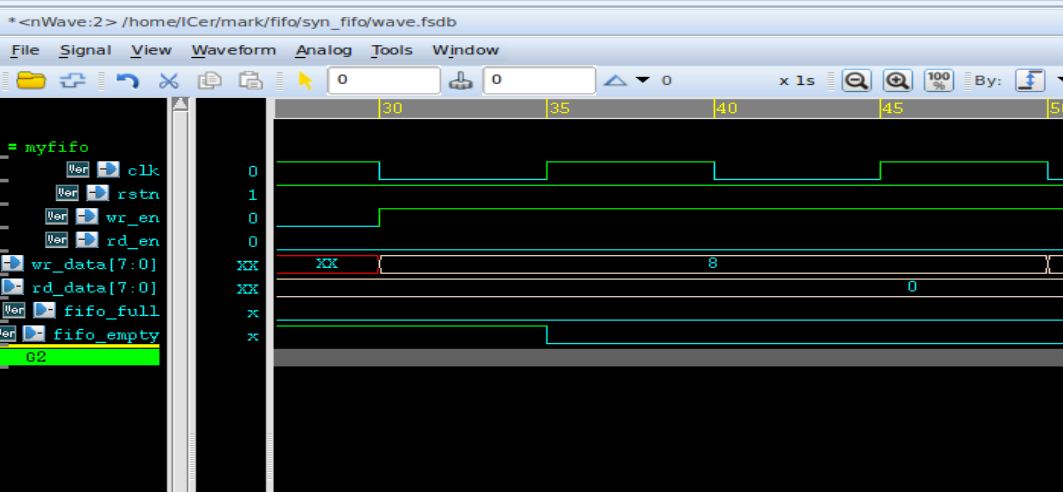

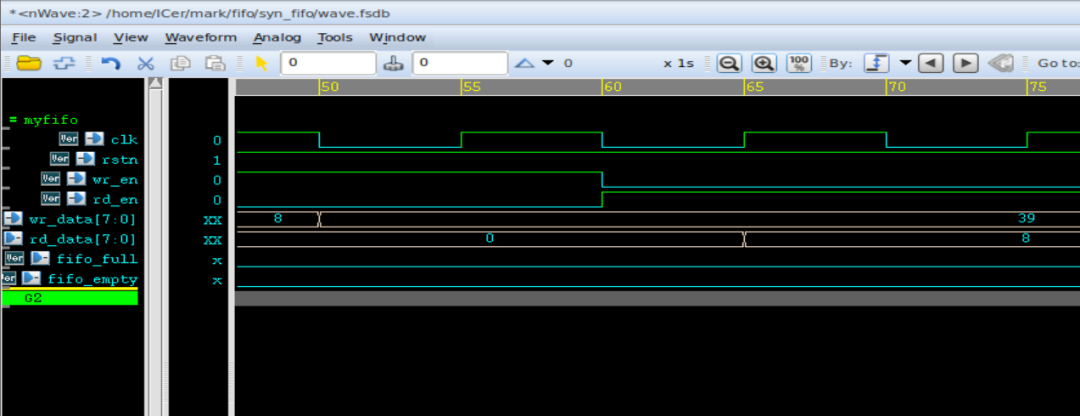

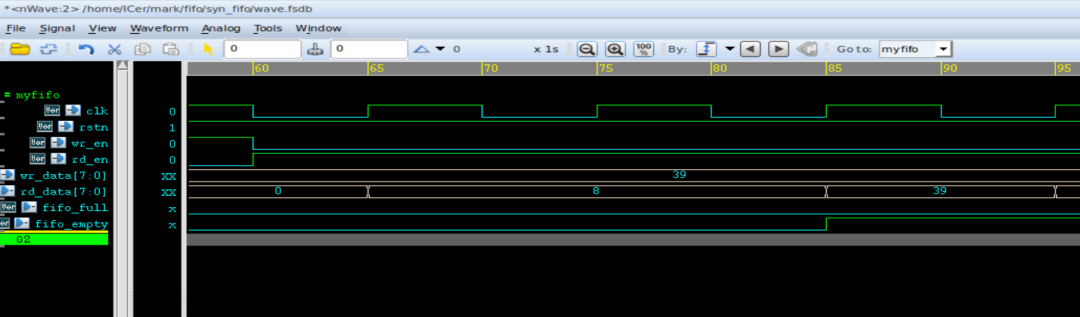

9 位宽(每个数据的位宽) FIFO有同步和异步两种,同步即读写时钟相同,异步即读写时钟不相同 同步FIFO用的少,可以作为数据缓存 异步FIFO可以解决跨时钟域的问题,在应用时需根据实际情况考虑好fifo深度即可 本次要设计一个异步FIFO,深度为8,位宽也是8。

2017-11-15 12:52:41 7993

7993

在现代电路设计中,一个系统往往包含了多个时钟,如何在异步时钟间传递数据成为一个很重要的问题,而使用异步FIFO可以有效地解决这个问题。异步FIFO是一种在电子系统中得到广泛应用的器件,文中介绍了一种基于FPGA的异步FIFO设计方法。使用这种方法可以设计出高速、高可靠的异步FIFO。

2018-07-17 08:33:00 7873

7873

FIFO( First In First Out)简单说就是指先进先出。由于微电子技术的飞速发展,新一代FIFO芯片容量越来越大,体积越来越小,价格越来越便宜。作为一种新型大规模集成电路,FIFO芯片以其灵活、方便、高效的特性。

2017-12-06 14:29:31 10173

10173

在现代的集成电路芯片中,随着设计规模的不断扩大,一个系统中往往含有数个时钟。多时钟域带来的一个问题就是,如何设计异步时钟之间的接口电路。异步FIFO(Firstln F irsto ut)是解决这个

2018-02-07 14:22:54 0

0 异步FIFO(Fist-In-First-Out)是一种先入先出的数据缓冲器[1]。由于可以很好地解决跨时钟域问题和不同模块之间的速度匹配问题,而被广泛应用于全局异步局部同步[2](Globally

2018-06-19 15:34:00 2870

2870

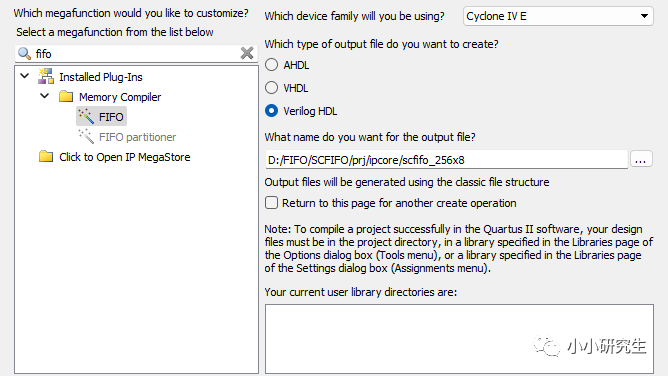

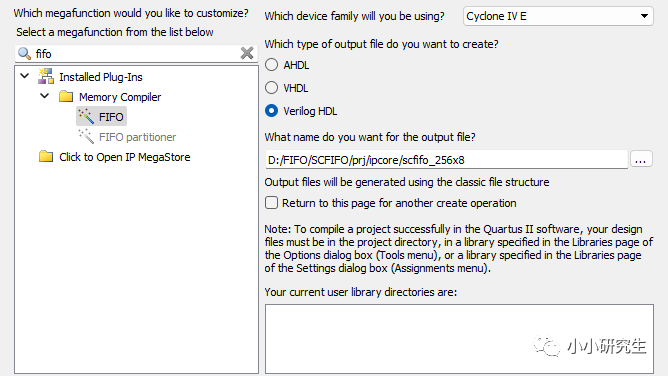

配置FIFO的方法有两种:

一种是通过QUARTUS II 中TOOLS下的MegaWizard Plug-In Manager 中选择FIFO参数编辑器来搭建自己需要的FIFO,这是自动生成FIFO的方法

2018-07-20 08:00:00 17

17 异步FIFO广泛应用于计算机网络工业中进行异步数据传送,这里的异步是指发送用一种速率而接收用另一速率,因此异步FIFO有两个不同的时钟,一个为读同步时钟,一个为写同步时钟。

2019-06-11 08:00:00 2788

2788

设计工程师通常在FPGA上实现FIFO(先进先出寄存器)的时候,都会使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其针对性变差,某些情况下会变得不方便或者将增加硬件成本。此时,需要进行自行

2018-11-28 08:10:00 6709

6709

无名管道应用的一个重大限制是它没有名字,因此,只能用于具有亲缘关系的进程间通信,在有名管道(named pipe或FIFO)提出后,该限制得到了克服。FIFO不同于管道之处在于它提供

2019-04-02 14:45:10 291

291 FIFO队列具有处理简单,开销小的优点。但FIFO不区分报文类型,采用尽力而为的转发模式,使对时间敏感的实时应用(如VoIP)的延迟得不到保证,关键业务的带宽也不能得到保证。

2019-12-02 07:02:00 1471

1471

FIFO队列具有处理简单,开销小的优点。但FIFO不区分报文类型,采用尽力而为的转发模式,使对时间敏感的实时应用(如VoIP)的延迟得不到保证,关键业务的带宽也不能得到保证。

2019-11-29 07:10:00 1595

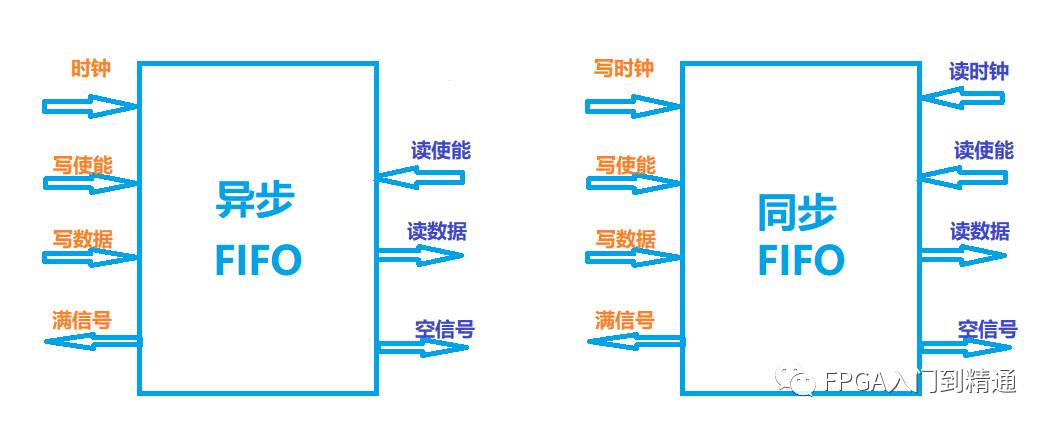

1595 根据FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟。在时钟沿来临时同时发生读写操作。异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

2019-11-29 07:08:00 1609

1609 FIFO队列不对报文进行分类,当报文进入接口的速度大于接口能发送的速度时,FIFO按报文到达接口的先后顺序让报文进入队列,同时,FIFO在队列的出口让报文按进队的顺序出队,先进的报文将先出队,后进的报文将后出队。

2019-11-29 07:04:00 4345

4345 FIFO( First Input First Output)简单说就是指先进先出。由于微电子技术的飞速发展,新一代FIFO芯片容量越来越大,体积越来越小,价格越来越便宜。

2019-11-18 07:10:00 1605

1605 FPGA电路FIFO设计的源代码

2020-07-08 17:34:37 15

15 FIFO是FPGA处理跨时钟和数据缓存的必要IP,可以这么说,只要是任意一个成熟的FPGA涉及,一定会涉及到FIFO。但是我在使用异步FIFO的时候,碰见几个大坑,这里总结如下,避免后来者入坑。

2021-03-12 06:01:34 12

12 一:fifo是什么 FIFO的完整英文拼写为FirstIn First Out,即先进先出。FPGA或者ASIC中使用到的FIFO一般指的是对数据的存储具有先进先出特性的一个存储器,常被用于数据

2021-03-12 16:30:48 2796

2796

1.定义 FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序

2021-04-09 17:31:42 4697

4697

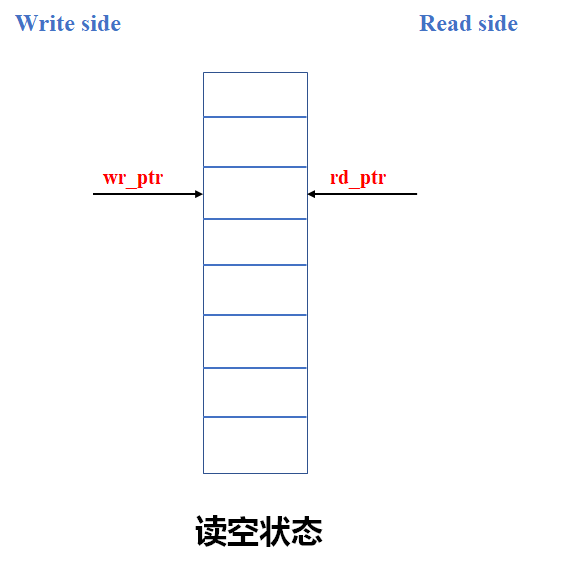

异步FIFO通过比较读写地址进行满空判断,但是读写地址属于不同的时钟域,所以在比较之前需要先将读写地址进行同步处理,将写地址同步到读时钟域再和读地址比较进行FIFO空状态判断(同步后的写地址一定

2021-08-04 14:05:21 3794

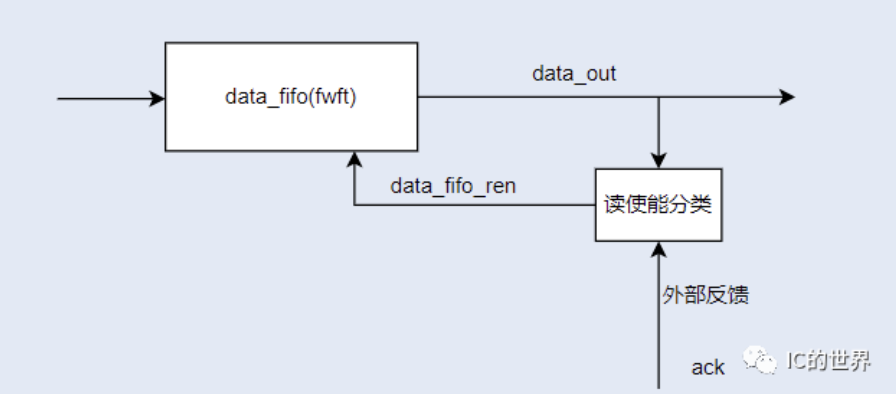

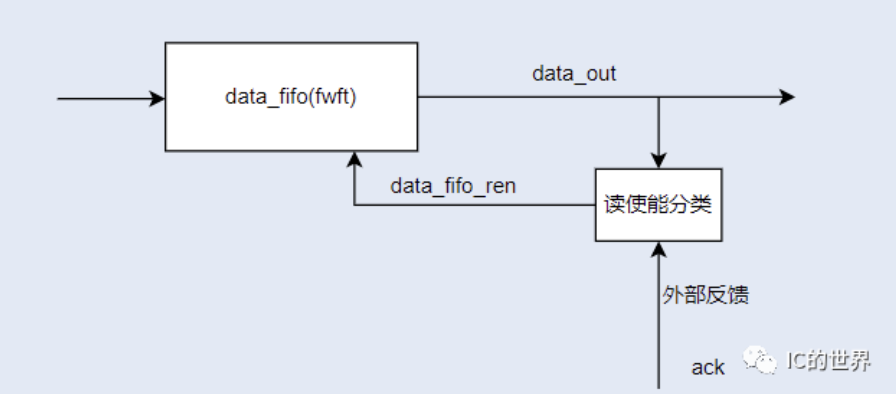

3794 FIFO是在FPGA设计中使用的非常频繁,也是影响FPGA设计代码稳定性以及效率等得关键因素。在数据连续读取时,为了能不间断的读出数据而又不导致FIFO为空后还错误的读出数据。可以将FIFO

2021-09-09 11:15:00 6293

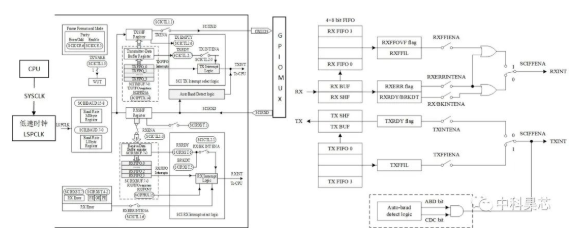

6293 STM32 串口 FIFO

2021-12-03 09:36:08 37

37 跨时钟域处理 & 亚稳态处理&异步FIFO1.FIFO概述FIFO: 一、先入先出队列(First Input First Output,FIFO)这是一种传统的按序执行方法,先进

2021-12-17 18:29:31 10

10 FIFO最常被用来解决写、读不匹配的问题(时钟、位宽),总结下来,其实FIFO最大的作用就是缓冲。既然是缓冲,那么就要知道这个缓存的空间到底需要多大。接下来的讨论,都建立在满足一次FIFO突发传输

2022-02-26 17:41:52 3045

3045

FIFO是FPGA项目中使用最多的IP核,一个项目使用几个,甚至是几十个FIFO都是很正常的。通常情况下,每个FIFO的参数,特别是位宽和深度,是不同的。

2022-03-08 11:06:12 4520

4520

在FPGA中对图像的一行数据进行缓存时,可以采用FIFO这一结构,如上图所示,新一行图像数据流入到FIFO1中,FIFO1中会对图像数据进行缓存,当FIFO1中缓存有一行图像数据时,在下一行图像数据来临的时候,将FIFO1中缓存的图像数据读出,并传递给下一个FIFO

2022-05-10 09:59:29 3056

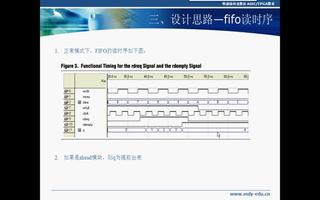

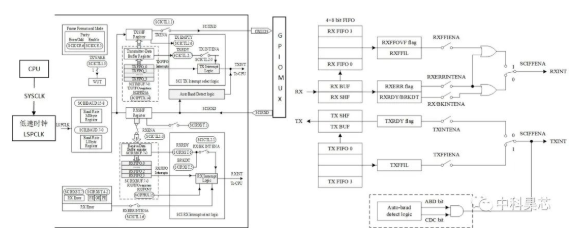

3056 自中科昊芯推出专题讲解SCI串口通信以来,第一期主要讲解SCI串口FIFO通信原理,第二期主要讲解SCI串口自动波特率,本期主要讲解FIFO中断通信逻辑。

2022-05-16 09:53:28 2301

2301

由于平时我们工作中,FIFO都是直接调用IP核,对于FIFO深度选择并没有很在意,而在笔试面试过程中,经常被问及的问题之一就是如何计算FIFO深度。

2022-07-03 17:25:28 2222

2222 FIFO的使用非常广泛,一般用于不同时钟域之间的数据传输,或者用于不同数据宽度之间的数据匹配。在实际的工程应用,可以根据需要自己写FIFO。不考虑资源的情况下,也可以使用Xilinx提供的IP核来完成。

2022-08-14 10:49:47 3567

3567 FIFO是First in First out 的缩写,一般是由寄存器reg或者ram搭起来的,相对于普通存储器而言,FIFO没有地址可操作的地址总线,因而使用比较方便,但是数据只能像水流一样排队进排队出。

2022-08-19 09:02:47 1830

1830 逻辑核™ IP FIFO生成器用户指南描述了FIFO生成器,以及有关设计、定制和实现的信息核心。

2022-08-28 11:09:00 2

2 FIFO可以缓存串口接收到的数据,因此我们可以利用FIFO来减少中断次数。以NXP的lpc1778芯片为例,接收FIFO的触发级别可以设置为1、2、4、8、14字节,推荐使用8字节或者14字节,这也是PC串口接收FIFO的默认值。

2022-10-18 10:01:18 695

695 FIFO的分类根均FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟。在时钟沿来临时同时发生读写操作。异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

2022-11-01 09:57:08 1315

1315 同步FIFO的意思是说FIFO的读写时钟是同一个时钟,不同于异步FIFO,异步FIFO的读写时钟是完全异步的。同步FIFO的对外接口包括时钟,清零,读请求,写请求,数据输入总线,数据输出总线,空以及满信号。

2022-11-01 09:58:16 1189

1189 FIFO 是我们设计中常用的工具,因为它们使我们能够在进行信号和图像处理时缓冲数据。我们还使用异步FIFO来处理数据总线的时钟域交叉问题。

2022-11-04 09:14:11 3214

3214 和写入数据(对于大型数据存储,在性能上必然缓慢),其数据地址是由内部读写指针自动加一完成的,不能像普通的存储器一样,由地址线决定读取或者写入某个特定地址的数据,按读写是否为相同时钟域分为同步和异步FIFO,这里主要介绍异步FIFO,主要用于跨时钟域传输数据。 FIFO是

2022-12-12 14:17:41 2790

2790 FIFO用于为匹配读写速度而设置的数据缓冲buffer,当读写时钟异步时,就是异步FIFO。多bit的数据信号,并不是直接从写时钟域同步到读时钟域的。

2023-01-01 16:48:00 941

941 FIFO(First In First Out)是异步数据传输时经常使用的存储器。该存储器的特点是数据先进先出(后进后出)。其实,多位宽数据的异步传输问题,无论是从快时钟到慢时钟域,还是从慢时钟到快时钟域,都可以使用 FIFO 处理。

2023-03-26 16:00:21 1824

1824

FIFO(First In First Out )先入先出存储器,在FPG设计中常用于跨时钟域的处理,FIFO可简单分为同步FIFO和异步FIFO。

2023-04-25 15:55:28 2893

2893

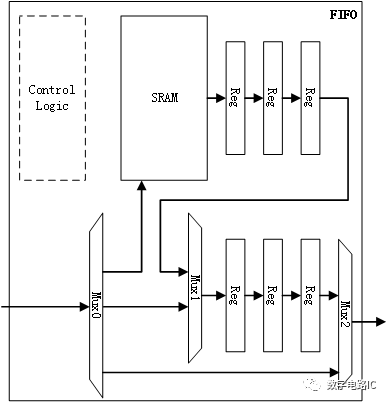

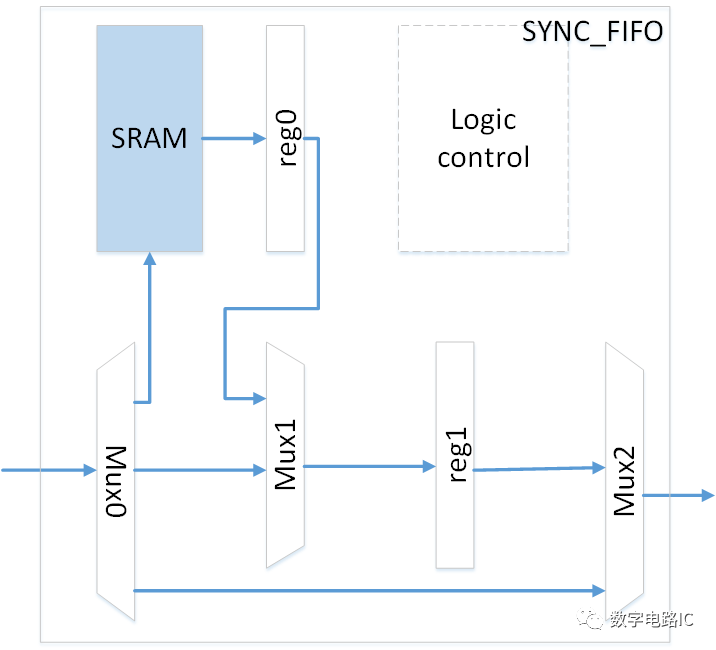

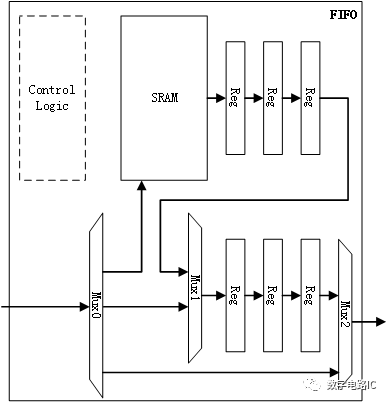

今天咱们开始聊聊FIFO的设计。FIFO是一个数字电路中常见的模块,主要作用是数据产生端和接受端在短期内速率不匹配时作为数据缓存。FIFO是指First In, First Out,即先进先出,跟大家排队一样。越早排队的人排在越前面,轮到他的次序也越早,所以FIFO有些时候也被称为队列queue。

2023-05-04 15:48:20 544

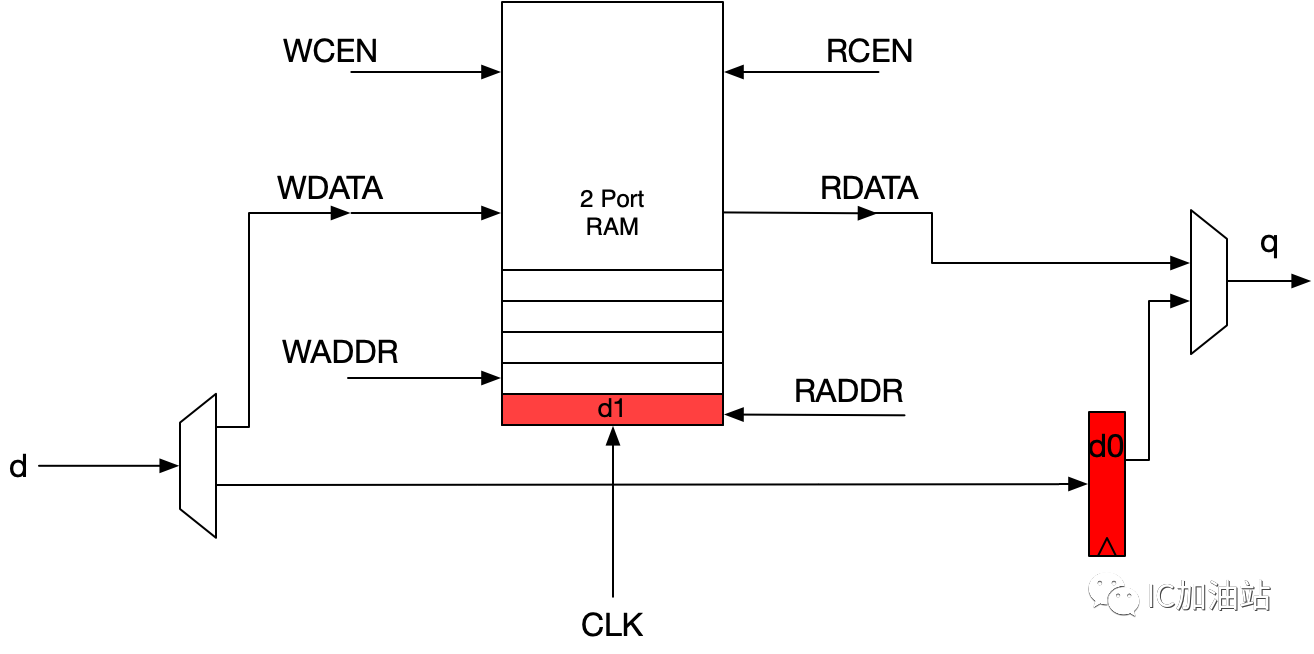

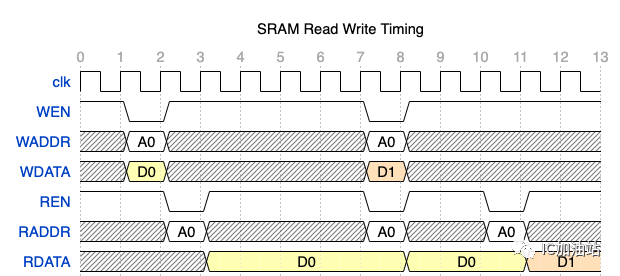

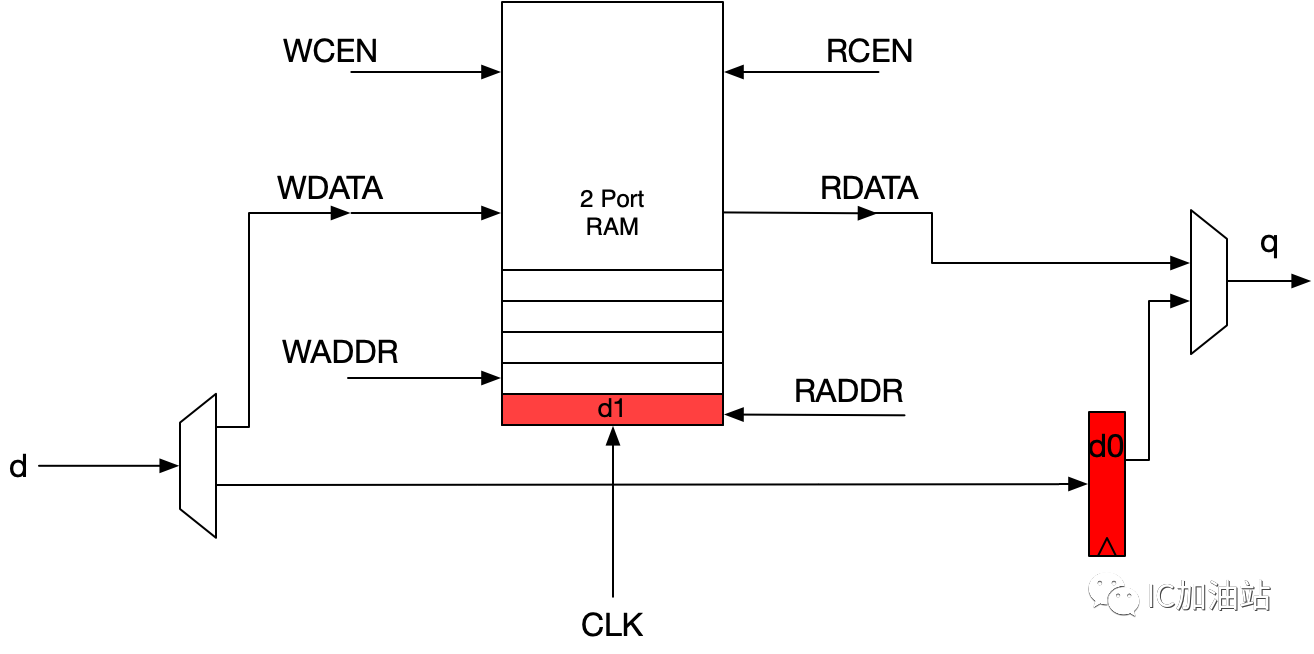

544 开始往下读之前,老李先问一个问题,假如现在让你设计一个深度为N的基于2port SRAM的同步FIFO,请问至少需要多大的SRAM? 假设SRAM的位宽就是你的数据宽度,那么问题就是问你需要的SRAM的行数至少是多少?如果你觉得答案是显而易见的N,那么你值得读完这一篇。

2023-05-04 15:55:49 629

629

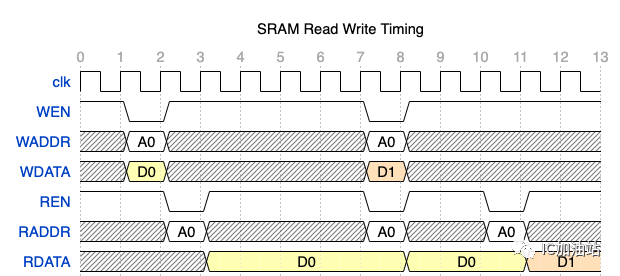

我们说这个结构之所以使得FIFO的输出Q在读完SRAM之后保持稳定,其实需要SRAM本身可以保持RDATA在读操作之后的多个周期保持稳定。即SRAM本身的读时序如下图所示:图中cycle 4,5,6都没有读操作,SRAM的RDATA依然保持D0不变。

2023-05-04 15:59:46 403

403

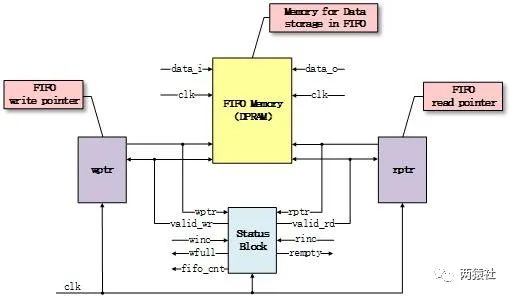

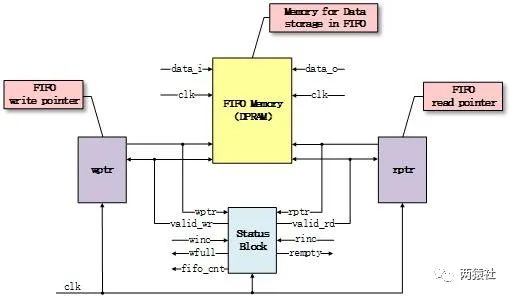

异步FIFO主要由五部分组成:写控制端、读控制端、FIFO Memory和两个时钟同步端

2023-05-26 16:17:20 911

911

FIFO,First In First Out,先入先出队列,顾名思义,即第一个到达的数据也将会是第一个离开。

2023-06-05 14:39:33 535

535

FIFO 是FPGA设计中最有用的模块之一。FIFO 在模块之间提供简单的握手和同步机制,是设计人员将数据从一个模块传输到另一个模块的常用选择。

2023-06-14 08:59:29 223

223 FIFO 是FPGA设计中最有用的模块之一。FIFO 在模块之间提供简单的握手和同步机制,是设计人员将数据从一个模块传输到另一个模块的常用选择。 在这篇文章中,展示了一个简单的 RTL 同步

2023-06-14 09:02:19 461

461 在FPGA的设计中的,内部的FIFO和RAM是两种非常常见的存储单元

2023-07-11 17:23:33 956

956 FIFO,先进先出。在FPGA中使用的FIFO一般是指对数据的存储具有先进先出的缓冲器,FIFO与普通的存储器的不同在于它没有读写地址线。举个例子,当FPGA从外部传感器读取到一连串数据时,首先

2023-07-23 11:47:03 369

369

Vivado IP核提供了强大的FIFO生成器,可以通过图形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 1628

1628

FPGA厂商提供了丰富的IP核,基础性IP核都是可以直接免费调用的,比如FIFO、RAM等等。

2023-08-07 15:41:28 1294

1294

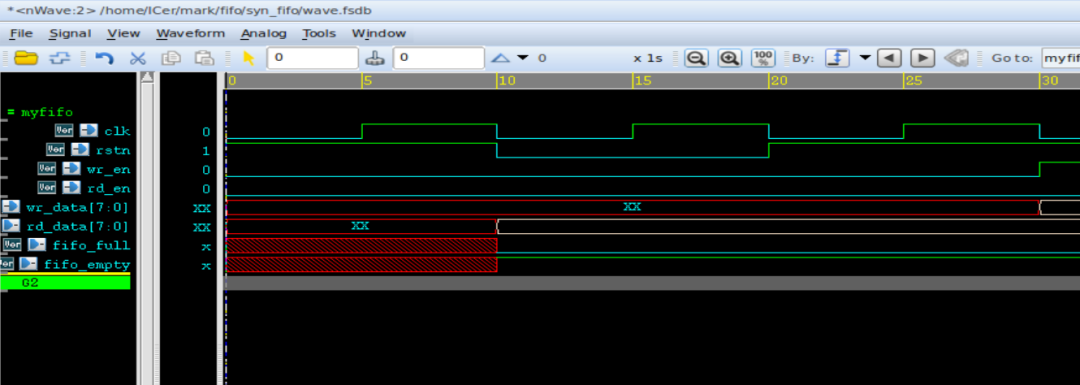

同步FIFO的设计主要包括读写地址的产生、数据的读写、以及状态的控制。下面我们将分别介绍这三个方面的设计。

2023-08-31 12:53:04 266

266 FIFO(First In First Out, 先入先出 ),是一种数据缓冲器,用来实现数据先入先出的读写方式。数据按顺序写入 FIFO,先被写入的数据同样在读取的时候先被读出,所以 FIFO存储器没有地址线,有一个写端口和一个读端口。

2023-09-07 18:30:11 821

821

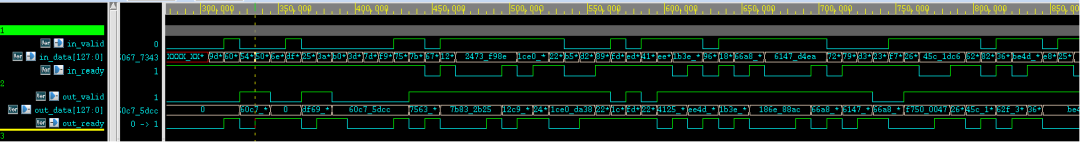

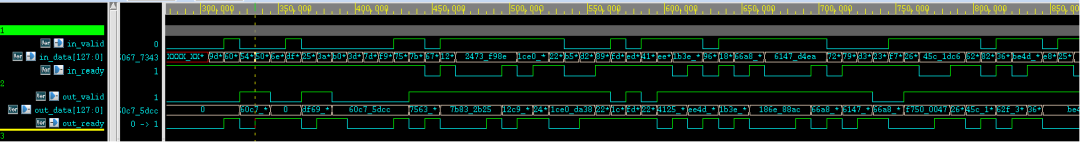

上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数据位宽是写数据位宽两倍的FIFO,然后使用读时钟频率:写时钟频率=2:3,进行简单的FIFO跨时钟域操作。

2023-09-07 18:31:35 759

759

FIFO在设计是一个非常常见并且非常重要的模块,很多公司有成熟的IP,所以一部分人并没有人真正研究写过FIFO,本文仅简述FIFO中部分值得保留的设计思路。

2023-09-11 17:05:51 356

356

模块虽小但是要有新意,首先写一个同步FIFO,这是一个烂大街的入门级项目,但是我肯定不会写的那么简单

2023-09-11 17:11:07 333

333

异步FIFO包含"读"和"写“两个部分,写操作和读操作在不同的时钟域中执行,这意味着Write_Clk和Read_Clk的频率和相位可以完全独立。异步FIFO

2023-09-14 11:21:45 545

545

为什么异步fifo中读地址同步在写时钟域时序分析不通过? 异步FIFO中读地址同步在写时钟域时序分析不通过的原因可能有以下几个方面: 1. 读地址同步在写时钟域时序分析未覆盖完全 在时序分析时,可能

2023-10-18 15:23:55 312

312 同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用? 1. 同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO在处理时序有明显的区别。同步FIFO相对来说是较为

2023-10-18 15:23:58 790

790 请问异步FIFO的溢出操作时怎么样判断的? 异步FIFO是数据传输的一种常用方式,在一些储存器和计算机系统中,常常会用到异步FIFO。作为一种FIFO,异步FIFO经常面临两种情况:溢出

2023-10-18 15:28:41 299

299 本文将简述一种fifo读控制的不合理设计案例,在此案例中,异常报文将会堵在fifo中,造成头阻塞。

2023-10-30 14:25:34 159

159

电子发烧友App

电子发烧友App

评论