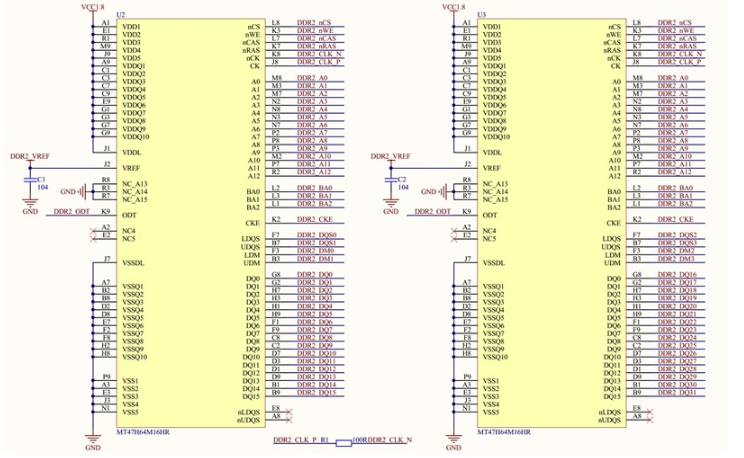

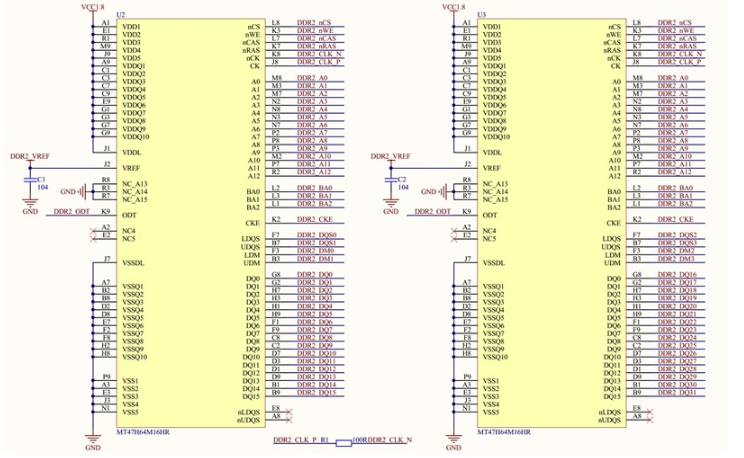

每片DDR2存储器的容量为1Gb,两片DDR2芯片组合,得到总容量为2Gb。单DDR2存储器为16bit,两片存储器共用控制线和地址线,数据线并列,即组成了32位的2Gb存储模组。

2020-08-21 15:09:00 5493

5493

本文首先列出了DDR2布线中面临的困难,接着系统的讲述了DDR2电路板设计的具体方法,最后给出个人对本次电路设计的一些思考。

2020-11-20 10:28:35 6386

6386 描述Arduino DUE SODIMM(DDR2 规格)DDR2 SODIMM 封装中的 Arduino DUE

2022-09-13 06:46:33

在quartus2中创建了一个DDR2 控制器的ip核 ,但是在选择 DDR型号的时候,找不到我要用的DDR芯片信号 怎么办?选择了一个DDR芯片将它的行列bits数改了之后 发现 内存大小又不对 。求解答

2017-09-19 14:50:23

我想用s3c2450外接128MB的DDR2内存,就是说用两片64MB的DDR2拼一下。 请问高手应该怎样连接? 谢谢

2022-06-22 12:01:49

。但我也无法在ddr2包装器ucf文件中找到这些信号。能告诉我如何解决这些错误吗?我已附上PAR报告和顶级模块的ucf文件以及此邮件。等待您的回复。system.txt.ucf 33 KBpar_report.txt 20 KB

2020-06-18 10:36:34

嗨,DDR2内存型号的最低频率是多少?我们可以尝试低于125 Mhz的DDR2内存型号吗?问候 - sampath

2020-05-27 09:24:15

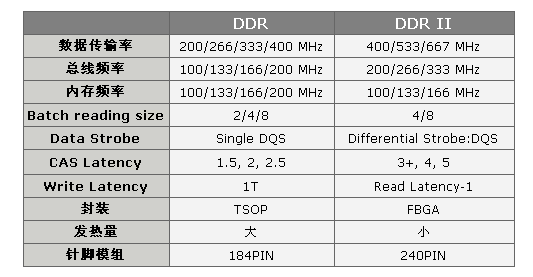

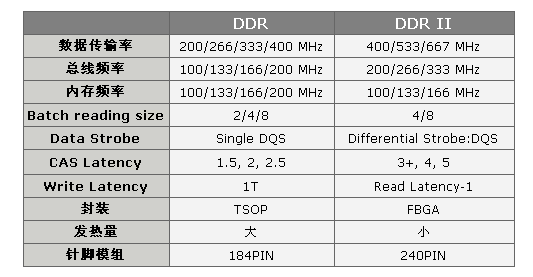

从上表可以看出,在同等核心频率下,DDR2的实际工作频率是DDR的两倍。这得益于DDR2内存拥有两倍于标准DDR内存的4BIT预读取能力。

2019-08-08 07:11:44

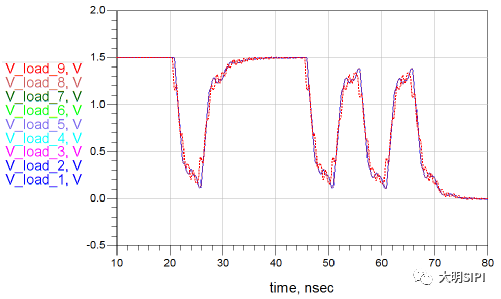

1、 在读数据时,打开主控端的ODT,关闭DDR2端的 ODT;而在写数据时,则相反;数据线空闲时,则关闭两端的ODT。2、 对于DDR2 800,设置寄存器,使主控端和DDR2端的ODT阻值为50

2019-05-30 08:10:00

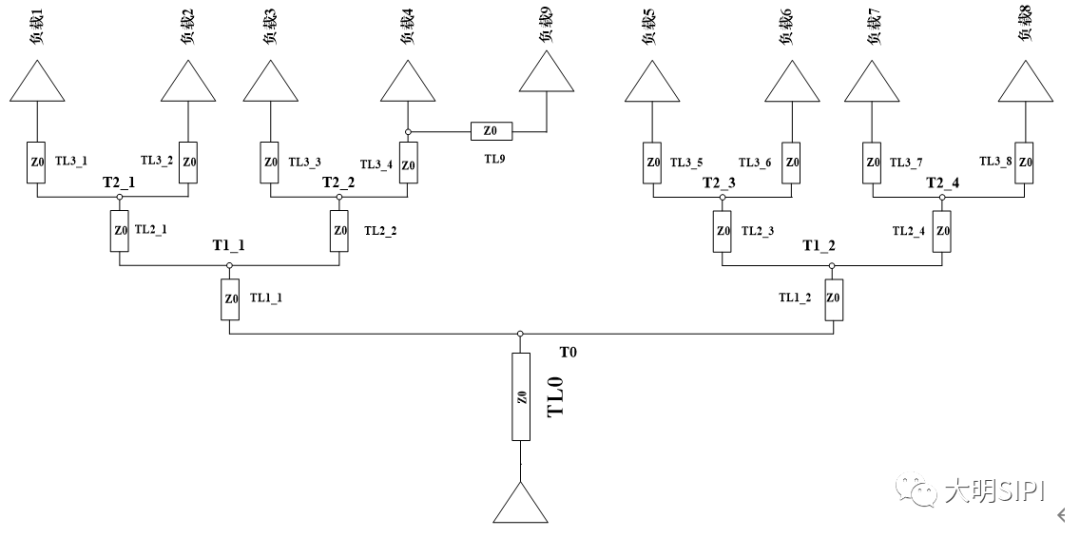

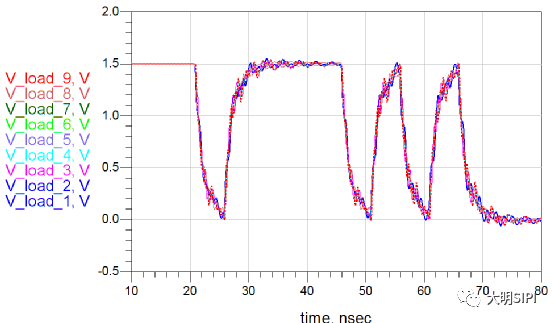

主要是针对DDR2 667内存的设计。信号分组:DDR2的布线中习惯把信号分成若干组来进行设计,分成同组的信号具有相关或者相似的信号特性。时钟组:差分时钟信号,每一对信号都是同频同相的。ckp0

2011-10-27 14:53:32

DDR2时钟线走线规则a)时钟线包括MEM_CLKOUT#0、MEM_CLKOUT0、MEM_CLKOUT#1、MEM_CLKOUT1,MEM_CLKOUT#2、MEM_CLKOUT2

2015-02-03 14:13:44

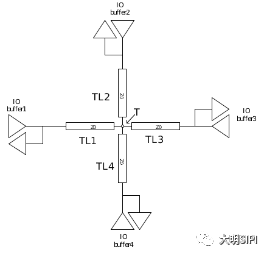

本次设计中CPU的封装为BGA844-SOC-Y,DDR2的封装为FBGA84,DDR2的控制总线采用星形连接,使用的PCB软件为AltiumDesigner10

2019-07-30 06:29:28

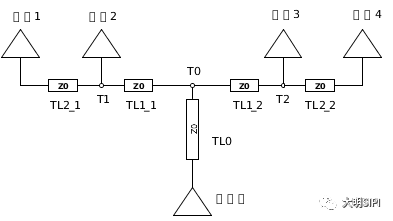

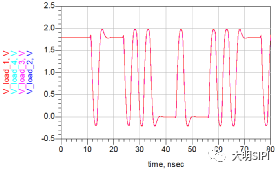

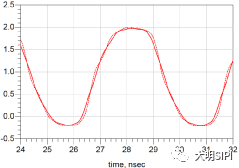

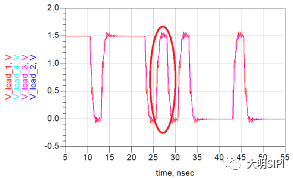

DDR2设计原理 DDR2 designBasic knowledge? Source Sync Bus Analysis? On-Die Terminations (ODT)? Slew Rate

2009-11-19 09:59:04

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之处?

2021-03-12 06:22:08

求一DDR2接口设计代码

2013-04-24 10:00:36

[size=14.3999996185303px]我有个ARM的板子,DDR2和NAND的数据线是复用的,这样PCB走线的时候,除了原来DDR2高速信号走线阻抗和等长以外,还需要特别注意什么吗。NAND的线长是不是不算入DDR2总的线长中。

2016-10-10 17:09:28

(频带外的不必要辐射)为目的,介绍使用了片状铁氧体磁珠和片状电感器的移动终端的PA电源线的噪声对策方法。 通过有线连接的RF信号质量的评估项目中,有ACLR*1(临道泄露功率比)和SEM*2(频谱发射

2018-10-10 16:50:20

本帖最后由 芯航线跑堂 于 2016-12-19 00:25 编辑

AC6102 DDR2测试工程本文档介绍AC6102上DDR2存储器基于Verilog代码的测试过程。AC6102上使用了2

2016-12-15 14:43:40

最近在做ddr2方面的东西,需要仿真ddr2,可是一直没有头绪。xx_example_top_tb仿真不知道是对是错,网上说的外挂美光ddr2 模型的仿真方法,没有具体讲解。哪位大虾能够指点一二哇,不甚感激!

2016-06-29 15:50:28

DR2与DDR有哪些区别?DDR3与DDR2的区别是什么?

2021-10-26 06:15:07

大家好,我们可以在这里讨论使用DDR2 / DDR3内存与FIFO(我的好奇心)的差异/优点/缺点。以上来自于谷歌翻译以下为原文Hi All, Can we discuss here

2019-02-14 06:14:38

本次发布 Gowin DDR2 Memory Interface IP 参考设计及 IP CoreGenerator 支持调用 Gowin DDR2 Memory Interface IP

2022-10-08 07:25:25

Gowin DDR2 Memory Interface IP用户指南主要内容包括 IP 的结构与功能描述、端口说明、时序说明、配置调用、参考设计等。主要用于帮助用户快速了解 Gowin DDR2 Memory Interface IP 的产品特性、特点及使用方法。

2022-10-08 07:08:19

IBIS Models for DDR2 Analysis 仿真

2012-03-16 16:52:07

嗨,我找不到N2815A电缆的任何文件,所以我的问题是订购哪种电缆(U4201A或N2815A)是正确的,以便与U4164A和DDR3探头(电缆E5845A)或DDR2探头(电缆E5384A

2018-10-18 16:57:26

有人用Xilinx ISE的mig生成ddr2,然后进行调试的吗?如果选择了内含pll,顶层时钟怎么连接

2014-09-15 19:14:41

; is not a bus or arrayError (12014): Net "DDR2:DDR2U|mem_dq[15]", which fans out to "DDR2

2014-03-18 19:55:04

quartus ii 调用DDR2 IP核时无法生成 ( 已经完成破解获得ddr2的license)

2017-02-07 17:29:25

在DDR2 MIG的使用时,想把DDR2封装成一个FIFO使用,但是有些问题不是太明白。在MIG的User Interface接口中,提供给控制器的数据是上升沿和下降沿的拼接,一个周期提供两个数据到

2015-03-29 18:41:43

1、从工作平率上说:首先接口就全部不同 电压不同 频率的计算方法不同 SDR的频率就是外频 133=133 DDR的频率就是外频的2倍 133=266 DDR2的频率就是外频的4倍 133=533

2014-12-30 14:35:58

1、从工作平率上说:首先接口就全部不同 电压不同 频率的计算方法不同 SDR的频率就是外频 133=133 DDR的频率就是外频的2倍 133=266 DDR2的频率就是外频的4倍 133=533

2014-12-30 14:36:44

), .reset_request_n (), .soft_reset_n (tie_high)); 以mem开头的一堆信号,是直接导出为顶层引脚,去连接PCB板上的DDR2芯片的。以local开头的一堆信号

2020-02-25 18:33:00

本帖最后由 一只耳朵怪 于 2018-5-25 14:46 编辑

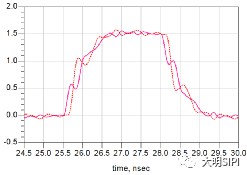

TI工程师: 您好,我在官网上下载了DM368的IBIS模型,仿真DDR2时,DM368的DDR2地址信号和其它控制信号,以及

2018-05-25 07:24:50

并不会注意一些数字上的差异,如DDR3和DDr2,或许大多数人都会追求时髦选择DDR3,但是你真的了解DDR2与DDR3的区别吗?作为消费者,其实我们可主宰自己的命运,用知识的武器捍卫自己的选择。下面

2011-12-13 11:29:47

我正在使用带有 ECC 芯片的 4GB DDR3 RAM 连接到 T1040 处理器 DDR 控制器。

我尝试了这个序列,但未能成功生成 DDR 地址奇偶校验错误:

步骤1:

ERR_INT_EN

2023-05-31 06:13:03

的接口连接。DDR2芯片的连接电路如图2.27所示。 图2.27 DDR2芯片接口电路DDR2芯片接口以及PCB layout,通常需要遵循以下的原则。● 单端信号的电路板阻抗一般控制在50 ohm

2016-08-12 17:59:50

“mem_*”的接口,是DDR2 IP核与FPGA外部DDR2芯片的接口。对于第一类接口,功能描述如表4.1所示。表4.1 DDR2 IP核系统接口列表信号名方向功能描述

2016-10-27 16:36:58

)线必须连接到FPGA 的引脚名带有DQ的pin;DDR2的DQS线必须连接到FPGA 的引脚名带有DQS的pin,DDR2的地址线连接到FPGA 的普通I/O引脚;DDR2的DM信号连接到FPGA

2017-09-25 17:51:50

小弟最近使用DDR2的IP核的时候,发现在新建完成的时候有个警告:ddr2_pht.v exit but should have been created by IPToolbench。正是这个警告

2017-03-09 22:50:15

嗨!我有一个带有DDR2内存的Sparten6 xc6slx150-csg484项目(MT47H64M16HR-3E)。但是当我创建一个MIG.DoseMIG支持这个DDR2时,我不能用DDR2吗?ISE:13.4MIG:3.9

2020-04-10 08:06:02

大家好, 如果有人可以在virtex 4上调试一个DDR2,那就太棒了。我正在使用电源PC和PLB DDR IP。我可以看到所有DDR 2控制信号都出现在我们主板上的DDR 2内存上。如果我查看

2018-09-30 11:07:28

在与SDRAM相同的总线时钟频率下达到更高的数据传输率。虽然DDR2和DDR一样,都采用相同采样方式进行数据传输,但DDR2拥有两倍于DDR的预读取系统命令数据的能力。也就是说,在同样100MHz

2011-05-03 11:31:09

信号的时候刷新,这三者的不同之处在于,每次读写刷新会浪费几个时钟周期,手动刷新引脚是设置刷新而刷新,其中推荐采用手动刷新,可以在空闲的时候刷新DDR2, 就可以避免操作的时候因为打开刷新而浪费的几个

2015-03-16 20:21:26

基于CPLD和DDS的数频源设计如何改善信号源的频谱质量?

2021-04-30 06:46:43

嗨!我正在寻找Spartan-3A / 3ANFPGA入门KitBoard用户指南(UG334)。具体来说第13章:DDR2 SDRAM和我不明白如何使用DDR2 SDRAM,因为例如这个内存

2019-07-31 06:18:10

GPM模型在DDR2设计中的应用是什么?

2021-05-26 06:11:13

你好我正在使用atlys主板,我必须在spartan-6上实现ddr2(MT47H64M16-25E)接口,...通过使用MIG及其示例设计,在模拟中一切正常....通过注意ddr2接口,例如

2019-10-28 07:46:43

你好 ! 我想设计一个框架,我们想出的设计具有以下特点: 1:DDR3(MT47H64M16HR-3 ofmicron inc。) 2:USB 但我不知道如何设计DDR2原理图,而且我还没有找到关于

2019-09-06 07:55:42

,以便我可以将它们连接到外部逻辑分析仪板,但是再次实现失败,说它在设计中找不到DDR2信号(???)。有谁知道可能会发生什么以及探测DDR2总线以便调试的可靠方法?消息由shrutiparashar

2019-05-10 14:25:23

何谓天线阵列?有什么方法可以改善无线信道的传输质量吗?

2021-06-01 06:00:16

求四片DDR2的例子,非常感谢

2014-07-14 16:33:45

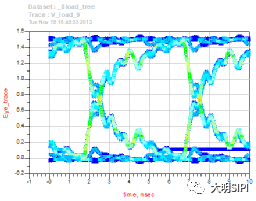

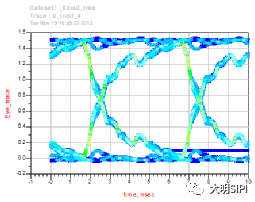

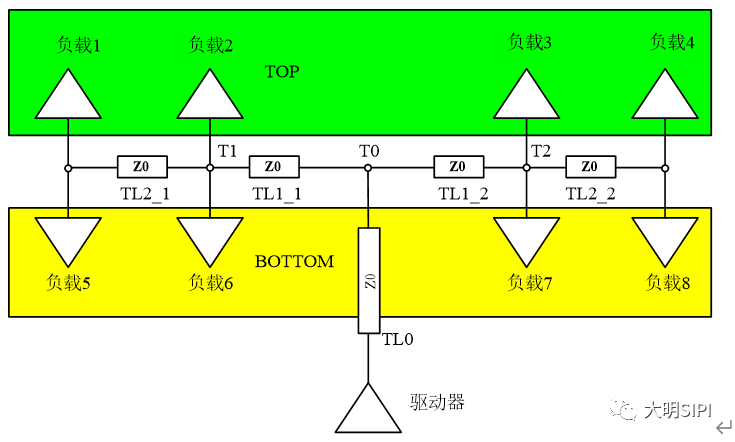

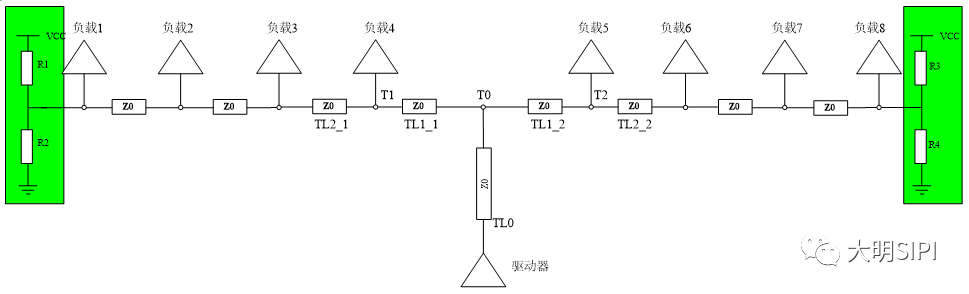

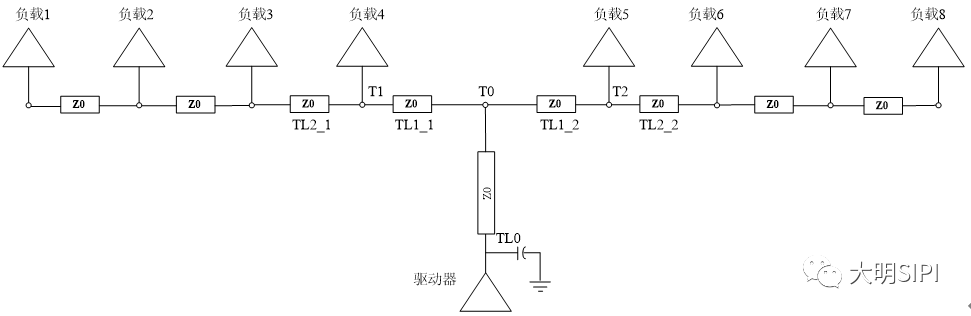

PCB布线设计的好坏直接影响到硬件电路能否正常工作或运行多快的速度。而在高速数字PCB设计中,DDR2是非常常见的高速缓存器件,且其工作频率很高本文将针对DDR2的PCB布线进行讨论。DDR2

2016-12-26 16:56:05

个DQSn,即DQS/DQSn为一对差分数据时钟,用差分时钟还是单独信号作为时钟是可以通过初始化寄存器时进行设置的。 最后还是比较电气特性,DDR2已经降到了1.8V,若要最大限度的提升速度,降低

2014-12-30 15:22:49

我们知道ddr2有速度等级和存储量大小之分。在用altera FPGA设计的时候调用IP核到底该怎样选择ddr2呢?比如说640*480*8bit@60hz的视频信号,该选择什么ddr2呢?怎么计算

2018-01-31 11:00:13

将数据发送,接收再存储入DDR2,再将数据以灯的形式显示出来,灯型数据不对。自己实在找不到错误如果不存入DDR2,直接接收数据显示,一切正常,加上DDR2之后,从DDR2读取就无法正常显示观察灯型

2018-08-10 11:24:19

如何操作才能使得ddr2降频,是更换晶振还是操作寄存器呢?pll2是产生ddr2的clk,但是手册上说明clk=clkin2*20/2.说明软件是改不了的吗?

2018-08-02 09:10:45

存取频率是多少?我咨询一家板卡商,他们回复说C6748外接的DDR2的最高运行频率是312Mhz,如果这个速度是真的,那么,就是说DSP对DDR2的存取速度也是312MHz,这对于DSP内核456MHz的最高速度来说,是不是拖累了DSP内核,影响最高性能呢?是否可以使用更高频率的DDR2来改善呢?

2020-07-30 08:19:32

架构的DDR2,所以一组内的DQ仅需要8个,而有的DQS带有9个DQ,在选用该DQ的时候只要任意选取其中的8个就可以。在SSTL-18电平标准中,为了实现更高的信号频率,输入信号需要和一个参考电压

2019-05-31 05:00:05

DDR2 SDRAM控制器的设计与实现

本文介绍了&&," -&,+. 的基本特征!并给出了一种&&," -&,+. 控制器的设计方法!详述了其基本结构和设计思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 DDR2名词解释

DDR2的定义:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准,它与上一代DDR内

2009-04-26 18:02:22 1186

1186

DDR2内存传输标准 DDR2可以看作是DDR技术标准的一种升级和扩展:DDR的核心频率与时钟频率相等,但数据频率为时钟频率的两倍,也

2009-04-26 18:05:40 786

786

什么是DDR2 SDRAM

DDR2的定义:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技

2009-12-17 11:17:59 623

623 DDR2的定义:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准,它与上一代DDR内存技术标准最大的不

2009-12-17 16:26:19 731

731 DDR2内存传输标准

DDR2可以看作是DDR技术标准的一种升级和扩展:DDR的核心频率与时钟频率相等,但数据频率为时钟频率的两倍,也就是说在一个时钟周期内必须传输

2009-12-24 14:53:28 621

621 DDR2传输标准

DDR2可以看作是DDR技术标准的一种升级和扩展:DDR的核心频率与时钟频率相等,但数据频率为时钟频率的两倍,也就是说在一个时钟周期内必须传输两次

2009-12-25 14:12:57 434

434 DDR2乏人问津 DRAM厂抢转产能

DDR2和DDR3 1月上旬合约价走势迥异,DDR2合约价大跌,DDR3却大涨,凸显世代交替已提前来临,将加速DDR2需求急速降温,快速转移到DDR3身上,

2010-01-18 16:04:44 1094

1094 DDR2,DDR2是什么意思

DDR2(Double Data Rate 2) SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准,它与上一代DDR内

2010-03-24 16:06:36 1381

1381 SDRAM, DDR, DDR2, DDR3 是RAM 技术发展的不同阶段, 对于嵌入式系统来说, SDRAM 常用在低端, 对速率要求不高的场合, 而在DDR/DDR2/DDR3 中,目前基本上已经以DDR2 为主导,相信不久DDR3 将全面取代

2012-01-16 14:53:01 0

0 ISS 的DDR2 的设计指导,虽是英文,但很有用。

2015-10-29 10:53:38 0

0 总结了DDR和DDR2,DDR3三者的区别,对于初学者有很大的帮助

2015-11-10 17:05:37 36

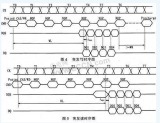

36 DDR2 SDRAM操作时序规范,中文版规范

2015-11-10 17:42:44 0

0 Xilinx FPGA工程例子源码:DDR2 Controller

2016-06-07 11:44:14 24

24 本文首先列出了DDR2布线中面临的困难,接着系统的讲述了DDR2电路板设计的具体方法,最后给出个人对本次电路设计的一些思考。

2017-09-19 11:27:21 22

22 了时变多普勒和伪距的模拟,生成了卫星导航接收机处的复杂信号。播放硬件以FPCA和DDR2为基础,通过PCI将信号文件传入DDR2,在FPCJA中实现了数据的连续读取,经插值滤波和数模转换后形成中频信号,再经射频调制输出。通过北斗接收机的

2017-11-09 11:43:02 8

8 DDR2(Double Data Rate2)SDRAM是由JEDEC(电子设备工程联合委员会)制定的新生代内存技术标准,它与上一代DDR内存技术标准最大的不同:虽然采用时钟的上升/下降沿同时传输

2017-11-25 01:41:01 3855

3855

本文章主要涉及到对DDR2和DDR3在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关技术,其中一些设计方法在以前已经成熟的使用过。

2018-02-06 18:47:57 2638

2638

突发长度,由于DDR3的预期为8bit,所以突发传输周期(BL,Burst Length)也固定位8,而对于DDR2和早期的DDR架构的系统,BL=4也是常用的,DDR3为此增加了

2018-06-21 09:20:54 14616

14616

DDR2 设备概述:DDR2 SDRAM接口是源同步、支持双速率传输。比如DDR SDRAM ,使用SSTL 1.8V/IO电气标准,该电气标准具有较低的功耗。与TSOP比起来,DDR2 SDRAM的FBGA封装尺寸小得多。

2019-06-22 10:05:01 1793

1793

本文档的主要内容详细介绍的是DDR和DDR2与DDR3的设计资料总结包括了:一、DDR的布线分析与设计,二、DDR电路的信号完整性,三、DDR Layout Guide,四、DDR设计建议,六、DDR design checklist,七、DDR信号完整性

2020-05-29 08:00:00 0

0 一些设计方法在以前已经成熟的使用过。 1 介绍 目前,比较普遍使用中的DDR2的速度已经高达800 Mbps,甚至更高的速度,如1066 Mbps,而DDR3的速度已经高达1600 Mbps。 对于如此高的速度,从PCB的设计角度来帮大家分析,要做到严格的时序匹配,以满足信号的完整性,

2021-03-25 14:26:01 3864

3864

DDR,DDR2,DDR3,DDR4,LPDDR区别作者:AirCity 2019.12.17Aircity007@sina.com 本文所有权归作者Aircity所有1 什么是DDRDDR

2021-11-10 09:51:03 154

154 5片DDR2设计分享

2022-12-30 09:19:26 4

4

正在加载...

电子发烧友App

电子发烧友App

评论