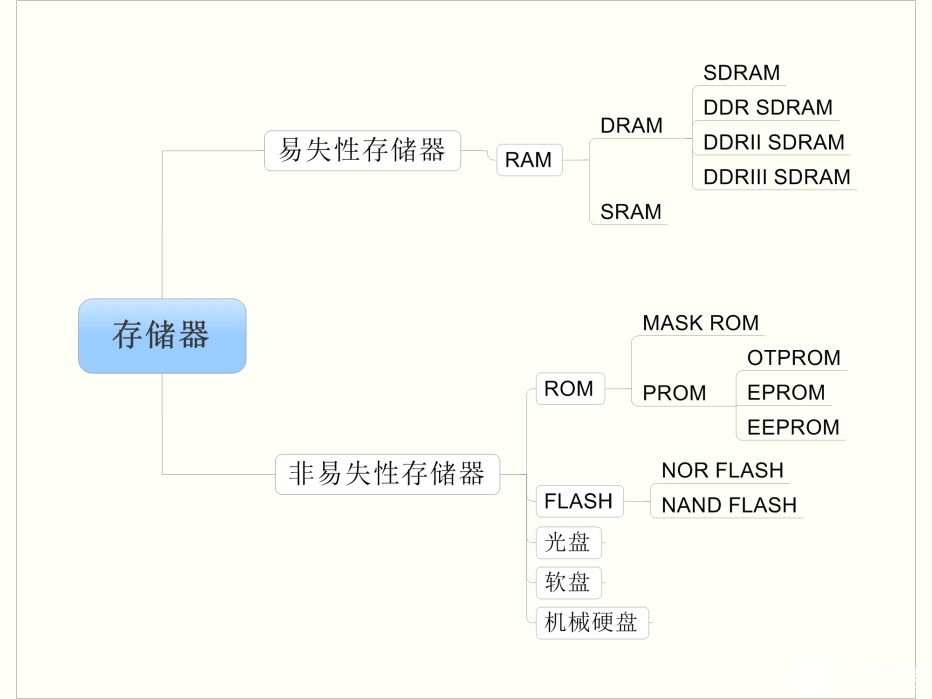

本文主要介绍FPGA中常用的RAM、ROM、CAM、SRAM、DRAM、FLASH等资源,包括特性、工作原理、应用场景等。

一、RAM

RAM(Random Access Memory)是FPGA中最基本和常用的内部存储块,根据不同架构可以实现不同容量,最大可达几十Mb。

FPGA中的RAM主要包括:

- 分布式RAM:存在于逻辑块(LE)中的小容量RAM,通常为几百比特到几千比特。

- 块RAM:FPGA中专门用于实现RAM功能的大容量存储块,每个块RAM容量从几kb到几十kb不等。

- UltraRAM:某些高端FPGA特有的大容量RAM块,比块RAM具有更高的密度和带宽。

1、分布式RAM(Distributed RAM)

分布式RAM利用查找表(LUT)的功能实现,不需要占用额外Flip-Flop,但会占用可用于逻辑实现的LUT资源。

每个LUT可以实现一个小容量的RAM,例如6输入LUT实现64位RAM。

注意分布式RAM只能实现同步读写操作。

2、块RAM(Block RAM)

每个块RAM通常有单端口、双端口和四端口版本。

支持同步读写操作,可以通过多端口实现FIFO等功能。

例如Xilinx UltraScale FPGA中一个块RAM容量为36kb,位宽可配置,延时很小,频率可以达到550MHz。

3、UltraRAM

UltraRAM集成在部分高端FPGA中,每个UltraRAM可以达到数十Mb的容量,具有比块RAM更高的密度和带宽。

UltraRAM可以与块RAM一起使用,实现更大容量的存储解决方案。

Verilog 代码示例

(* ram_style = "distributed" *) reg [7:0] dist_ram[0:63]; // 64 x 8 的分布式RAM

(* ram_style = "block" *) reg [31:0] block_ram[0:1023]; // 1K x 32 的块RAM

(* ram_style = "ultra" *) reg [7:0] ultra_ram[0:262143]; // 256K x 8 的UltraRAM

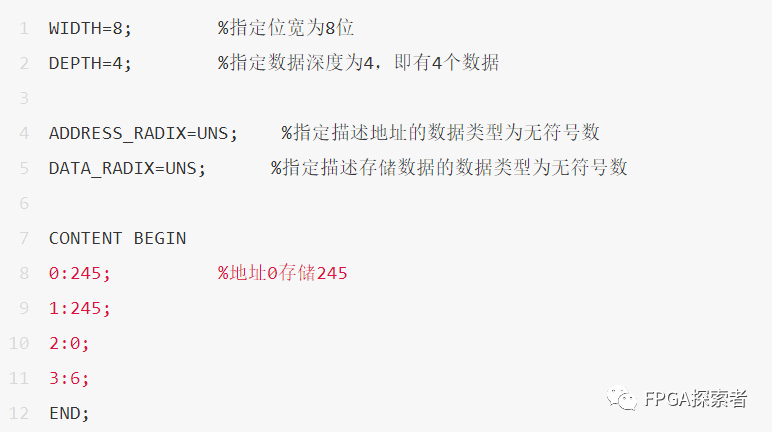

二、 ROM

ROM(Read-Only Memory)是只读存储器,用于存放不需修改的数据。

FPGA中的ROM主要有:

- 分布式ROM:使用LUT实现,容量很小。

- 块ROM:使用块RAM实现,容量较大。

ROM在配置时写入数据之后数据不能修改。ROM主要用于存放程序代码等不变数据。

Verilog 代码示例

(* rom_style = "distributed" *) reg [7:0] dist_rom[0:31]; // 32 x 8 分布式ROM

(* rom_style = "block" *) reg [31:0] block_rom[0:2047]; // 2K x 32 块ROM

三、CAM

CAM(Content-Addressable Memory)是一种特殊类型的内存结构,也称为内容可寻址存储器,可以通过内容查找数据所在位置。

CAM主要应用:

- 网络查找:根据目的地址查找路由端口。

- 缓存查询:根据TAG查询缓存中是否存在数据。

CAM的工作原理:

基于硬件电路的快速匹配,当输入一串数据时,CAM会同时比较这串数据与内部存储的所有数据项。如果找到完全匹配的数据项,CAM就会输出该数据项的地址。

CAM的优点:高速查找、精确匹配、并行处理。

CAM的缺点:容量受限、功耗较高、价格昂贵。

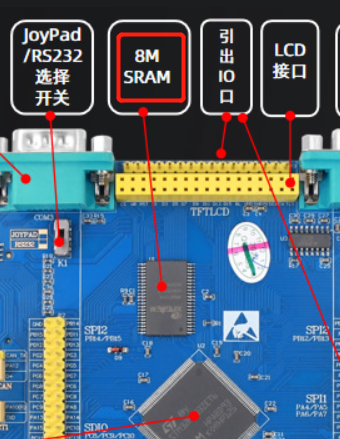

四、SRAM

SRAM(Static RAM)是一种常用的随机访问存储器(RAM)类型,它以静态方式存储数据,不需要定期刷新。也称为静态随机存储器。

SRAM在速度和功率消耗方面表现优异,但是容量较小,成本较高。

SRAM通常用于存储CPU或FPGA内部的寄存器、缓存或临时变量等。

SRAM主要由存储单元阵列、地址解码器和读写控制电路等组成。每个存储单元都包含一个双口RAM,可以独立地进行读/写操作。每个RAM有两位,即一个存储单元可以存储一个比特(bit)的数据。

SRAM还可以实现预读取功能,即在读取数据的同时,预读下一个数据,从而提高访问速度。此外,SRAM还可以实现双端口访问,即同时对两个不同的存储单元进行读写操作。

Verilog 代码示例

sram_controller sram_inst (

.clk (clk),

.addr (addr),

.dout (dout),

.din (din),

.we (we),

.ce (ce),

.oe (oe)

);

五、 DRAM

全称动态随机存取存储器(Dynamic Random Access Memory),是一种用于存储和访问大规模数据的主要存储器技术。

DRAM以其高密度、容量大和低功耗等特点,以Gigabit(Gb)为单位提供大容量存储,在FPGA中得到广泛的应用,比如常见的DDR3、DDR4等等。

FPGA的DRAM可以使用不同的接口标准,如DDR3、DDR4、LPDDR、HBM等。这些接口标准定义了DRAM与其他系统组件(如处理器、其他存储器、外设等)之间的通信协议和物理连接。

相比SRAM,DRAM拥有更大的容量,顺序读写速度快,随机读写速度慢。

Verilog 代码示例

ddr3_controller ddr3_inst(

.clk (clk),

.reset_n (reset_n),

.s_axi_awid (s_axi_awid),

.s_axi_awaddr (s_axi_awaddr),

.s_axi_awlen (s_axi_awlen),

.s_axi_awsize (s_axi_awsize),

.s_axi_awburst (s_axi_awburst),

.s_axi_awlock (s_axi_awlock),

.s_axi_awcache (s_axi_awcache),

.s_axi_awprot (s_axi_awprot),

.s_axi_awvalid (s_axi_awvalid),

.s_axi_awready (s_axi_awready),

// Write data channel

.s_axi_wdata (s_axi_wdata),

.s_axi_wstrb (s_axi_wstrb),

.s_axi_wlast (s_axi_wlast),

.s_axi_wvalid (s_axi_wvalid),

.s_axi_wready (s_axi_wready)

);

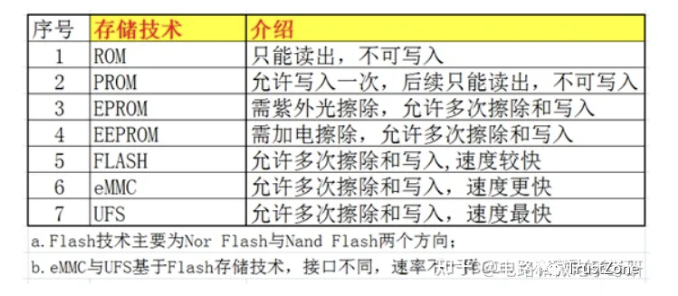

六、FLASH

FLASH是一种非易失存储器,断电后保持数据,容量小,但成本低廉。

FPGA中的FLASH主要用于:

- 存储配置文件:许多FPGA使用FLASH来保存配置文件。

- 程序存储:用于存储代码和数据。

FLASH存储器以块为单位进行擦除和写入操作。擦除操作需要将整个块中的数据清除,而写入操作只需修改需要更新的部分数据。

写入操作通常采用位编程(bit programming)的方式进行。在位编程中,根据需要将存储单元的电荷状态改变,以表示0或1的值。

与其他存储器类型相比,FLASH存储器的读取延迟较高,而擦除和写入操作的速度也相对较慢。此外,FLASH存储器的擦写次数有限,通常在百万到数十亿之间。

Verilog 代码示例

flash_controller flash_inst(

.clk(clk),

.flash_cs(flash_cs),

.flash_clk(flash_clk),

.flash_io(flash_io),

.addr(addr),

.dout(dout),

.din(din),

.oe(oe),

.we(we)

);

七、总结

FPGA提供了多种内部和外部的存储器解决方案,根据需要可以灵活使用,构建存储器系统。合理利用各类存储器的优缺点,可以在成本、容量和速度上取得最佳平衡。

电子发烧友App

电子发烧友App

评论