虽然栅极间距(GP)和鳍片间距(FP)的微缩持续为FinFET平台带来更高的性能和更低的功耗,但在5nm及更先进节点上,兼顾寄生电容电阻的控制和实现更高的晶体管性能变得更具挑战。 泛林集团

2022-05-07 14:10:15 7090

7090

SRAM工艺FPGA的加密技术

2012-08-13 17:08:03

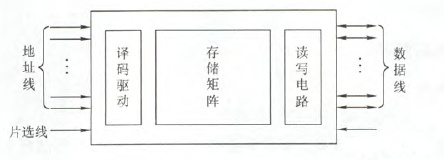

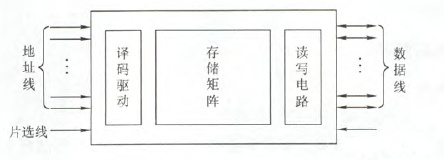

引起的功耗。 SRAM的功耗包括动态功耗(数据读写时的功耗)和静态功耗(数据保持时的功耗)。图1 给出了一个用来分析SRAM功耗来源的结构模型,在这个模型中,将SRAM的功耗来源分成三部分:存储阵列、行(列

2020-05-18 17:37:24

SRAM的性能及结构

2020-12-29 07:52:53

SRAM存储器可兼容IS61WV25616EDBLL-8BLI的参考:英尚微推荐一款国产SRAM芯片EMI504HL08WM-55I,由EMI先进的全CMOS工艺技术制造。支持工业温度范围和芯片级封装

2021-12-03 08:17:27

先进MCU的新低功耗模式低功耗MCU的要求会随着应用以及应用中使用MCU的方式的不同而有所变化。例如,在电池供电的恒温器应用中,低功耗主要由器件能够驱动LCD显示屏的最低功耗模式定义,在这种情况下

2012-08-27 15:41:15

功耗成为HPC和Networking的关键设计挑战

2021-05-21 06:32:23

如何降低芯片功耗目前已经成为半导体产业的热点问题。过去,对于集成器件制造商(IDM)来说,最直接的作法就是通过先进的制程工艺和材料比如低K介质来解决,低功率设计可以通过将自己设计团队的技能和经验进行

2019-06-27 08:05:18

本文以MP3解码器为例,介绍了一种在嵌入式Linux系统下配置使用处理器片内SRAM的应用方案,有效提高了代码的解码效率,降低了执行功耗。该方案不论在性能还是成本上都得到了很大改善。

2020-03-05 07:01:34

当我们使用的电脑运行过程中比较卡的时候,可以通过给电脑加装内存条来改善电脑的性能。我们可以给单片机外加和内存条效果一样的SRAM芯片来提升单片机的性能。下面宇芯电子以STM32单片机来讲解一下来扩展

2020-05-07 15:58:41

,组织结构为512K*16的高速率低功耗静态随机存储器。IS62WV51216高性能CMOS工艺制造。高度可靠的工.

2022-02-11 06:39:36

xilinxaltera 等基本都需要外置SRAM,是因为成本的愿意吗?但是国产的比如高云FPGA一般都是内置SRAM?这样是否性能会更好?

2019-05-06 11:34:21

上海需要20名SRAM 版图工程师:报价丰厚,全国各地都可以参加远程面试1. 1年以上SRAM版图设计相关经验2. 熟悉SRAM版图设计,包括SRAM/TCAM/ROM等,了解半导体工艺制程和器件

2021-08-30 13:11:14

完全解决的。这些挑战包括:多于10万个器件的设计复杂度、大于几GHz的时钟主频、纳米级的CMOS工艺技术、低功耗、工艺变化、非常明显的非线性效应、极度复杂的噪声环境以及无线/有线通讯协议的支持问题。

2019-10-11 06:39:24

要解决一系列的技术难题。为此,我们邀请FPGA企业、EDA企业、IP企业、芯片制造企业共同探讨新工艺技术的研发关键点。 Altera技术经理相奇博士:40纳米技术应对高静态功耗和高速I/O挑战

2019-05-20 05:00:10

近几年随着电子产品的发展,我们注意到一个很重要的趋势,每一代的设备的尺寸越来越小,在保持性能不变的情况下或者是性能更高级的情况下,设备的尺寸有着越来越小的趋势化,也有可能是因为现有的电子元件越来越小

2017-12-04 11:04:58

更换电池期间保持时间。带有电容或电池的Vbat还有助于消除由停电引起的恼人闪光。在高度关注功耗的环境下,低功耗MCU的发展促生了极具灵活性的通用MCU。工艺技术和设计技术的进步使16位MCU的工作电流可

2014-09-02 15:51:28

市场上已有的解决方案,以降低开发成本。在当今对成本和功耗都非常敏感的“绿色”环境下,对于高技术企业,两种挑战都有什么影响呢?第一种挑战意味着开发全新的产品,其功能是独一无二的,具有较低的价格以及较低

2019-08-09 07:41:27

端口六管CMOS SRAM单元 两端口 SRAM随着工艺尺寸的不断降低,参数波动变得越来越严重,六管SRAM存储单元固有的缺点(见下文)导致其在低电压情况下难以提供足够的稳定性,于是出现了一种 8 管

2020-07-09 14:38:57

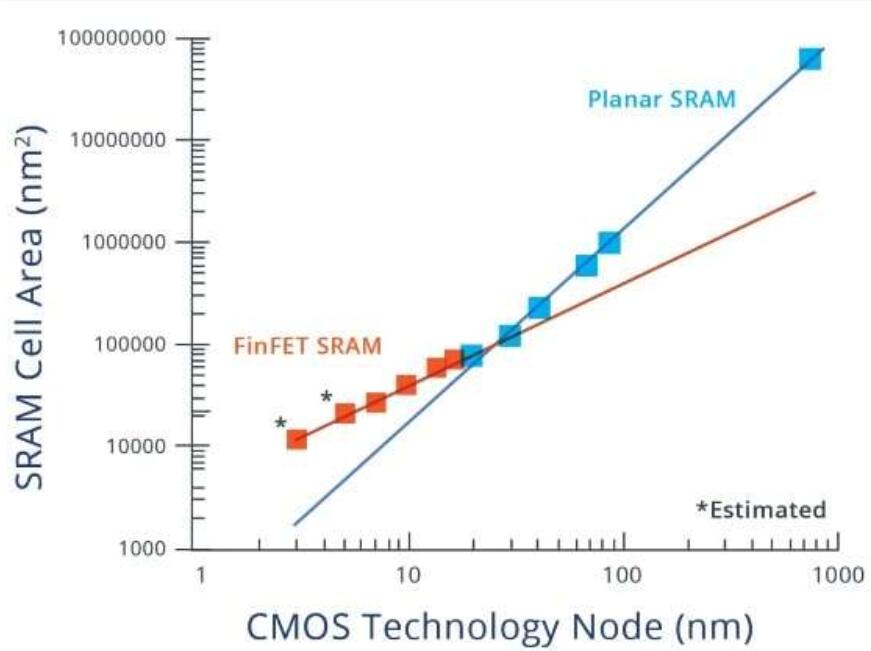

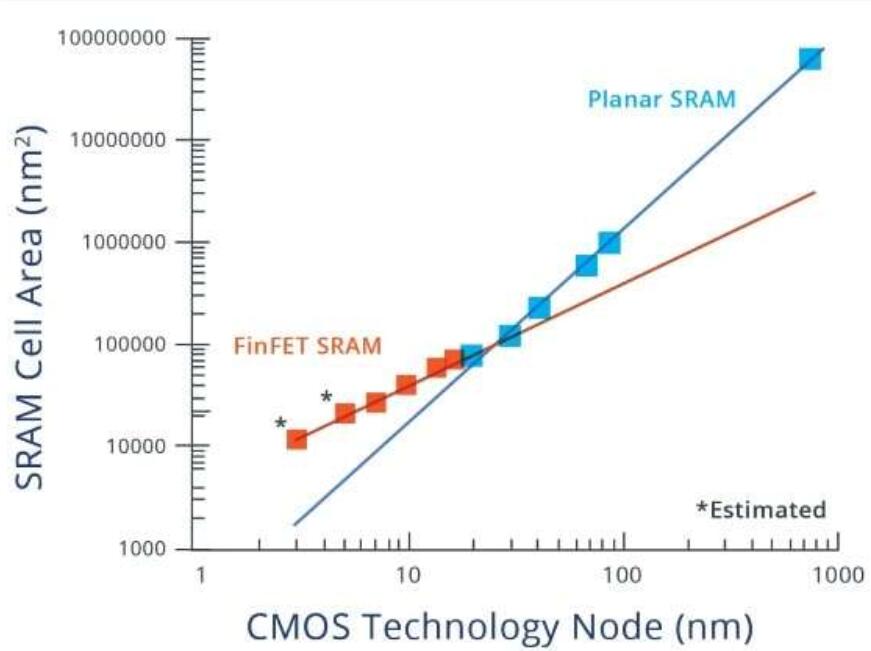

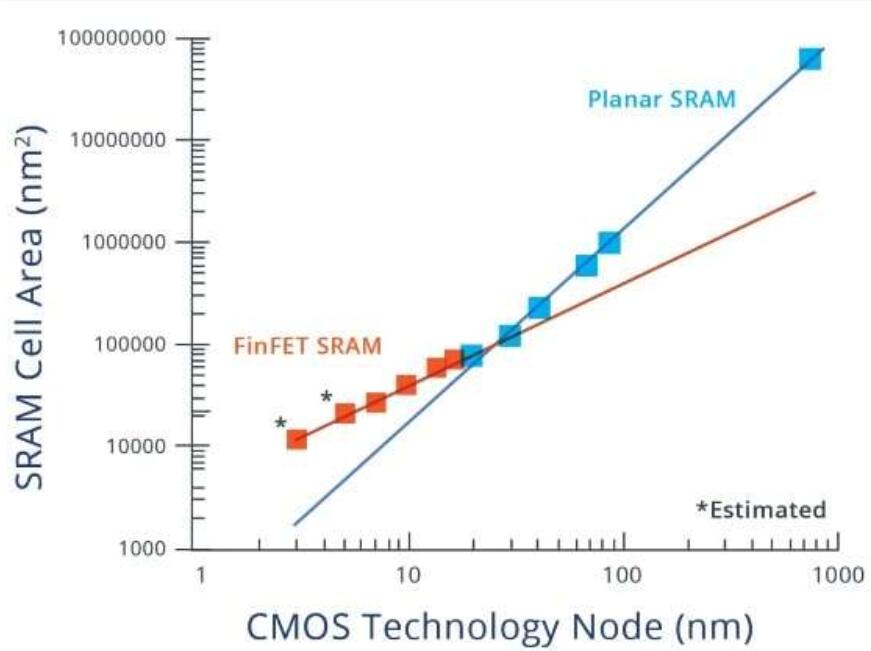

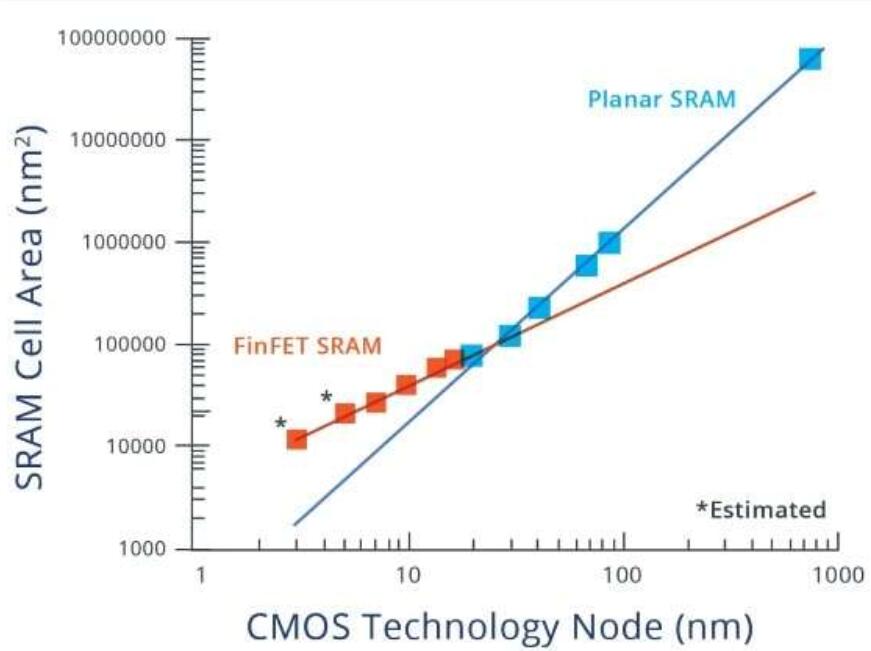

,为了提供足够的数据缓存能力,随着集成电路制造工艺的发展,嵌入式SRAM 的存储单元的面积也在以约0.5 倍每代的速度减小,在45 nm 工艺节点嵌入式SRAM 的密度已可以达到150 Mb/cm2。双

2020-07-06 16:26:25

在异步SRAM中实现速度与功耗的完美平衡

2021-02-02 07:48:11

仅仅优化了单元读、写一方面的性能,另一方面保持不变或者有恶化的趋势;单端读写单元往往恶化了读写速度,并使灵敏放大器的设计面临挑战;辅助电路的设计,往往会使SRAM的设计复杂化。 为了使SRAM存储单元

2020-04-01 14:32:04

从工艺选择到设计直至投产,设计人员关注的重点是以尽可能低的功耗获得最佳性能。Altera在功耗和性能上的不断创新,那其28nm高端FPGA如何实现功耗和性能的平衡?具体有何优势?

2019-09-17 08:18:19

提升SRAM性能的传统方法

2021-01-08 07:41:27

采用SRAM工艺的FPGA芯片的的配置方法有哪几种?用单片机实现SRAM工艺FPGA的加密应用

2021-04-08 06:04:32

随着设备尺寸的缩小,工程师正在寻找缩小DCDC电源设计解决方案的方法。如何缩小电源芯片设计并解决由此产生的热性能挑战?

2021-09-29 10:38:37

如何采用创新降耗技术应对FPGA静态和动态功耗的挑战?

2021-04-30 07:00:17

实现超低功耗蓝牙设计面临的主要挑战是什么?

2021-05-19 06:39:34

近几年随着电子产品的发展,我们注意到一个很重要的趋势,每一代的设备的尺寸越来越小,在保持性能不变的情况下或者是性能更高级的情况下,设备的尺寸有着越来越小的趋势化,也有可能是因为现有的电子元件越来越小

2017-10-19 10:51:42

高线性性能的评估和实现挑战

2021-04-06 07:10:32

随着FPGA的容量、性能以及可靠性的提高及其在消费电子、汽车电子等领域的大规模应用,FPGA设计的安全性问题越来越引起人们的关注。相比其他工艺FPGA而言,处于主流地位的SRAM工艺FPGA有一些

2019-08-23 06:45:21

功耗技术、可选内核电压 以及优化的芯片工艺,Stratix III器件的功耗得到大幅度降低,从而成为业界最低功耗的高性能FPGA。图5:ADI的超低功耗PulSAR ADC具有众多优点ADI医疗仪器

2009-09-17 14:52:33

晶体管密度的增加而缩小,SRAM区域更容易因工艺变化出现缺陷。这些缺陷将降低处理器芯片的总成品率。更高的功耗: 如果SRAM的位单元必需与逻辑位单元的大小相同,那么SRAM的晶体管就必须小于逻辑晶体管

2016-10-29 14:24:24

本文以MP3解码器为例,介绍了一种在嵌入式Linux系统下配置使用处理器片内SRAM的应用方案,有效提高了代码的解码效率,降低了执行功耗。该方案不论在性能还是成本上都得到了很大改善。

2021-04-26 07:01:55

不同特征尺寸的MOS晶体管,计算了由这些晶体管组成的静态随机存储器(SRAM)单粒子翻转的临界电荷Qcrit、LET阈值(LETth),建立了LETth与临界电荷之间的解析关系,研究了特征工艺尺寸

2010-04-22 11:50:00

美等发达国家的先进技术和工艺销售、安装于一体的大规模企业之一。汇集国内物流设备制造业众多技术精英,所拥有的工艺装备、技术、研发能力均居国内领先水平。凭借专业的制作经验、领先的制作技术、优秀的产品质量

2009-11-11 10:39:17

美等发达国家的先进技术和工艺销售、安装于一体的大规模企业之一。汇集国内物流设备制造业众多技术精英,所拥有的工艺装备、技术、研发能力均居国内领先水平。凭借专业的制作经验、领先的制作技术、优秀的产品质量

2009-11-12 10:23:26

美等发达国家的先进技术和工艺销售、安装于一体的大规模企业之一。汇集国内物流设备制造业众多技术精英,所拥有的工艺装备、技术、研发能力均居国内领先水平。凭借专业的制作经验、领先的制作技术、优秀的产品质量

2009-11-13 10:20:08

采用SRAM工艺的FPGA芯片的的配置方法有哪几种?如何对SRAM工艺FPGA进行有效加密?如何利用单片机对SRAM工艺的FPGA进行加密?怎么用E2PROM工艺的CPLD实现FPGA加密?

2021-04-13 06:02:13

请问如何应对功耗挑战?

2021-06-18 06:47:35

金属材料的工艺性能和切削加工性能的介绍:http://www.gooxian.com/ 1.金属材料的工艺性能 (1)铸造性能铸造性是指浇注铸件时,材料能充满比较复杂的铸型并获得优质铸件的能力

2017-08-25 09:36:21

一种新型绝热SRAM,从而可以以全绝热方式有效恢复在字线、写位线、敏感放大线及地址译码器上的大开关电容的电荷.最后,在采用TSMC0.25μmCMOS工艺器件参数情况下,对所设计的绝热SRAM 进行

2009-08-08 09:48:05

静态随机存储SRAM工艺

2020-12-29 07:26:02

SRAM两大问题挑战

2021-02-25 07:17:51

在研究移动电视技术发展趋势时需要区分产品功能组合、封装、性能、采用的半导体工艺和最重要的射频接收器性能。目前大多数单制式解调器都采用130纳米至65纳米CMOS工艺制造。多数情况下,它们与射频接收器

2019-07-29 06:49:39

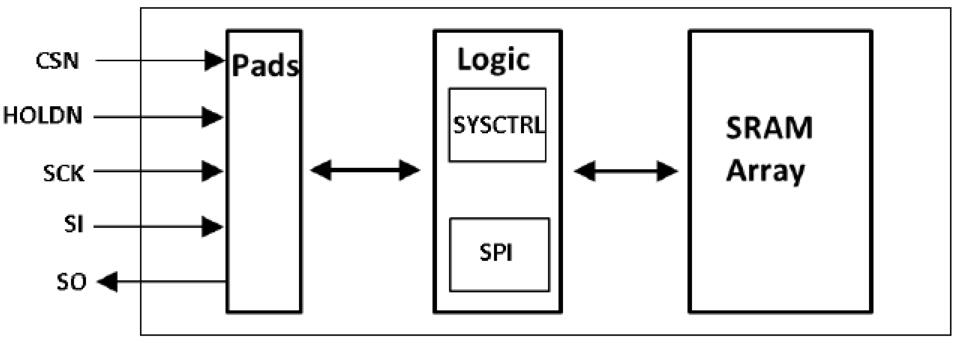

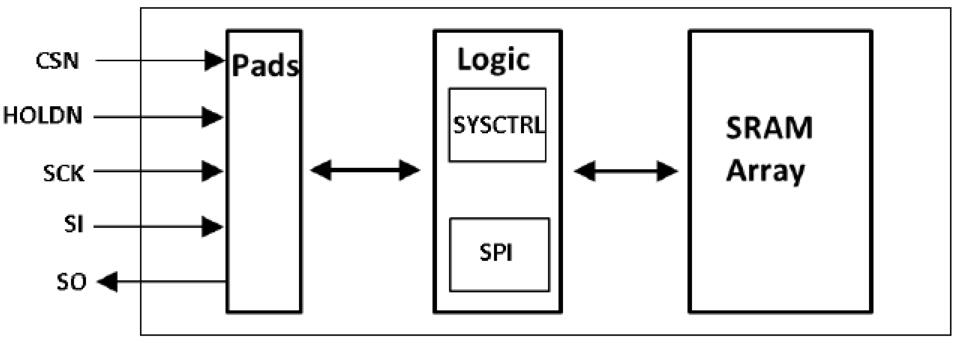

首先对采用SRAM工艺的FPGA 的保密性和加密方法进行原理分析,然后提出一种实用的采用单片机产生长伪随机码实现加密的方法, 并详细介绍具体的电路和程序。

2009-04-16 09:43:06 24

24 在现代电子系统设计中,由于可编程逻辑器件的卓越性能、灵活方便的可升级特性,而得到了广泛的应用。由于大规模高密度可编程逻辑器件多采用SRAM 工艺,要求每次上电,对FP

2010-07-17 16:28:02 8

8

STC高性能SRAM选型指南

型号 容量 工作电压 温度 速度 封装

2010-09-24 11:33:06 0

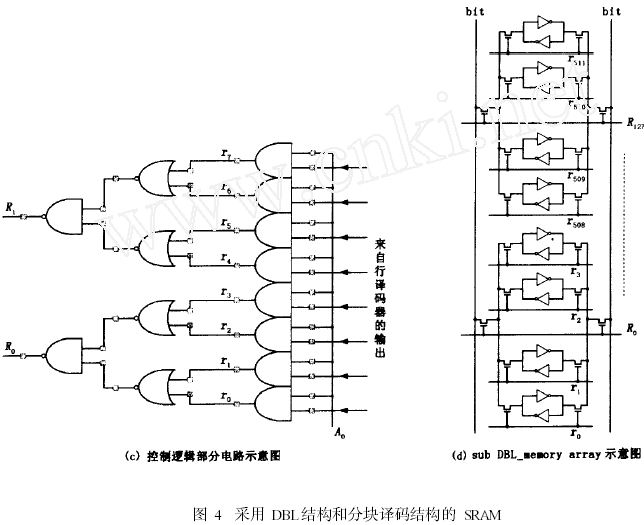

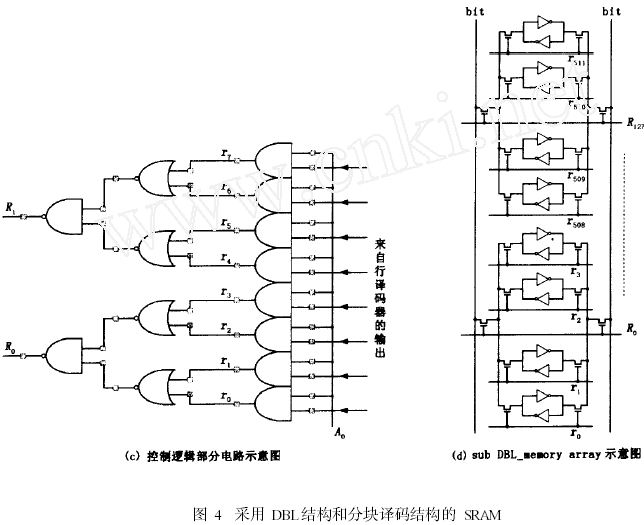

0 基于DBL结构的嵌入式64kb SRAM的低功耗设计

针对嵌入式系统的低功耗要求,采用位线分割结构和存储阵列分块译码结构,完成了64 kb低功耗SRAM模块的设计。 与一般布局的

2010-01-12 10:03:47 996

996

东芝在“2010 Symposium on VLSITechnology”上,发布了采用09年开始量产的40nm工艺SoC的低电压SRAM技术。该技术为主要用于便携产品及消费类产品的低功耗工艺技术。通过控制晶体管阈值

2010-06-21 10:54:42 928

928

在现代电子系统设计中,由于可编程逻辑器件的卓越性能、灵活方便的可升级特性,而得到了广泛的应用。由于大规模高密度可编程逻辑器件多采用SRAM工艺,要求每次上电,对FPGA器

2010-08-02 11:11:42 1626

1626

SRAM(Static Random Access Memory),即静态随机存取存储器。它是一种具有静止存取功能的内存,不需要刷新电路即能保存它内部存储的数据。SRAM的优点是较高的性能、功耗低,缺点是集成度低。

2017-09-01 17:26:23 3

3 异步SRAM产品分为快速与低功耗两个极为不同的产品类型,每个系列都具有其自己的一系列特性、应用和价格。快速异步SRAM具有更快的存取速度,但功耗较高;低功耗SRAM功耗低,但存取速度慢。 从技术角度

2017-10-16 11:11:38 0

0 SRAM不需要刷新电路即能保存它内部存储的数据。而DRAM(Dynamic Random Access Memory)每隔一段时间,要刷新充电一次,否则内部的数据即会消失,因此SRAM具有较高的性能,功耗较小。

2017-11-03 16:11:12 11292

11292 如何降低芯片功耗目前已经成为半导体产业的热点问题。过去,对于集成器件制造商(IDM)来说,最直接的作法就是通过先进的制程工艺和材料比如低K介质来解决,低功率设计可以通过将自己设计团队的技能和经验进行

2017-11-23 06:52:28 148

148 SRAM不需要刷新电路即能保存它内部存储的数据。而DRAM(Dynamic Random Access Memory)每隔一段时间,要刷新充电一次,否则内部的数据即会消失,因此SRAM具有较高的性能

2018-05-30 07:18:00 19573

19573

SRAM具有较高的性能,但是SRAM也有它的缺点,即它的集成度较低,功耗较DRAM大,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积。同样面积的硅片可以做出更大容量的DRAM,因此SRAM显得更贵。

2019-12-17 07:06:00 2514

2514

先进的制程工艺提升对于 CPU 性能提升影响明显。工艺提升带来的作用有频率提升以及架构优化两个方面。一方面,工艺的提升与频率紧密相连,使得芯片主频得以提升;

2019-10-01 17:06:00 6983

6983

仅仅优化了单元读、写一方面的性能,另一方面保持不变或者有恶化的趋势;单端读写单元往往恶化了读写速度,并使灵敏放大器的设计面临挑战;辅助电路的设计,往往会使SRAM的设计复杂化。 为了使SRAM存储单元的性能得到整体的提升,本文提出了读写裕度同

2020-04-03 15:47:15 1808

1808 ,组织为1M字乘16位。它是使用ISSI的高性能CMOS技术制造的。这种高度可靠的工艺加上创新的电路设计技术,可生产出高性能和低功耗的设备。 IS62WV102416DALL/DBLL

2020-05-28 15:30:26 942

942 当今世界环境保护已蔚然成风,力求节约能源,因此强烈要求电子系统低功耗化和低电压化。而且由于制造SRAM的半导体工艺精细化,SRAM要求低电压供电。因而近年来研究低电压供电技术活动十分活跃。在高速

2020-05-27 15:40:27 803

803 ISSI生产的32Mb高速低功耗异步SRAM,这种创新的设计加强了ISSI对具有最高质量和性能的SRAM的长期承诺。32MbSRAM在汽车A3温度范围(-40C至+ 125C)下提供12ns的访问

2020-05-28 15:35:18 1247

1247 或更快的速度工作。静态ram中所谓的静态,是指这种存储器只要保持通电,里面储存的数据就可以恒常保持。SRAM不需要刷新电路即能保存它内部存储的数据。 因此SRAM具有较高的性能,SoC随着工艺进步设计复杂度增加,embeded sram也越来越多。在40nm SoC产品Sram一

2020-06-29 15:40:12 12384

12384

SRAM不需要刷新电路即能保存它内部存储的数据。SRAM存储器具有较高的性能,但是SRAM芯片也有它的缺点,即它的集成度较低,功耗较DRAM大。SRAM的速度快但昂贵,一般用小容量的SRAM作为更高

2020-07-16 14:07:44 5284

5284

SRAM是可在任何CMOS工艺中免费获得的存储器。自CMOS诞生以来,SRAM一直是任何新CMOS工艺的开发和生产制造的技术驱动力。利用最新的所谓的深度学习领域专用域结构(DSA),每个芯片

2020-07-30 16:32:30 774

774

一代又一代的半导体晶圆工艺提升使不断增加的IC设计密度、性能提升和功耗节省得以实现,但也为电路设计工程师带来了许多新兴的挑战。包括创新的工艺特性,诸如FinFET晶体管等代表着向低功耗设计模式的转变,这就需要EDA软件在性能和精度方面也要有相应的飞跃提升。

2020-09-08 14:06:38 3774

3774 在过去的几十年中,SRAM领域已划分为两个不同的产品系列-快速和低功耗,每个产品都有自己的功能,应用程序和价格。使用SRAM的设备需要它的高速性或低功耗性,但不能同时兼顾两者。但是人们越来越需要具有

2020-09-24 16:23:23 468

468 昨天凌晨,iPhone 12、iPhone 12 mini、iPhone 12 Pro、iPhone 12 Pro Max正式发布。它们搭载了与之前新iPad Air相同的A14仿生处理器,该处理器基于5nm工艺制程打造。采用了六核心设计,性能比A13处理器提升了13%,并且功耗降低30%。

2020-10-15 10:33:00 1408

1408 随着诸如医疗电子和无线传感节点等应用的兴起,低功耗芯片受到了越来越广泛的关注。这类芯片对性能和功耗要求苛刻。静态随机存储器(SRAM)作为芯片的重要组成部分,大程度上影响着芯片的面积和功耗,因此

2020-12-02 16:29:37 739

739 计算 (HPC) 应用,对PPA提出更高要求,驱动着开发者们不断挑战物理极限。 追求更优PPA 随着功耗和性能指标不断变化,先进工艺节点下的芯片设计需要考虑更多变量。动态或翻转功耗已经成为功耗优化的重点。尽管降低工作电压可以直接降

2021-05-06 11:12:01 1765

1765 低功耗SRAM存储器应用于内有电池供电对功耗非常敏感的产品,是静态随机访问存储器的一种类别,静态随机访问存储器(SRAM)作为最重要的半导体存储器,广泛地嵌入于高性能微处理器。随着集成电路制造工艺

2021-06-08 16:49:32 1943

1943 静态存储SRAM芯片包含业界多样的异步低功耗SRAM。而带有ECC的异步SRAM适用于各种要求最高可靠性和性能标准的工业,医疗,商业,汽车和军事应用。快速SRAM是诸如交换机和路由器,IP电话,测试设备和汽车电子产品之类的网络应用的理想选择。

2021-10-11 16:33:11 12563

12563 低功耗SRAM存储器应用于内有电池供电对功耗非常敏感的产品,作为静态随机访问存储器的一种类别,静态随机访问存储器(SRAM)作为最重要的半导体存储器,广泛地嵌入于高性能微处理器。随着集成电路制造工艺

2021-12-21 16:34:39 1150

1150 IS62WV51216EBLL-45TLI SRAM芯片是一个8M容量,组织结构为512K*16的高速率低功耗静态随机存储器。 采用高性能CMOS工艺制造。高度可靠的工艺水准再加创新的电路设计技术

2022-01-26 14:39:57 1636

1636 当前有两个不同系列的异步SRAM:快速SRAM(支持高速存取)和低功耗SRAM(低功耗)。从技术角度看来,这种权衡是合理的。在低功耗SRAM中,通...

2022-02-07 12:37:56 2

2 虽然栅极间距(GP)和鳍片间距(FP)的微缩持续为FinFET平台带来更高的性能和更低的功耗,但在5nm及更先进节点上,兼顾寄生电容电阻的控制和实现更高的晶体管性能变得更具挑战。

2022-05-27 17:24:13 6

6 以已经宣布量产的三星3nm为例,三星官方消息显示,与三星5nm工艺相比,第一代3nm工艺可以使功耗降低45%,性能提升23%,芯片面积减少16%;而未来第二代3nm工艺则使功耗降低50%,性能提升30%,芯片面积减少 35%。

2022-09-26 16:46:12 883

883 看索尔维如何突破创新,迎“难”而上 出于物理极限和制造成本的原因,先进工艺技术让芯片的体积不断突破想象,从5纳米到3纳米,甚至2纳米时,有如半导体行业灯塔般的“摩尔定律”已然失效。 工业界已达成新的共识:在功耗、性能、

2022-10-24 17:54:34 647

647

平面到FinFET的过渡对SRAM单元的布局效率有重大影响。使用FinFET逐渐缩小关键节距已导致SRAM单元尺寸的迅速减小。鉴于对更大的片上SRAM容量的需求不断增长,这样做的时机不会更糟。离SRAM将主导DSA处理器大小的局面并不遥远。

2022-11-24 16:07:13 730

730

台积电在今年早些时候正式推出其 N3 制造技术时表示,与其 N5(5 纳米级)工艺相比,新节点的逻辑密度将提高 1.6 倍和 1.7 倍。它没有透露的是,与 N5 相比,新技术的 SRAM 单元几乎无法缩放。

2022-12-22 12:28:42 1034

1034 EMI Serial SRAM是为串行接口的SRAM,外扩SRAM可以通过使用SPI的接口来将外部RAM添加到几乎所有应用中。串行访问的静态随机存取存储器采用先进的CMOS技术进行设计和制造,以提供高速性能和低功耗。

2023-04-27 17:37:44 645

645

电子发烧友网站提供《优化EEG放大器的性能并降低功耗的设计挑战.pdf》资料免费下载

2023-11-28 11:40:16 0

0 随着半导体技术的不断发展,封装工艺也面临着一系列挑战。本文将探讨其中一个重要的挑战,并提出一种化解该挑战的工艺方法。

2023-12-11 14:53:37 194

194

电子发烧友App

电子发烧友App

评论