8位寄存器在16位寄存器中,而16位寄存器在32位寄存器中。

2022-09-19 10:10:11 2746

2746 ;/**1.传送value高8位*******DATA= (uchar)(value>>8) ;*******************************寄存器ODR操作方式

2015-07-30 22:29:36

目录STM32中串口通信的基本操作USART_SR状态寄存器比较常用的位操纵该寄存器的函数USART_DR数据寄存器DR寄存器的操作流程操作DR寄存器的函数USART_BRR波特率寄存器操作BRR

2021-08-16 08:54:56

可能很多朋友对GPIO_TypeDef里的各个寄存器还不太了解,更会疑惑为何有了ODR,还要使用BSRR和BRR,下面我就我的认识,做一下简单的说明ODR寄存器可读可写:既能控制管脚为高电平,也能

2022-01-05 06:34:52

STM32BSRR寄存器和BRR寄存器是32位的。置GPIOA->BSRR低16位的某位为’1’,则对应的I/O端口管脚置’1’;置GPIOA->BSRR低16位的某位为

2022-01-05 07:36:22

。每个IO口都由7个寄存器来控制,分别是:配置模式的两个32位的端口配置寄存器CRL和CRH;两个32位的数据寄存器IDR和ODR;1个32位的置位/复位寄存器BSRR;1个16位的复位寄存器BRR;1个32位的锁存寄存器LCKR;常用的IO口寄

2022-01-18 07:31:09

一、查找寄存器地址STM32给不同的寄存器分配了不同的地址,在《STM32中文参考手册》中查找地址。找到GPIOX端口的起始地址寄存器名称 寄存器地址相对 GPIOA 基址的偏移

2021-12-10 08:19:42

【8-15】端口配置寄存器 32位IDR 数据寄存器 32位 输入ODR 数据寄存器 32位 输出BSRR 置位/复位寄存器 32位BRR 复位寄存器 16位LCKR 锁存寄存器 32位3、常用的IO端口寄存器 CRL CRH IDR ODR4、CRL ...

2022-02-28 06:51:38

STM32F103GPIO功能描述每个GPI/O端口有两个32位配置寄存器(GPIOx_CRL,GPIOx_CRH),两个32位数据寄存器(GPIOx_IDR和GPIOx_ODR),一个32位置位

2021-08-04 09:19:52

昨天没有写,打球吃饭到很晚。今天把昨天没有完成的看了下。主要是STM32F107的端口和中断部分。结合键盘扫描的例程做了一些了解。端口GPIO寄存器主要有:1.GPIOx_CRL

2021-08-06 08:34:10

(GPIOA->BSRR, GPIO_BSRR_BS_5);// set output lowSET_BIT(GPIOA->BRR, GPIO_BRR_BR_5);....但这不起作用。我不确定我理解三个寄存器及其功能之间的区别。每个用例有哪些?哪一个适合我的要求?

2018-09-26 11:34:15

STM32串口寄存器库函数配置方法STM32常用寄存器和库函数串口配置一般步骤(串口实例)常用的串口相关寄存器:USART_SR状态寄存器USART_DR数据寄存器USART_BRR波特率寄存器

2022-02-22 06:22:43

STM32串口通信相关寄存器状态寄存器 (USART_SR)数据寄存器 (USART_DR)波特率寄存器 (USART_BRR)控制寄存器 x (USART_CRx)控制寄存器 1

2021-08-16 07:44:44

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档文章目录前言一、什么是寄存器?二、STM32寄存器映射1.总线基地址2.GPIO基地址3.GPIOB端口寄存器列表4.GPIOx端口数

2022-01-20 07:08:11

前面介绍了存储器映射、寄存器和寄存器映射,这些都是为了介绍使用 C语言封装寄存器做铺垫。这里我们通过一个实例来对 C 语言封装寄存器进行介绍。 具体实例:控制 GPIOC 端口的第 0 管脚输出一个

2017-11-24 10:33:09

是那么简单, 先看两张BSRR/BRR寄存器的图:据官方数据手册上面说, 这两个寄存器用于专门对ODR进行原子操作的位操作, 都是在置1的时候对某位有影响.举例说下怎么对IO端口赋值:1.对高8位/低8位

2020-05-26 08:00:00

GPIO寄存器一览GPIOx->CRL(x=A…E)GPIOx->CRH(x=A…E)GPIOx->IDR(x=A…E)GPIOx->ODR(x=A…E)GPIOx_BSRR

2022-01-05 07:52:27

这里就不说库函数操作了,因为库函数的本质是操作寄存器。当GPIO做为输出时,无非是输出0或者1。涉及到的寄存器有GPIOx_ODR、GPIO_BSRR、GPIO_BRR.下面分别介绍这三个寄存器

2013-10-07 15:51:33

写这篇文章的原因是发现net上很少有从STM32的寄存器的角度去解析其原理的文章,也许是太简单的缘故各位大哥都不愿意动笔。那么我来写下,尽量写得简单易懂,以此留个纪念。写得肯定不好或者有的地方不准

2021-08-19 08:53:01

寄存器(GPIOx_BSRR)4.一个16位复位寄存器(GPIOx_BRR)5.一个32位锁定寄存器(GPIOx_LCKR)这7个寄存器适当配置,可以控制一组GPIO的16个IO口。为什么16个IO口需要两个32位的配置寄存器呢?CRL/CRH每四个位控制一个IO口,GPIOx_C.

2022-01-05 06:44:20

包含7个寄存器。分别是- GPIOx_CRL:端口配置低寄存器- GPIOx_CRH:端口配置高寄存器- GPIOx_IDR:端口输入寄存器- GPIOx_ODR:端口输出寄存器GPIOx_BSRR:端口位设置/清除寄存器GPIOx_BRR:端口位清除寄存器GPIOx_L

2022-01-24 06:47:20

,GPIOx_IDR、GPIOx_ODR1个32位置位/复位寄存器,GPIOx_BSRR1个16位复位寄存器,GPIOx_BRR1个32位锁存寄存器,GPIOx_LCKR每个通用 IO(GPIO)端口的端口位,可由软件单独配置为以下8种模式:1、输入浮空,2、输入上拉,3、输入下拉,4、模拟输入,5、开漏

2021-08-05 06:11:56

- GPIOx_CRH:端口配置高寄存器- GPIOx_IDR:端口输入寄存器- GPIOx_ODR:端口输出寄存器- GPIOx_BSRR:端口位设置/清除寄存器- GPIOx_BRR :端口位清除寄存器

2021-08-24 07:52:12

功能STM32 的每个 IO 端口都有 7 个寄存器来控制。他们分别是:配置模式的 2 个 32 位的端口配置寄存器 CRL 和 CRH;2 个 32 位的数据寄存器 IDR 和 ODR;1 个 32 位的置位/复位寄存器BSRR;一个 16 位的复位寄存器 BRR;1 个 32 位的锁存寄存器

2022-02-22 08:08:16

模式)输入数据。⑥ 通过寄存器 GPIOx_BSRR 实现对寄存器 GPIOx_ODR 的位操作。⑦ 通过配置寄存器 GPIO

2021-08-10 06:29:54

= GPIOA->BSRR | 0x08;//BSRR端口位设置/复位寄存器elseGPIOA->ODR = GPIOA->BRR & ~0x08;// BRR端口位复位寄存器

2015-01-22 16:03:05

据寄存器(GPIOx_IDR和GPIOx_ODR)、一个32位置位/复位寄存器(GPIOx_BSRR)、一个16位复位寄存器(GPIOx_BRR)、一个32位锁定寄存器(GPIOx_LCKR)。(1

2020-03-26 14:42:19

STM32F4工程--IO口--GPIO寄存器详解 ----芯片:STM32F429IGT6----参考资料:正点原子视频一、基础知识1、每组IO口包含10个寄存器,如果配置一个IO口需要2个位

2022-01-18 06:53:40

STM32处理器的USB接口速度是多少?GPIOX_BSRR和GPIOX_BRR寄存器的目的是什么?

2021-11-01 07:34:19

STM32中控制GPIO状态的一共有7个寄存器,分别是CRL、CRH、IDR、ODR、BSRR、BRR、LCKR。调用即可看到选项

2021-07-01 08:13:51

1. GPIO相关寄存器1.1 配置寄存器(CRL、CRH)1.2 数据寄存器(IDR、ODR)1.3 位设置/清除寄存器(BSRR)1.4 锁定寄存器(LCKR)1.5 位清除寄存器(BRR)2.

2021-08-17 06:10:56

的数据寄存器(GPIOx_IDR、GPIOx_ODR)。3.一个32位的置位/复位寄存器(GPIOx_BSRR)。4.一个16位的复位寄存器(GPIOx_BRR)。5.一个16位的锁定寄存器(GPIOx_LOCK)。(一旦gpio端口锁定之后,再次复位gpio端口时,gpio端口的状态将不会改变)

2022-01-11 07:48:19

;BSRR0x100x40010800+0x10 GPIOA->BRR0x140x40010800+0x14 GPIOA->LCKR0x180x40010800+0x18 表4.6.3 GPIOA各寄存器实际地址表 我们

2016-04-17 11:51:00

功能寄存器。如用sfr P1 = 0x90这一句定义P1为P1端口在片内的寄存器。然后我们往地址为0x80的寄存器设值的方法是:P0=value; 那么在STM32中,是否也可以这样做呢??答案是肯定

2015-01-26 14:39:13

相关寄存器STM32F103 的每个 GPIO 端口有:两个 32 位配置寄存器(GPIOx_CRL 和GPIOx_CRH)、两个 32 位数据寄存器(GPIOx_IDR 和 GPIOx_ODR)、一

2022-08-31 17:46:16

相关寄存器STM32F103 的每个 GPIO 端口有:两个 32 位配置寄存器(GPIOx_CRL 和GPIOx_CRH)、两个 32 位数据寄存器(GPIOx_IDR 和 GPIOx_ODR)、一

2022-07-16 16:29:17

相关寄存器STM32F103 的每个 GPIO 端口有:两个 32 位配置寄存器(GPIOx_CRL 和GPIOx_CRH)、两个 32 位数据寄存器(GPIOx_IDR 和 GPIOx_ODR)、一

2022-06-01 19:04:33

发现BRR或者是BSRR中有置一的。怎么回事? void GPIO_SetBits(GPIO_TypeDef* GPIOx, uint16_t GPIO_Pin) { /* Check

2019-08-23 03:47:02

服务函数中使用同样的操作寄存器的方法和库函数的方法,问题依旧。

//GPIO_ResetBits(GPIOBGPIO_Pin_5);

GPIOB->BRR=GPIO_Pin_5

2023-10-20 08:09:27

仅供个人学习使用STM32 的每个 IO 端口都有 7 个寄存器来控制。他们分别是:配置模式的 2 个 32 位的端口配置寄存器 CRL 和 CRH;2 个 32 位的数据寄存器 IDR 和 ODR

2022-02-28 07:22:14

。 分别为 (1)配置模式的2个32位的端口配置寄存器 CRL 和 CRH; (2)2 个 32 位的数据寄存器 IDR 和 ODR; (3)1 个 32 位的置位/复位寄存器BSRR; (4)1个 16 位

2018-07-02 05:18:52

通用同步/同步收发器USART串口是由哪些部分组成的?如何从USART_BRR寄存器得到USARTDIV呢?

2021-12-10 06:57:43

用stm32 的配置GPIO 来控制LED 显示状态,可用ODR,BSRR,BRR 直接来控制引脚输出状态.ODR寄存器可读可写:既能控制管脚为高电平,也能控制管脚为低电平。管脚对于位写1 gpio

2021-12-09 06:54:41

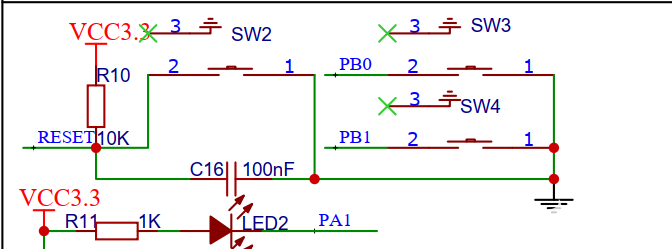

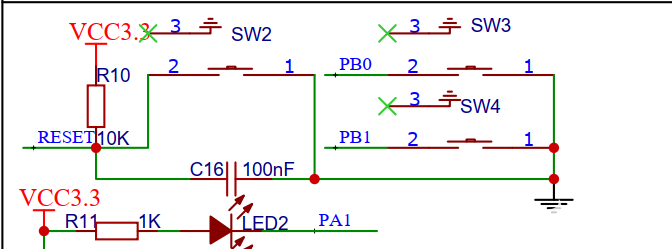

硬件:首先在硬件中我们看到了RGB灯的硬件电路图现在我们用寄存器的方法来操作这几个灯:1,先定义硬件的宏#defineGPIOB_CRL0x40010C00#define

2021-12-27 06:59:04

(GPIOx_BSRR) (x=A..G)寄存器32位,低16位控制ODR寄存器的值(BSRR低16位写1把ODR寄存器的位变为1,写0不影响ODR寄存器)总结:GPIOx_BSRR寄存器,低16位,写1引脚

2015-08-28 22:28:15

写入 USART_BRR 寄存器的这个值是多少?它是做什么用的?我不明白为什么要使用以下公式进行计算:fclock /(除数,在我的公式中是 5 * baudrate)例如,这是一个示例计算:我使

2022-12-27 06:24:09

请问STM32中GPIO的BSRR和BRR的清零有什么区别啊?还有GPIO的上拉和下拉用的是一个寄存器,是怎么区分?是通过ODR区分吗?写数据操作的时候是操作是通过ODR还是通过BSRR和BRR呢?还有RCC里PLLRDY和PLLON的区别是什么啊?。。。谢谢了!

2019-07-22 04:35:04

STM32通用IO 寄存器一、端口配置寄存器 CRH、CRL1、MODE2、CNF二、数据寄存器 ODR、IDR1、ODR2、IDR三、置位/复位寄存器 BSRR1、BSRR四、复位寄存器 BRR

2022-01-18 09:15:23

资料上复用输出不使用ODR寄存器,有点出入。 求解

2020-05-08 02:27:53

stm32标准例程-寄存器版本的源代码,57个实验例程,从跑马灯到操作系统,全方位学习stm32开发

2015-11-26 16:17:12 0

0 CSD寄存器解析,SD卡寄存器解说,值得学习。

2016-01-06 14:25:28 0

0 主要介绍STM32寄存器——外设驱动,图文详情,非常合适看

2016-02-22 15:46:19 0

0 STM32 GPIO寄存器ODR BSRR BRR详细介绍

2017-07-29 10:27:58 2

2 STM32的每个IO端口都有7个寄存器来控制。他们分别是:配置模式的2个32位的端口配置寄存器CRL和CRH;2个32位的数据寄存器IDR和ODR;1个32位的置位/复位寄存器BSRR;一个16

2017-11-25 09:52:46 3593

3593 STM32的每个GPIO端口都有两个特别的寄存器,GPIOx_BSRR和GPIOx_BRR寄存器,通过这两个寄存器可以直接对对应的GPIOx端口置1或置0。 GPIOx_BSRR的高16位中每一位

2017-11-26 11:50:22 1

1 寄存器 GPIOx->IDR,GPIOx->ODR

一个32位的 set/reset 寄存器 GPIOx->BSRR

一位16位的 reset 寄存器 GPIOx->BRR

一位32位的锁定寄存器 GPIOx->LCKR。

2018-01-11 09:03:19 12657

12657

ODR寄存器可读可写:既能控制管脚为高电平,也能控制管脚为低电平。

管脚对于位写1 gpio 管脚为高电平,写 0 为低电平

BSRR 只写寄存器:[color=Red]既能控制管脚

2018-11-01 15:45:20 7217

7217 每个GPIO端口有: 2个配置寄存器GPIOx_CRL, GPIOx_CRH(32位); 2个数据寄存器GPIOx_IDR, GPIOx_ODR(32位); 1个置位/复位寄存器GPIOx_BSRR(32位); 1个复位寄存器GPIOx_BRR(16位); 1个锁定寄存器GPIOx_LCKR(32位);

2019-05-16 18:07:00 0

0 (GPIOx_BSRR),一个16 位复位寄存器(GPIOx_BRR)和一个32 位锁定寄存器 (GPIOx_LCKR)。

2019-04-25 08:00:00 1

1 和输出寄存器GPIOx_IDR和GPIOx_ODR,1个32位置位复位寄存器GPIOx_BSRR,1个32位锁定寄存器GPIOx_LCKR和2个32位复用功能选择寄存器GPIOx_AFRH和GPIOx_AFRL。

2019-08-20 15:07:32 1727

1727

stm32每一个GPIO端口拥有2个32bits的configuration寄存器(GPIOx_CRL,GPIOx_CRH),2个32bits的数据寄存器(GPIOx_IDR,GPIOx_ODR

2019-11-01 16:28:19 11135

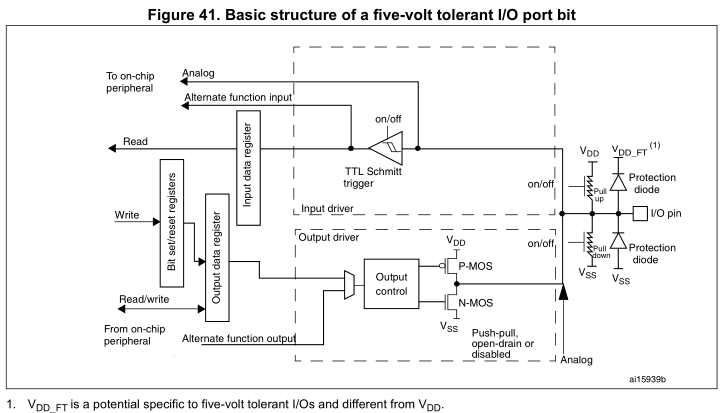

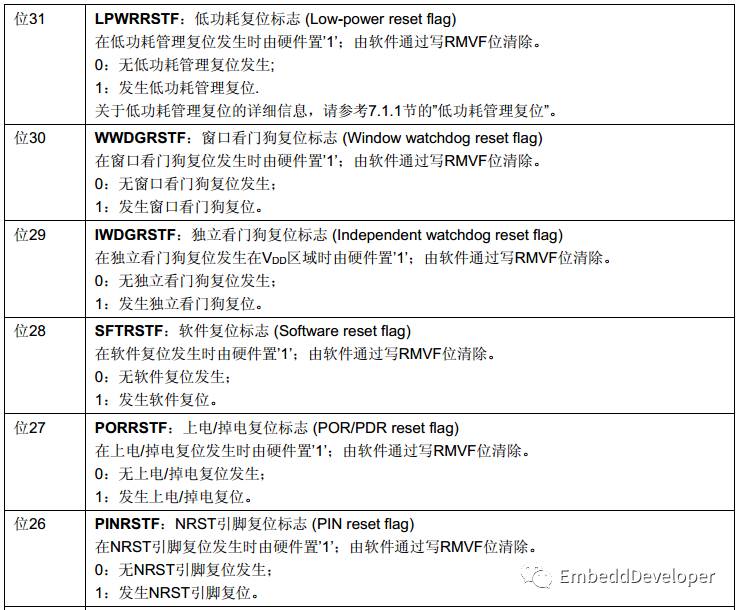

11135 一篇很简单,有必要了解的文章 - STM32复位来源(寄存器版)

2020-03-14 14:13:01 10124

10124

如下表新手看这个图 还是很懵的,CNF1/CNF0; MODE1/MODE0;PxODR寄存器这些是什么?答案是:控制I/O的寄存器。第二:STM32 I/O口寄存器STM32 每个I/O 都由7个寄存器控制:2个 32位的端口配置寄存器(CRL和CRH);2个32的数据存储(IDR和ODR);一个3

2021-11-15 12:51:04 17

17 用stm32 的配置GPIO 来控制LED 显示状态,可用ODRBSRRBRR 直接来控制引脚输出状态.ODR寄存器可读可写:既能控制管脚为高电平,也能控制管脚为低电平。管脚对于位写1 gpio

2021-11-26 11:21:05 76

76 IO 配置常用的 8 个寄存器: MODER、OTYPER、OSPEEDR、PUPDR、ODR、IDR 、AFRH 和 AFRL。MODER 寄存器(输入状态寄存器):STM32F4 最多

2021-11-29 13:51:03 10

10 口包含7个寄存器。分别是- GPIOx_CRL:端口配置低寄存器- GPIOx_CRH:端口配置高寄存器- GPIOx_IDR:端口输入寄存器- GPIOx_ODR:端口输出寄存器GPIOx_BSRR:端口位设置/清除寄存器GPIOx_BRR:端口位清除寄存器GPIOx_L

2021-11-29 13:51:04 14

14 ,OTYPER,OSPEEDR和PUPDR),2个32位数据寄存器(IDR和ODR),1个32位置位/复位寄存器(BSRR),1个32位锁定寄存器(LCKR)和2个32位复用功能选择寄存器(AFRH...

2021-11-29 14:21:07 10

10 。每个通用的I/O(GPIO)端口有 2个32位配置寄存器(GPIOx_CRL、GPIO_CRH) 2个32位数据寄存器(GPIOx_IDR、GPIO_ODR) 1个32位置位/复位寄存器(GPIOx_BSSR) 1个16位复位寄存器(GPIOx_BRR) 1个32

2021-12-03 09:51:06 9

9 一、实验原理(一)寄存器地址查找STM32给不同的寄存器分配了不同的地址在《STM32中文参考手册_V10》的第28页,有不同寄存器的地址范围。然后找到端口输入寄存器的地址偏移,这样就能找到对应端口

2021-12-07 10:06:14 2

2 一、实验原理(一)寄存器地址查找STM32给不同的寄存器分配了不同的地址在《STM32中文参考手册_V10》的第28页,有不同寄存器的地址范围。然后找到端口输入寄存器的地址偏移,这样就能找到对应端口

2021-12-07 10:21:04 8

8 ,GPIOx_IDR、GPIOx_ODR1个32位置位/复位寄存器,GPIOx_BSRR1个16位复位寄存器,GPIOx_BRR1个32位锁存寄存器,GPIOx_LCKR每个通用 IO(GPIO)端口的端口位,可由软件单独配置为以下8种模式:1、输入浮空,2、输入上拉,3、输入下拉,4、模拟输入,5、开漏

2021-12-07 11:51:05 0

0 ,一般高16位保留BSRR寄存器32位分为低16位BSRRL和高16位BSRRH,BSRRL配置一组IO口的16个IO口的状态(1),BSRRH配置复位状态(0)。每组GPIO端口的寄存器包括:4个32位配置寄存器一个端口模式寄存器(GPIOx_MODER)一个端口输出类型寄存器(GPIOx_.

2021-12-08 17:06:11 5

5 STM32F103点灯程序(寄存器)

2021-12-08 17:21:09 20

20 配置寄存器使STM32最小系统板上的LED灯点亮根据原理图,要使D2点亮,需要将PC13拉低,分为以下步骤:使能GPIO的时钟配置GPIO13为输出模式配置GPIO13输出低电平一、确定有关寄存器

2021-12-08 17:21:10 3

3 以我现在的水平还啥都不了解,所以这次主要说的就是通过USB串口和电脑通信**串口配置**:详细配置可以参考STM32开发指南寄存器版本的5.3.2章节,每个串口都有一个自己独立的波特率寄存器 USART_BRR,通过配置它就可以配置串口的波特率**串口时钟使能**:串口的

2021-12-08 17:36:10 0

0 STM32 第二天寄存器寄存器功能:寄存器的功能是存储二进制代码,它是由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位二进制代码,故存放n位二进制代码的寄存器,需用n个触发器来构成

2021-12-08 17:36:11 18

18 stm32是如何将配置从库函数调用一步一步到寄存器的?0. 前言1.综述1.1 流程2.正式开始2.1 LED库函数初始化2.2 GPIO_TypeDef2.3 GPIOA的访问方法2.4

2021-12-16 16:58:11 18

18 通过按位异或,写ODR寄存器,如:GPIOB->ODR ^= GPIO_Pin_5; //对PB5 IO口取反在官方给的固件库中,有#define GPIO_Pin_5

2021-12-24 19:35:35 4

4 STM32串口通信相关寄存器状态寄存器 (USART_SR)数据寄存器 (USART_DR)波特率寄存器 (USART_BRR)控制寄存器 x (USART_CRx)控制寄存器

2021-12-28 19:11:36 6

6 STM32串口寄存器库函数配置方法STM32常用寄存器和库函数串口配置一般步骤(串口实例)常用的串口相关寄存器:USART_SR状态寄存器USART_DR数据寄存器USART_BRR波特率寄存器

2021-12-28 19:13:59 7

7 本文基于STM32F407ZGT6,适用于M3/M4大部分内核的STM32芯片。——————————————————————————————STM32每个通用 I/O 端口包括 10个32位寄存器

2021-12-28 19:26:24 0

0 功能STM32 的每个 IO 端口都有 7 个寄存器来控制。他们分别是:配置模式的 2 个 32 位的端口配置寄存器 CRL 和 CRH;2 个 32 位的数据寄存器 IDR 和 ODR;1 个 32 位的置位/复位寄存器BSRR;一个 16 位的复位寄存器 BRR;1 个 32 位的锁存寄存器

2021-12-28 19:28:06 0

0 读值输出寄存器:ODR BSRR BRR输入寄存器:IDR(0 低电平)#define __I volatile #define __I volatile const #define __O

2022-01-13 10:16:40 1

1 STM32F03寄存器方式点亮LED流水灯文章目录STM32F03寄存器方式点亮LED流水灯一、题目内容二、STM32F03系列芯片的地址映射和寄存器映射映射原理;了解GPIO端口的初始化设置三步

2022-01-13 14:47:41 9

9 文章目录一、STM32F103系列芯片使用入门1.寄存器一、STM32F103系列芯片使用入门1.寄存器①概念 寄存器是中央处理器内的组成部分。寄存器是有限存贮容量的高速存贮部件,它们可用来暂存指令

2022-01-13 14:48:42 4

4 STM32的寄存器操作在使用STM32单片机编程时一般都用ST给的库函数编程,库函数编程的底层就是对单片机寄存器的操作,库函数就是一系列寄存器操作的封装。一般来说ST给的库函数足以满足项目所需的各种

2022-01-13 15:43:16 18

18 【8-15】端口配置寄存器 32位IDR 数据寄存器 32位 输入ODR 数据寄存器 32位 输出BSRR 置位/复位寄存器 32位BRR 复位寄存器 16位LCKR 锁存寄存器 32位3、常用的IO端口寄存器 CRL CRH IDR ODR4、CRL ...

2022-01-13 16:15:59 3

3 仅供个人学习使用STM32 的每个 IO 端口都有 7 个寄存器来控制。他们分别是:配置模式的 2 个 32 位的端口配置寄存器 CRL 和 CRH;2 个 32 位的数据寄存器 IDR 和 ODR

2022-01-13 16:32:20 0

0 1. GPIO相关寄存器1.1 配置寄存器(CRL、CRH)1.2 数据寄存器(IDR、ODR)1.3 位设置/清除寄存器(BSRR)1.4 锁定寄存器(LCKR)1.5 位清除寄存器(BRR)2.

2022-01-17 09:33:10 2

2 stm32使用延时实现呼吸灯(寄存器)该实验是使用STM32F103C8T6实现,使用寄存器编程。呼吸灯:灯光的亮度在控制下不断的从亮到暗,再从暗到亮之间变化,感觉好像是人在呼吸。一般使用PWM

2022-01-18 10:33:22 0

0 电平兼容的 ;I/O 控制寄存器说明:2 个 32 位的端口配置寄存器 CRL 和 CRH;2 个 32 位的数据寄存器 IDR 和 ODR;1 个 32 位的置位/复位寄存器BSRR;1个 16 位的复位寄存器 BRR;1 个 32 位的锁存寄存器 LCKR。

2022-01-18 10:52:27 7

7 每个GPI/O端口有两个32位配置寄存器(GPIOx_CRL, GPIOx_CRH),两个32位数据寄存器(GPIOx_IDR和GPIOx_ODR),一个32位置位/复位寄存器(GPIOx_BSRR

2022-05-31 11:13:27 2087

2087

第一行是偏移地址。偏移地址指明了这个寄存器相对于外设寄存器区段的位置,从起始地址表中我们可以知道 GPIOA 寄存器区段的起始地址是 0x4001_0800,而 GPIO_BSRR 的偏移地址

2023-05-31 17:36:10 979

979

既然ODR能控制管脚高低电平,为什么还需要BSRR寄存器呢? 为什么需要BSRR寄存器 在单片机中,为了控制端口的输出状态,我们需要使用特定的寄存器。其中,ODR寄存器负责直接控制端口输出电平

2023-10-24 11:49:17 1731

1731

电子发烧友App

电子发烧友App

评论