全球 3D NAND 价格近来快速崩跌,紫光集团旗下的长江存储肩负打破国内“零”存储自制率之重任,以”光速”的气势加入这场存储世纪大战。除了武汉 12 寸厂进入生产,南京厂也将于年内动工,加上成都厂,紫光将先后启动三大基地生产 3D NAND 芯片,即使合计投资金额高达 1,800 亿人民币,花十年目标换来比肩巨人三星、东芝的机会,紫光此举看来大胆但却值得!

大陆占全球总存储的消耗量 50 %,但芯片自制率几乎是零,全数仰赖美国、日本、韩国进口,紫光集团旗下的长江存储投入 3D NAND 研发近四年时间,今年 32 层芯片进入生产,紫光集团董事长赵伟国在南京举行的“中国芯片发展高峰论坛 China IC Summit ”中骄傲指出,中国已有第一支采用自己自主研发芯片所生产的U盘。

紫光位于武汉的 12 寸晶圆厂今年投入32 层 3D NAND 芯片生产,目前以月产能2000 片小量生产,该生产基地规划三座大型 12 寸晶圆厂,合计单月产能上看 30 万片。

不仅如此,紫光位于南京的半导体项目也将投入 3D NAND 芯片生产,目前南京基地已进入整地阶段,最快将于年底前动工,同时,成都的半导体项目也计划投入 3D NAND 芯片,合计紫光在武汉、南京、成都三大生产基地将投入 1,800 亿人民币生产 3D NAND 芯片,以冲刺经济规模的战略,换取比肩国际大厂的契机。

看好 3D NAND 未来五年需求大好,技术瓶颈存在,紫光要用力赶上

由于全球存储芯片价格崩跌之势已现,对于紫光在此时大动作进行扩产,也让外界不禁担心,紫光若启动三大生产基地生产 3D NAND 芯片,会不会演变成长期产业供过于求的危机?

甫从华为离职加入紫光集团担任执行副总裁的楚庆独家对 DT 君分析 3D NAND后续走势看法 ,楚庆认为,无论是从供给面或是技术面来看,未来 NANDFlash 产业前景都非常乐观,今年旗舰级智能手机的存储容量是 256GB ,明年会成长到 512GB ,消耗的存储芯片越来越可观,但3D NAND技术会遇到不小瓶颈。

他表示,去年华为因为 NAND Flash 芯片缺货造成销售额短少 40 亿美元,内部更因此成立战略领导小组来分析因应供给短缺的情況。

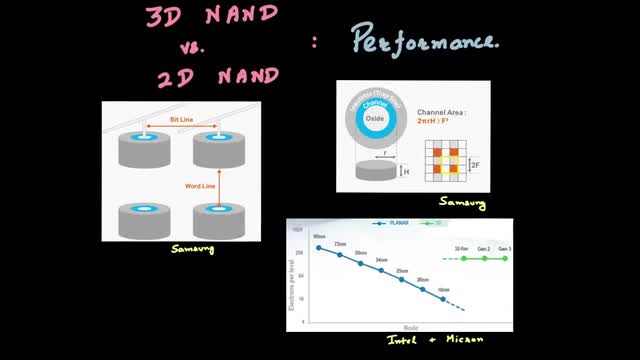

楚庆分析,虽然 3D NAND 技术不断往上迭,从 32 层迭到 64 层,但到了 96 层技术,就不会是一年密度增长一倍的速度了,等堆迭到了 128 层,之后的发展可能是堆迭到 144 层左右,技术挑战越来越艰难,供给不会一直顺利产出,因此,紫光对于未来五年的存储市场抱持乐观态度。

对于眼前 3D NAND 产能过剩,楚庆反而认为这是短暂现象,因为现有的几家半导体大厂包括三星、东芝都是同步发展 96 层技术,伴随技术突破,一定会有不少产能增加,形成供过于求,但这些新产能很快就会被新增的需求吃掉。

再者,楚庆也认为未来 3D NAND 技术从 96 层堆迭到 128 层技术后,每一个世代的技术进展会从原本的 12 个月,拉长至 18 个月才能达到,而紫光在存储领域也会有全新的战略来因应,外界可以拭目以待。

长江存储 Xtacking 惊艳背后的辛酸,杨士宁:选择这条路要很大勇气

今年国际存储大厂三星、东芝、美光、西部数据、SK海力士已进入 64 层 3D NAND 技术的生产,并且完成 96 层 3D NAND 技术研发,寄希望于 2019 年投产,三星更要抢在今年第四季率先小幅量产 96 层芯片,除此之外,众家大厂未来更要再往上朝 128 层 3D NAND 技术开发。

长江存储身为后发者,为了要快速赶上国际大厂的脚步,计划在 64 层技术之后,会跳过 96 层技术,直攻 128 层 3D NAND 芯片,就技术规划来看,业界传出紫光将会以两颗 64 层芯片直接做堆迭的方式开发生产。

再者,长江存储近期提出的 Xtacking 新架构引发全球存储产业一阵骚动。长江存储首席执行官杨士宁在 Flash Memory Summit 期间透露, Xtacking 架构有很多好处,但挑战也不少,决定选择走上这一条道路需要勇气,因为要让这个技术发挥作用并不容易,他和紫光集团全球执行副总裁高启全来回讨论多次才下此决定。

Xtacking 架构技术的基础是来自于武汉新芯开发多年的 CMOS 成像器的打线封装技术( Wafer Bonding ),长江存储为了将该技术用于 3D NAND 开发,将其“几微米的间距”缩小到仅约 100 nm。

当中,最为困难的一部分是存储和逻辑元件的对淮技术,使用位于晶圆上方和下方的摄影机,透过等离子体活化被挤压在一起的晶片表面,再以低温退火做处理。然后,于 I/O 晶圆的背面进行加工,以便在晶片背面形成焊垫。

Xtacking 架构将逻辑和存储元件上下相迭且分开加工,有效解除 I/O 传输瓶颈

而对于Xtacking技术细节,长江存储联席首席技术官汤强出席“中国芯片发展高峰论坛 China IC Summit ”时有非常详尽的解说。

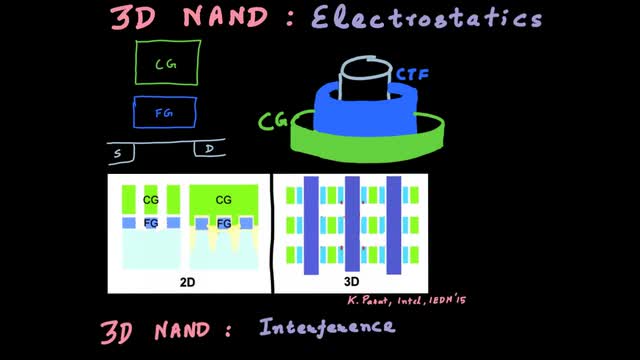

汤强表示, NAND Flash 是串连式的存储,传统的 2D NAND 技术是二维平面结构,随着尺寸微缩越来越小,面临的挑战越来越多,这其中包括成本过高,以及越来越多的干扰信号等等问题,因此,大家开始想解决方案,把串连式的存储从平面竖起来,发展成立体三维结构的 3D NAND,可大幅提高存储密度,同时也避开光刻上成本的增加,也解决干扰技术。

不过, 3D NAND 技术也同样面临挑战,主要面临来自三大方面,包括 I/O 传输速度、存储密度、产品上市周期,而这三大方面正是存储技术的核心竞争力之所在。

汤强解释,在进行半导体加工时,会先做外围负责驱动、传输功能的逻辑电路元件,之后加工存储阵列元件,但加工存储阵列元件时所采用的高温高压工艺,会影响之前已经加工完成的逻辑元件,在逻辑电路上的工艺最多只能做到 0.18 微米制程,速度上无法提升,导致 I/O 的线性传输会卡住。

长江存储Xtacking的解决方式,是把外围逻辑电路和存储阵列电路两个模块分开加工,之后两个模块从水平摆放,变成上下堆迭摆放在一起,如此一来可解除 I/O 传输瓶颈,有效提升速度,因为在加工外围逻辑电路的时候,就不会被阵列电路加工时的高温高压所影响。

因此,逻辑电路可以采用更为先进的工艺,从 0.18 微米制程的加工技术,放宽到 90 纳米、 55 纳米、 28 纳米,甚至是采用高端的 16 纳米、 10 纳米制程生产,完全贴紧逻辑电路往前进的步伐。

再者,现在的 I/O 传输速度瓶颈是0.8 Gb/秒,将来采用先进工艺后,可以放宽至 3 Gb/秒,这和 DRAM 的传输速度可以有效缩短。

为了解决体积问题,并且增加芯片密度,两块加工完毕的模组从水平摆放变成堆迭摆放,把外围电路放在阵列电路之下,这使得 Xtacking 的面积利用率从传统的 65 %提升至 90 %。

其实也有其他国外大厂采用类似技术,将外围逻辑电路直接摆放在存储阵列电路的下面为 PUA,然 Xtacking 技术不一样之处在于,是分成个模块同时做,可缩短研发周期,工艺不会受到干扰,然后再将模块拼再一起,未来甚至可以把外围逻辑电路交给外面做代工,灵活度提升。

长江存储将从第二代 3D NAND 采用 Xtacking 架构,让优势尽情发挥

然而, Xtacking 技术也同样面临三大难题,第一是硅片的平整度,随着存储堆迭变高,平整度地挑战是很大的。第二是对孔的对淮精度,要把整片硅片所有的孔都对淮,并且接通,这相当不容易。第三是接口材料的选择,长江存储甚至和合作供应商合作研发一款新的 CMP 研磨机台。

在经过多时努力,现在 Xtacking 技术良率提升非常快,结构的可靠性也很好,在编程擦写 3,000 次之后,可靠度仍是维持一样。且针对可靠度测试上,包括温度循环测试(Thermal Cycle )、高温存储测试( High Temp. Storage )、电子迁移测试( Electro-migration ),都通过考验。

长江存储将从第二代( 64 层技术)的3D NAND 采用 Xtacking 架构,未来各代技术也都会导入。未来 3D NAND 层数堆迭越来越高时,伴随而来的是外围电路的占比会变很大,这时,Xtacking 技术的优势便可以越来越有得发挥。

长江存储的 Xtacking 技术概念最令人惊艳的是传输速度可以达到 3Gbps ,比肩DRAM的传输水准,加上明年量产 64 层 3D NAND 后,要一举直攻 128 层技术,刚好国际大厂在 128 层技术后会放缓脚步,因此有充裕时间可以追赶。

若 Xtacking 技术成功量产,会是国内存储产业的重大里程碑,更为芯片自主开发的道路注入强心针,且紫光将以武汉、南京、成都三个生产基地投入 3D NAND 芯片生产,下一步要玩经济规模之战,以期快速追上国际大厂,快速打破国内“零”自制存储芯片的现况,并且跻身国际大厂之林。

电子发烧友App

电子发烧友App

评论