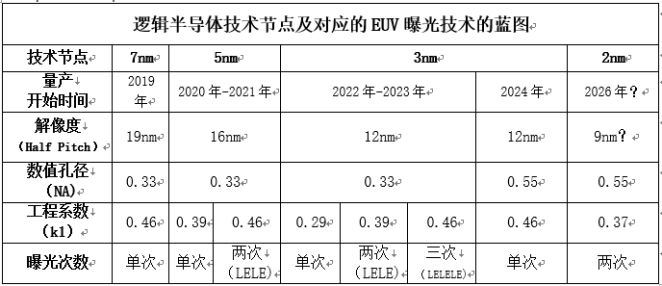

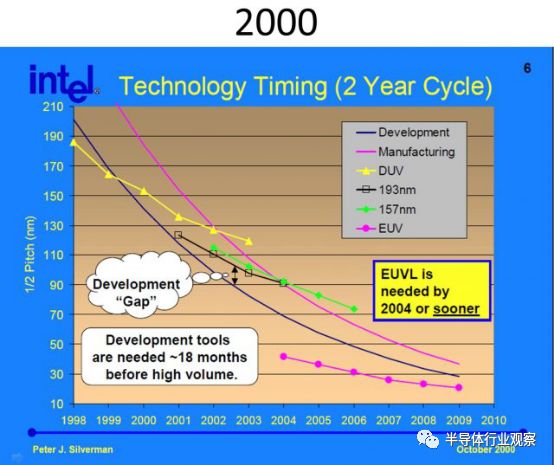

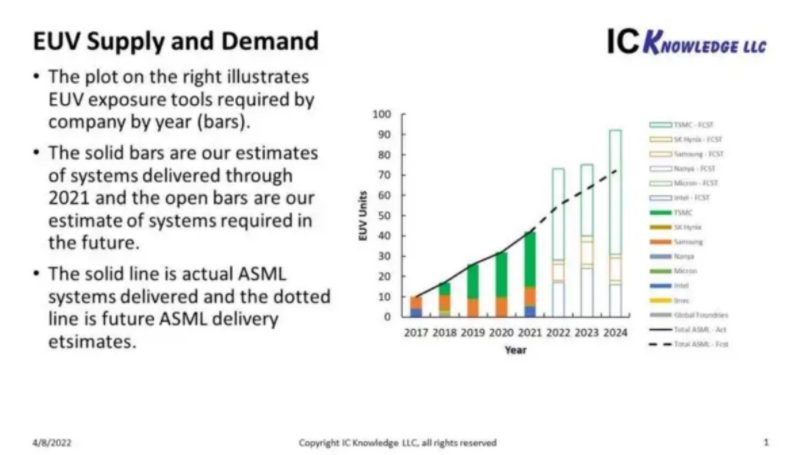

用于高端逻辑半导体量产的EUV(Extreme Ultra-Violet,极紫外线光刻)曝光技术的未来蓝图逐渐“步入”我们的视野,从7nm阶段的技术节点到今年(2019年,也是从今年开始),每2年~3年一个阶段向新的技术节点发展。

高端逻辑半导体的技术节点和对应的EUV曝光技术的蓝图。

也就是说,在EUV曝光技术的开发比较顺利的情况下,5nm的量产日程时间会大约在2021年,3nm的量产时间大约在2023年。关于更先进的2nm的技术节点,还处于模糊阶段,据预测,其量产时间最快也是在2026年。

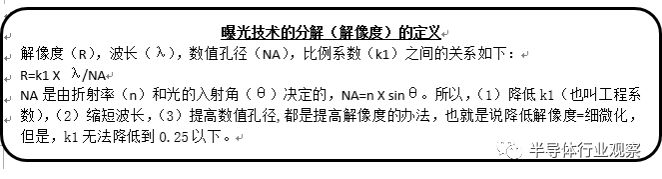

决定解像度(Half Pitch)

的是波长和数值孔径、工程系数

技术节点的发展推动着半导体曝光技术解像度(Half Pitch)的发展,ArF液浸曝光技术和EUV曝光技术等的解像度(R)和曝光波长(λ)成正比,和光学的数值孔径(NA,Numerical Aperture)成反比,也就是说,如果要增大解像度,需要在缩短波长的同时,扩大数值孔径。

实际上,解像度和被称为“工程系数(k1)”的定数也成一定的比例关系。如果降低工程系数,解像度就会上升。但是,工程系数如果降低到最小极限值(0.25),就无法再降低了。

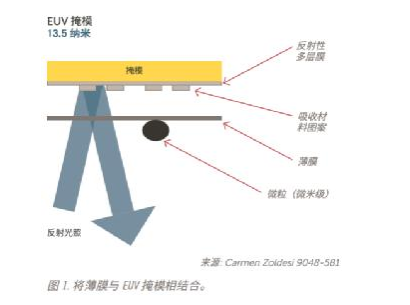

ArF液浸曝光技术、EUV曝光技术中的解像度(Half Pitch)(R)和波长、数值孔径(NA)、工程系数(k1)的关系。

在ArF液浸曝光技术、EUV曝光技术中,光源的波长是固定的,无法改变。顺便说一下,ArF液浸曝光的波长是193nm,EUV曝光的波长是13.5nm。两者有超过10倍的差距,单纯计算的话,EUV曝光绝对是占优势。

对ArF液浸曝光技术以前的光制版(lithography)技术来说,提高数值孔径是提高解像度的有效手段。具体来说,就是通过改良作为曝光设备的Stepper和Scanner,来提高数值孔径。

与之相反,运用EUV曝光技术的话,不怎么需要改变数值孔径,EUV曝光技术利用X线的反射光学系统,光学系统拥有非常复杂的构造,同时光学系统的变化也会伴随着巨额的开发投资。所以,过去一直以来EUV曝光设备方面从没有更改过数值孔径。最初的EUV scanner的数值孔径是0.25,现行设备的数值孔径是0.33,不管怎么说,和ArF Dry曝光技术的最高值(0.93)相比,都是很低的。

正如在本栏目中去年(2018年)12月报道的一样(使用EUV曝光的高端逻辑半导体和高端DRAM的量产终于开始了!),用于量产7nm的最尖端逻辑半导体的EUV scanner--“NXE:3400B”内置的数值孔径是0.33。

而且,今后数年内,都会在使用数值孔径为0.33的EUV scanner的同时,提高解像度。换句话说,也就是通过使用同样数值孔径的曝光设备来使解像度(Half Pitch)更细微化。

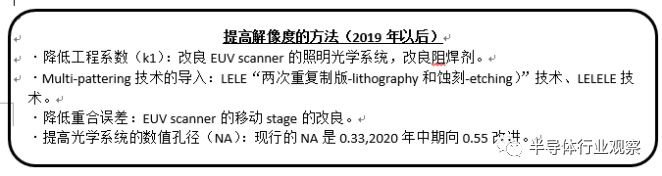

通过阶段性地降低工程系数来提高解像度

所以,很多用来提高细微化的办法都被限制了,因为波长和数值孔径是固定的,剩下的就是工程系数。光学方面,通过降低工程系数,可以提高解像度。和ArF液浸曝光技术一样,通过和Multi-patterning 技术组合起来,就可以达到实质上降低工程系数的效果。而且,机械方面,有必要降低曝光设备的重合误差。

提高EUV曝光技术的解像度的方法(2019年以后)

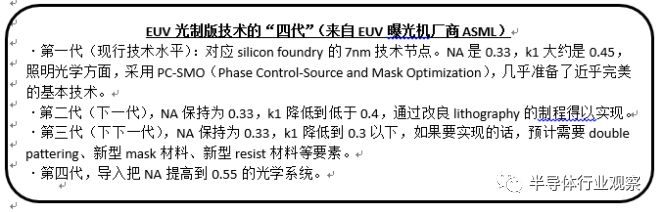

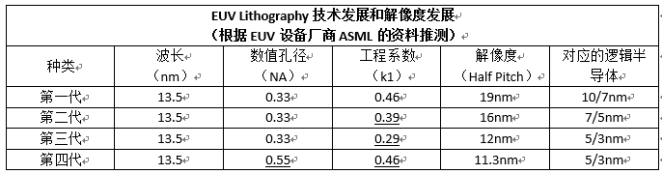

据EUV曝光设备厂商ASML说,他们把未来EUV曝光技术方面的细微化工作分为“四代”。现行技术水平是第一代,同时也是7nm逻辑半导体的量产是用的技术。工程系数是0.45左右。

第二代是把工程系数降低到0.40以下,通过改良曝光技术的硬件(光学方面)和软件(阻焊层,resist)得以实现。其技术核心也不过是改良现行技术。

第三代是把工程系数降低到0.30以下,要得以实现,只改良现行技术比较困难,需要导入像Multi-pattering、新型mask材料、新型resist材料等这些基本要素。

第四代,由于工程系数无法再降低,所以开发新的光学系统,它可以数值孔径提高到0.55。

EUV曝光设备厂家ASML公布的EUV曝光技术的发展。

ASML公布的技术发展资料里面没有提到工程系数的具体数值,不过我们把工程系数的假设值放进去计算了一下,看看解像度可以提到何种程度,现行(第一代)的工程系数是0.46,其对应的解像度(Half Pitch)是19nm。

假设第二代的工程系数为0.39,对应的解像度为16nm,如果是最先进的逻辑半导体的技术节点的话,可以适用于7nm~5nm的量产品。

假设第三代的工程系数是0.29,对应的解像度是12nm,如果是最先进的逻辑半导体的技术节点的话,可以适用于5nm~3nm的量产品。

由于第四代大幅度更改了数值孔径,工程系数假设为0.46,和第一代相同。假设数值孔径为0.55,工程系数即使增加为0.46,相对应的解像度也和第三代基本相同,为11.3nm,可以适用于5nm~3nm的量产品。

EUV曝光技术发展和解像度的发展。以EUV曝光机厂商ASML发布的数据为基础作者推测的数字。

把Multi-patterning(多重曝光)

导入到EUV曝光技术里

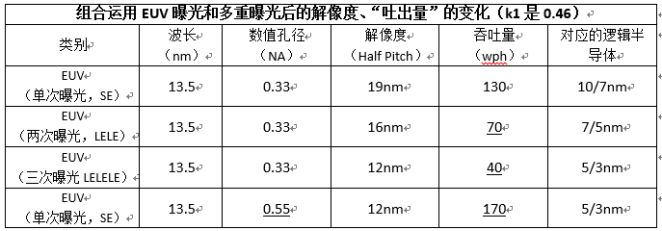

不需要改良光学系统和阻焊层(resist)等曝光技术,把工程系数k1实质性地降低的办法----Multi-patterning(多重曝光)技术。正在讨论把ArF液浸曝光方面广泛普及的多重曝光技术应用到EUV曝光技术里。

比方说,两次曝光就是导入LELE技术,即重复两次Lithography(L)和Etching(E),如果把LELE技术导入到工程系数为0.46的EUV曝光技术(数值孔径为0.33)上,解像度会变为16nm,这和把单次曝光时的工程系数降到0.39得到的效果一样。

三次曝光,即导入LELELE技术,重复三次Lithography(L)和Etching(E),再次降低解像度,为12nm,这和把单次曝光时的工程系数降低到0.29得到的效果一样。

但是,利用多重曝光技术的话,“吞吐量(through-put)”会大幅度降低,单次曝光(SE技术)的晶圆处理数量约为130片/小时,两次曝光(LELE)曝光的话,下降为70片/小时,三次曝光(LELELE)曝光的“吞吐量”下降为单次的1/3,为40片/小时。

联合运用EUV曝光和多重曝光的解像度和“吐出量”的变化(k1是0.46),作者根据ASML公布的数据总结的数字。

总结一下,新型的5nm技术有两个方向,第一、维持着单次曝光技术的同时,把工程系数下降到0.39;第二、通过利用两次曝光(LELE技术)技术,实质性地降低工程系数。两个的解像度都是16nm,预计量产开始时间为2021年。如果采用两次曝光技术,预计量产时间可以提前到2020年。

第三代的3nm技术的节点稍微有点复杂,有三个方向:第一、把单次曝光的工程系数维持为0.29;第二、联合两次曝光(LELE技术)和把工程系数改为0.39的曝光技术;第三、利用三次曝光(LELELE)技术。三个方向的解像度都是12nm,预计量产时间为2023年。但是,如果采用三次曝光的话,量产时间有可能再提前。

关于第四代2nm技术节点,如果用数值孔径为0.33的EUV曝光技术估计很难实现。应该是期待把数值孔径提高到0.55的EUV曝光技术。

EUV曝光设备的组合运用,

继续改良精度和生产性能

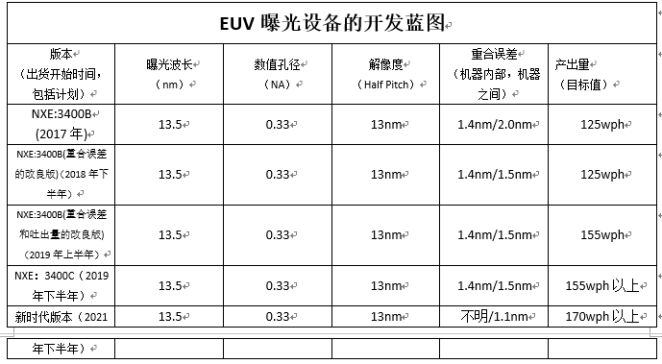

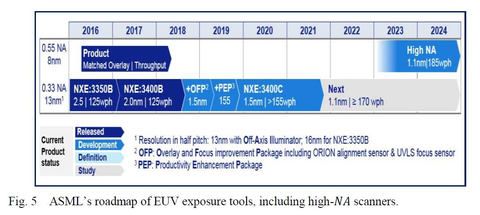

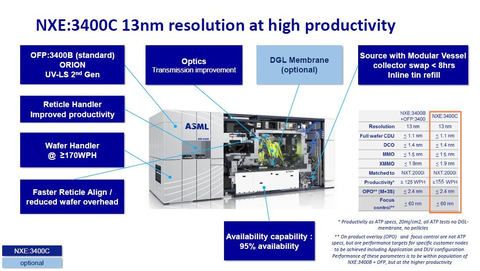

EUV曝光技术的开发方面最重要的是EUV曝光设备(EUV scanner)的改良。EUV曝光设备厂商ASML已经公布了继用于现行量产品7nm的EUV scanner--“NXE:3400B”之后的开发蓝图。

据ASML的技术蓝图预测,以“NXE:3400B”为基础,首次开发降低重合误差的版本,后面是以“降低重合误差版本”为基础,开发提高“吐出量”(生产性能)的版本。预计在今年(2019年)的上半年,完成这些改良。

基于以上改良成果的新产品“NXE:3400C”预计会在今年年末开始出货,预计“NXE:3400C”将要“担任”5nm的量产工作。

而且,降低重合误差的同时,还要开发提高产能的新版本,ASML还没有公布新版本的型号,出货时间预计在2021年的下半年,新版本应该会承担3nm的量产工作吧。

EUV曝光设备(EUV scanner)的开发蓝图,作者根据ASML公布的数据汇总的。

EUV曝光设备的开发蓝图,摘自2018年12月ASML在国际学会IEDM上发布的论文。

新一代用于量产的EUV曝光设备(EUV scanner)“NXE:3400C”的概要,出自ASML在2018年12月国际学会IEDM的演讲资料。

这些曝光设备基本都是搭载了数值孔径为0.33的光学系统。ASML同时也在致力于开发把数值孔径提高到0.55的EUV曝光设备。

被ASML称为“High NA”的、数值孔径为0.55的EUV scanner的出货时间预计在2023年的下半年,首批试验设备预计在2021年年底做成。

-

半导体

+关注

关注

334文章

27290浏览量

218086 -

机械

+关注

关注

8文章

1570浏览量

40523 -

数值

+关注

关注

0文章

80浏览量

14359

发布评论请先 登录

相关推荐

EUV热潮不断 中国如何推进半导体设备产业发展?

光刻机工艺的原理及设备

魂迁光刻,梦绕芯片,中芯国际终获ASML大型光刻机 精选资料分享

助力高级光刻技术:存储和运输EUV掩模面临的挑战

关于EUV光刻技术的分析和应用

关于EUV光刻技术的分析和应用

评论