我们所知道的计算机系统是建立在网络和存储速度较慢,而CPU内存的反应速度较快基础上的。多年来,设计人员为这些组件开发了相应的语言和接口,需要多层软件将内存命令转换为网络和存储命令,反之亦然。

到目前为止,CPU内存对相对于网络和存储I / O的速度使得这些软件层对系统性能的影响很小。

然而,随着摩尔定律的发展,网络和存储技术正迅速赶上CPU内存速度,现在几代软件层发挥的作用变得越来越重要。

在本文中,我们将Gen-Z结构视为消除现有系统瓶颈的解决方案,并通过统一通信路径并使用CPU内存加载/存储语言简化软件来显着提高系统效率和性能。

迈向新的计算架构

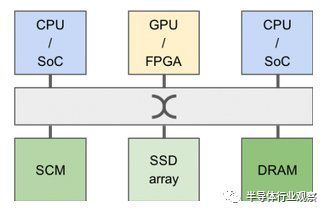

如图1所示,计算架构正在迅速发展为异构系统,包括多种计算单元(CPU / SoC,GPU,FPGA)和不同类型的内存/存储元件(DRAM,存储器),在本地互连在一起或远程通信。

此类体系结构应通过允许添加或删除资源,或在更新版本/技术可用时替换此类资源来提供更好的灵活性和可伸缩性。

图1 - 新的计算架构

以CPU为中心的方法

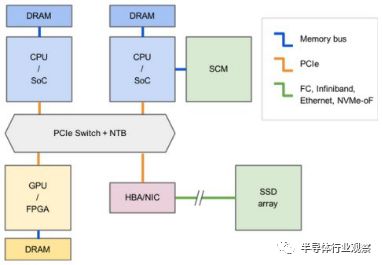

利用当今以CPU内存为中心的方法,图1中的系统使用各种硅组件、接口和软件层实现,如图2所示。

图2 - 以CPU内存为中心的系统架构

在计算系统的这种特定实现中,PCI Express被用来连接CPU内存、GPU / FPGA内存和高性能/低延迟存储器。SSD阵列通过主机总线适配器或NIC连接,使用光纤通道、Infiniband、NVMe-oF或以太网作为传输接口。

其中一个CPU的DRAM中的数据必须在到达SSD阵列之前遍历4个接口域,随后会产生相关的软件开销和缓冲区复制操作。

这里,可扩展性是一个问题:升级到下一代SCM可能需要升级/更换相关的CPU / SoC。同样,扩展SSD阵列可能需要HBA / NIC下游的结构交换机。

内存语义方法

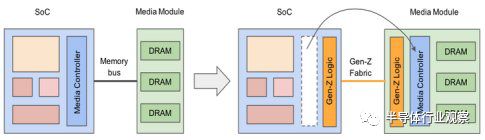

Gen-Z是一种内存语义结构,它将CPU内存字节可寻址的加载/存储模型扩展到整个系统。事实证明,加载/存储模型是CPU与内存子系统通信的最快、最有效的方法。为了启用此模型,Gen-Z将计算与介质分离,将介质特定功能与其正确所属的介质放在一起。图3说明了这个原理。

图3 - 从CPU内存接口到与介质无关的结构

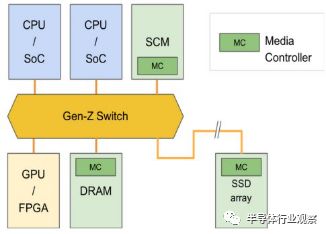

这一重要变化允许系统中的每个计算实体都是介质不可知和分解的。使用Gen-Z内存语义结构,可以使用交换拓扑实现图1中的系统,如图4所示。

图4 - 使用Gen-Z的系统架构

通过这种方法,所有设备彼此对等并通过简化的、高性能、低延迟的通信路径说出相同的加载/存储语言,而不会导致当前总线体系结构的转换惩罚和软件开销。

Gen-Z协议定义了大量的内存语义操作(通过OpCodes / OpClasses),可以实现高效的数据传输,以卸载计算资源,优化互连使用并降低软件开销。在所示的示例中,可以使用适当的OpCode / OpClass在一次加载和一次存储操作中将来自DRAM的数据复制到SSD阵列。

在可扩展性方面,系统可以通过独立升级,添加或删除计算,内存或存储元素而不影响功能,为每个工作负载和环境精确定制。

关于Gen-Z

Gen-Z架构专注于提供高效率、高带宽和低延迟。

通过利用经过验证的装载/存储模型实现高效率。简化了Gen-Z硬件接口层,从而最大限度地减少了对软件层的需求。消除这种复杂性、开销和诱导系统延迟可以显着提高系统性能。

高带宽以两种方式实现。Gen-Z支持非对称通信路径,这意味着可以将更多通道专用于读取路径而不是写入路径,反之亦然。此外,Gen-Z支持多种信令速率,包括16,25,32,56和112 GT / s。总而言之,这些功能将使Gen-Z能够跟上行业不断增长的速度需求,同时还允许将Gen-Z通信路径调整为特定的工作负载流量模式。

通过减少软件堆栈来实现低延迟。与传统的服务器存储和大量分层的网络堆栈不同,Gen-Z采用轻量级软件接口,直接对硬件进行内存读写操作。

芯片设计师需要的Gen-Z资源

希望成功开发Gen-Z产品的芯片设计师需要一些关键资源,具体如下:

Gen-Z控制器IP:SoC、交换机、存储介质控制器和其他类型的Gen-Z设备都需要可配置的高质量控制器IP才能连接到Gen-Z结构。在撰写本文时,两家IP供应商,Gen-Z联盟的成员已经宣布了Gen-Z控制器IP的当前和未来可用性。

Gen-Z PHY IP:初始Gen-Z实施将专注于经过验证的、部署的NRZ PHY信令技术和速度,利用16和32 GT / s的PCIe PHY和25 GT / s的IEEE802.3 PHY的可用性。后期部署可能会利用先进的PAM4 PHY信令速率,如56和112 GT / s。

Gen-Z验证IP:全面验证IP(VIP)工具的可用性对于保证集成在SoC之前和之后Gen-Z IP的质量至关重要。在撰写本文时,两家供应商已宣布为Gen-Z提供验证IP。

FPGA原型开发板:FPGA原型开发是确保系统级功能和互操作性的必要步骤。目前的FPGA技术允许Gen-Z原型设计高达56 GT / s(PAM4)和32 GT / s(NRZ)。还开发了连接器,以通过铜和光学连接以这些速率实现多通道Gen-Z信令。FPGA原型开发板可从多家供应商处获得,预计基于FPGA技术的Gen-Z特定原型开发平台即将推出。

Gen-Z联盟包括来自各个技术领域的成员,这对于构建产品生态系统至关重要,其中所有必需的硬件和软件组件彼此互操作。

结语

Gen-Z为计算机行业提供了一个独特的机会,可以利用现有的CPU内存重新定义现代计算并克服当前的挑战。随着新公司继续加入不断发展的Gen-Z开放式生态系统,构建模块、产品和服务的可用性自然会增加,并使新设计和产品能够应对新的工作负载和新出现的挑战。

Gen-Z为创新的高性能、低延迟解决方案提供了机会,这些解决方案将是开放、简单且经济、高效的。

-

数据传输

+关注

关注

9文章

1894浏览量

64607 -

网络

+关注

关注

14文章

7567浏览量

88795 -

传输接口

+关注

关注

1文章

15浏览量

10332

发布评论请先 登录

相关推荐

关于Gen-Z语义存储(memory-semantic)体系架构探讨

如何创建最佳的网络和架构 一文解析Gen-Z架构

EVAL-ADPD105Z-GEN信号是如何引入的,是否自带发光管和接收管?

TE推出Sliver互连解决方案,具有高性能、灵活性、成本低等特点

关于Z轴TMR传感器的性能介绍和应用分析

关于MDT推Z轴TMR传感器的性能分析和应用介绍

关于USB 3.1 Gen 2 Type-C线缆配置和PVC护套的性能分析和介绍

处理器和加速器互联的开发将得到进一步发展

PCIe Gen 4协议分析仪的竟然那么强大!

最新PCIe Gen 5 switch芯片已内置SerialTek PCIe抓包分析功能

iQOO Z6 Lite首发骁龙4 Gen 1处理器

高通骁龙8Gen3性能如何?

关于Gen-Z的性能和原理分析

关于Gen-Z的性能和原理分析

评论