推动晶体管往5nm以下节点微缩是VLSI工业的关键问题之一,因为越变越小的晶体管带来了各种各样的挑战,全世界也正在就这个问题进行一些深入研究以克服未来技术节点的挑战。

在本文,我们回顾了包括如碳纳米管FET,Gate-All-Around FET和化合物半导体在内的潜在晶体管结构和材料,他们被看做解决现有的硅FinFET晶体管在5nm以下节点缩放的问题。

半导体时代始于1960年,是伴随着集成电路的发明而开启的。在集成电路中,所有有源/无源元件及其互连都集成在单个硅晶圆上,这就使得它们在便携性、功能性、功耗和性能方面具有领先的优势。而在过去几十年里,VLSI行业也在摩尔定律的“指导”下快速发展。所谓摩尔定律,是指集成在芯片上的晶体管数量大约每两年增加一倍。

为了从缩小尺寸的晶体管获得相应的收益,VLSI行业在不断改进晶体管的结构、材料、制造技术以及设计IC的工具。到目前为止,晶体管所采用的各种技术包括了高K电介质,金属栅极,应变硅(strained silicon),双图案化(double patterning),从多个侧面控制通道,绝缘体上的硅(SOI)和更多技术。其中一些技术在《关于CMOS,SOI和FinFET技术的评论文章》中有讨论过。

如今,物联网,自动驾驶汽车,机器学习,人工智能和互联网流量的需求呈指数增长,这将给晶体管带来了缩小到现有7nm节点以下以获得更高性能的驱动力。然而,缩小晶体管尺寸却存在若干挑战。

亚微米(Sub-Micron)技术的问题:

每次我们缩小晶体管尺寸时,都会生成一个新的技术节点。所以我们已经看到了如28nm,16nm等的晶体管尺寸。我们知道,缩小晶体管可以实现更快的开关、更高的密度、更低的功耗,更低的每晶体管成本以及跟多的其他增益。

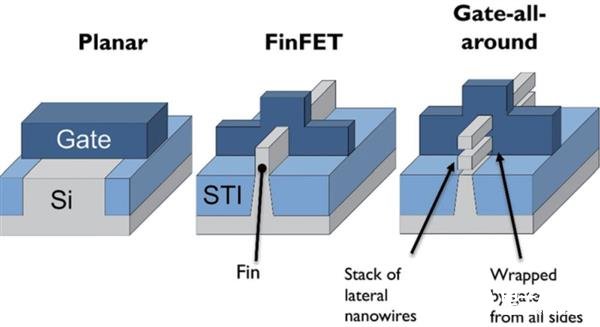

基于CMOS(互补金属氧化物半导体)的晶体管可以在28nm节点上运行良好。然而,如果我们将CMOS晶体管缩小到28nm以下,则短沟道效应变得不可控制。在该节点下,由drain-source电源产生的水平电场试图控制通道。结果,栅极不能控制远离它的漏电路径。

16nm / 7nm晶体管技术:FinFet和FD-SOI:

VLSI工业已采用FinFET和SOI晶体管用于16nm和7nm节点,因为这两种结构都能够防止这些节点的漏电问题。这两种结构的主要目标是最大化栅极到沟道(gate-to-channel)的电容并最大限度地减小漏极到沟道(drain-to-channel)的电容。在两个晶体管结构中,引入沟道厚度缩放作为新的缩放参数。随着沟道厚度减小,没有路径(path),因为它已经远离了栅极区域离。因此,栅极对通道具有良好的控制,这就消除了短通道效应。

在绝缘体上硅(SOI)晶体管中,使用掩埋氧化物层,其将主体与图1(a)中所示的衬底隔离。由于BOX层,漏—源(drain-source)寄生结电容减小,这带来更快的切换。对SOI晶体管来说,它们面对的主要挑战是难以在芯片上制造薄硅层。

图1:a)FD-SOI结构b)FinFET结构和通道

FinFET,也称为三栅极控制通道,如图1(b)中的三个侧面所示。我们可以看到,有一个薄的垂直“硅体”,看起来像是由栅极结构包裹的鱼的Fin。通道的宽度几乎是Fin高度的两倍。因此,为了获得更高的驱动强度,我们就使用了多Fin结构。FinFET的收益之一是带来了更高的驱动电流需求。但FinFET面临的主要挑战是复杂的制造工艺。

5nm以下的挑战:下一步是什么?

随着表面粗糙度散射增加的,同时减小“硅体”厚度,这将会带来较低的迁移率。这主要因为FinFET是3D结构,所以降低了散热方面效率。此外,如果我们进一步缩小FinFET晶体管尺寸,比如低于7nm,则漏电问题再次出现。再加上如自加热(self-heating)和阈值平坦化(threshold flattening)等诸多问题也会被考虑进来,这就推动我们去研究其他可能的晶体管结构,并用新的有效材料替换现有材料。

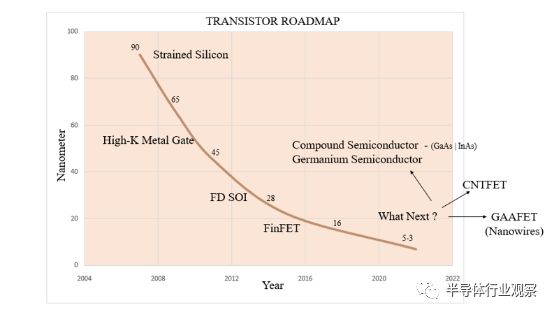

根据ITRS路线图(国际半导体技术路线图),下一代技术节点分别为5nm,3nm,2.5nm和1.5nm。在VLSI行业和学术界,也正在进行许多不同类型的研究和研究,以寻找满足这些未来技术节点要求的潜在解决方案。在这里,我们讨论一些有前景的解决方案,其中包括了碳纳米管FET(carbon nanotube FET)、GAA晶体管结构和化合物半导体等用于未来节点的技术。

图2:晶体管技术路线图

CNTFET - 碳纳米管FET:

CNT(碳纳米管)展示了一类新兴的半导体材料,它是由卷起的单片碳原子组成以形成的管状结构。CNTFET是一个场效应晶体管(FET),使用半导体CNT作为两个金属电极之间的沟道材料,这就形成了源极和漏极接触。在这里,我们将讨论碳纳米管材料以及它如何在较低的技术节点下给FET带来提升。

什么是碳纳米管?

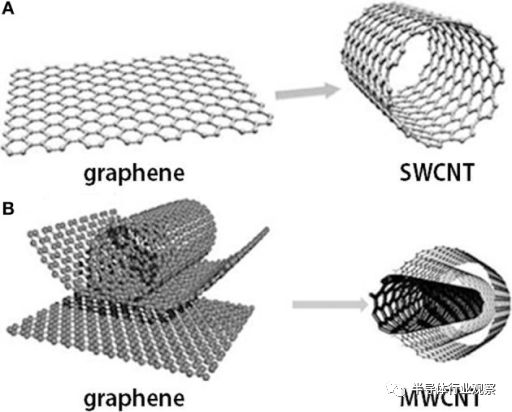

CNT是由碳制成的管状材料,拥有可在纳米尺度上测量的直径。它们具有长而中空的结构,由一个原子厚的碳片形成,这个东西就被称为“石墨烯”(Graphene)。碳纳米管具有不同的结构、长度、厚度、螺旋度和层数。主要被分类为单壁碳纳米管(Single Walled Carbon Nanotube :SWCNT)和多壁碳纳米管(Multi-Walled Carbon Nanotube :MWCNT)。如所示图3(a) ,可以看到,单壁碳纳米管是由单层的石墨烯构成,而多壁碳纳米则是由多个石墨烯层组成。

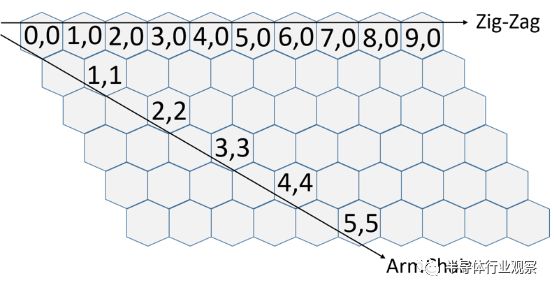

图3:a)单壁和多壁CNT b)手性矢量表示

碳纳米管的特性:

碳纳米管在热稳定性和物理稳定性方面具有优异的表现,如下所述:

1、金属和半导体行为

CNT可以表现出金属和半导体行为。这种行为变化取决于石墨烯片的卷绕方向,这被称为手性矢量(chirality vector)。该向量由一对整数(n,m)表示,如图3(b)所示。如果'n'等于'm',或者'n'和'm'的差值是三的整数倍,则CNT表现为金属,否则它表现为半导体。

2、令人难以置信的流动性

因为SWCNT能够表现为金属或半导体,所以拥有对称传导(symmetric conduction)和承载大电流的能力,这就使得它们具有很强的电子应用潜力,由于沿CNT轴的低散射率,沿CNT长度的电子和空穴具有很高的电流密度。数据显示,CNT可以承载大约10 A / nm^ 2的电流,而标准金属线的载流能力仅为10 nA / nm^ 2。

3、出色的散热性

热管理是电子设备性能的重要参数。碳纳米管(CNT)是众所周知的纳米材料,拥有出色的散热性能。此外,与硅相比,它们对I-V特性的温度升高影响较小。

晶体管应用中的CNT:CNFET

碳纳米管的带隙可以通过其手性(chirality)和直径改变,因此可以使碳纳米管表现得像半导体。半导体CNT可以是纳米级晶体管器件沟道材料的有利候选者,因为它提供了远超传统硅MOSFET的许多优点。碳纳米管传导热量类似于钻石或蓝宝石。此外,与硅基器件相比,它们的切换更可靠,功耗更低。

此外,CNFETS的跨导率(trans-conductance)比其对应物(counterpart)高四倍。CNT可与High-K材料集成,从而为通道提供良好的栅极控制。由于迁移率增加,CNFET的载流子速度是MOSFET的两倍。在相同的晶体管尺寸下,N型和P型CNFET的载流子迁移率类似。但在CMOS中,因为迁移率值不同,PMOS(P型金属氧化物半导体)晶体管尺寸大约是NMOS(N型金属氧化物半导体)晶体管的2.5倍。

CNTFET的制造是一项非常具有挑战性的任务,因为它需要精确和准确的方法。在这里我们讨论顶部门控(Top-gated)的CNTFET制造方法。

该技术的第一步始于将碳纳米管放置在氧化硅衬底上,然后分离各个管,使用先进的光刻来定义和图案化源极和漏极触点。然后通过改善触点和CNT之间的连接来减小接触电阻。通过蒸发(evaporation)技术在纳米管上进行薄顶栅(top-gate)电介质(dielectric)的沉积(deposition)。最后,为了完成该过程,栅极接触被沉积在栅极电介质上。

图4:碳纳米管FET的概念

CNTFET面临的挑战:

在商用CNFET技术的路线图上,存在许多挑战。他们中的大多数已经得到一定程度的解决,但其中也有一些尚未得到克服。在这里,我们将讨论CNTFET的一些主要挑战。

1、接触电阻

对于任何先进的晶体管技术来说,晶体管尺寸减小而带来的接触电阻的增加是他们面对的主要性能问题。由于晶体管的按比例缩小,接触电阻显著增加,这就带来晶体管性能下降。到目前为止减小器件触点的尺寸带来执行量(execution)大幅下降,这是硅和碳纳米管晶体管技术面临的挑战。

2、碳纳米管的合成

CNT的另一个挑战是改变其手性(chirality),使其表现得像个半导体。合成的管(synthesized tubes)具有金属和半导体的混合物。但是,由于只有半导体元件有资格成为晶体管,因此需要发明新的工程方法,在将金属管与半导体管分离时获得明显更好的结果。

3、开发非光刻工艺,将数十亿个这些纳米管放置在芯片的特定位置上,这构成了极具挑战性的任务。

目前,许多工程团队正在对行业和大学中的CNTFET器件及其逻辑应用进行研究。在2015年,一家领先的半导体公司的研究人员成功地使用“紧密接触方案”(close-bonded contact scheme)将金属触点与纳米管结合起来。他们通过在管的末端放置金属接触并使它们与碳反应形成不同的化合物来实现这一点。这项技术帮助他们将触点缩小到10纳米以下而不影响性能。

Gate all around FET:GAAFET

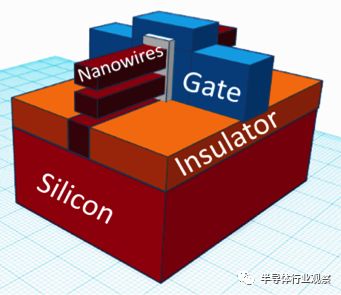

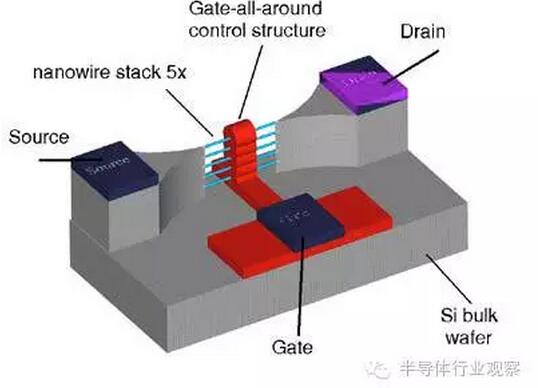

未来的潜在晶体管结构之一是GAAFET(Gate all around FET)。Gate-all-around FET是FinFET的扩展版本。在GAAFET中,栅极材料从四个方向围绕沟道区域。在简单的结构中,作为沟道的硅纳米线被栅极结构“包围”。垂直堆叠的多个水平纳米线结构被证明非常适合于提高每个限定区域的电流。图5中展示出了多个垂直堆叠的gate-all-around硅纳米线的概念。

图5:垂直堆叠的纳米线GAAFET

除硅材料外,还可以使用一些其他材料,如InGaAs,锗纳米线,借助这些材料能获得更好的移动性。

在复杂的栅极制造,纳米线和接触方面,GAAFET存在许多障碍。其中一个具有挑战性的工艺是从硅层制造纳米线,因为它需要一种新的蚀刻工艺方法。

最近,位于鲁汶的研发公司声称,他们在直径为10纳米以下的纳米线上使用GAAFET在通道上实现了出色的静电控制。去年,一家领先的半导体公司推出了一款5nm芯片,该芯片采用堆叠纳米线GAAFET技术,在50mm^2芯片上集成了300亿个晶体管。据称,与10nm节点相比,该芯片性能提高了40%,在相同性能下功耗降低了70%。

化合物半导体

继续晶体管微缩的另一种有希望的方法是选择表现出更高载流子迁移率的新型材料,而拥有来自III、V族成分的化合物半导体与硅相比,明显拥有更高的迁移率。其中一些化合物半导体实例是铟镓砷(InGaAs),砷化镓(GaAs)和砷化铟(InAs)。根据各种研究,化合物半导体与FinFET和GAAFET的集成在更小的节点处表现出优异的性能。

化合物半导体的主要问题是硅和III-V半导体之间的大的晶格(lattice)失配,导致晶体管沟道的缺陷。有一家公司开发了一种含有V形沟槽的FinFET进入硅衬底。这些沟槽充满铟镓砷并形成晶体管的鳍片。沟槽底部填充磷化铟以减少漏电流。利用这种沟槽结构,已经观察到缺陷在沟槽壁处终止,从而能够降低沟道中的缺陷。

结论

从22nm节点到7nm节点,FinFET已被证明是成功的,并且它还可以继续缩小到另一个节点。但我们也应该看到,除此之外,还存在各种挑战,如自加热,迁移率降低,阈值平坦等。

我们已经讨论了碳纳米管的优异运动特性,散热性,高载流能力,这将为替代现有硅技术提供了有前景的解决方案。

随着水平纳米线的堆叠打开“第四栅极”,Gate-all-around晶体管结构也是替换FinFET垂直Fin结构以获得良好静电特性的良好候选者。

虽然目前尚不清楚技术路线图中的下一步是什么。但是可以肯定的是,在未来的晶体管技术中,必须改变现有的材料,结构,EUV(极紫外)光刻工艺和封装,才能继续延续摩尔定律。

-

半导体

+关注

关注

335文章

28287浏览量

229471 -

晶体管

+关注

关注

77文章

9905浏览量

140114 -

化合物

+关注

关注

0文章

21浏览量

8342

发布评论请先 登录

相关推荐

5nm的晶体管会是什么样?

晶体管使用的判定方法

从7nm到5nm,半导体制程 精选资料分享

什么是鳍式场效应晶体管?鳍式场效应晶体管有哪些优缺点?

台积电2020年3月开始量产5nm工艺,晶体管密度提升最多80%

新型垂直纳米环栅晶体管,或是2nm及以下工艺的备选

Intel放弃FinFET晶体管转向GAA晶体管 GAA工艺性能提升或更明显

关于5nm以后的晶体管选择的方法分析

关于5nm以后的晶体管选择的方法分析

评论