苹果于近日召开了手机和手表发布会。按照苹果“一年新品,一年改良”的作风,在继去年发布了引领风潮的iPhone X后,今年苹果在发布会上发布的产品主要是去年的改良版本。虽然并没有太多惊喜,但是我们仍然能看到苹果产品背后的逻辑,并预测相关芯片技术的发展路径。

传感器加时尚——苹果可穿戴设备的核心壁垒

发布会上首先发布了Apple Watch 4。不得不说,Apple Watch系列是可穿戴设备中时尚感最强的,外观设计非常得体,从而能够走进大众而不仅仅是极客的玩具。

在这次发布的Apple Watch 4中,除了处理器更新换代计算能力加强之外,最主要的设计改进来自于传感器的使用。首先,Apple Watch 4中使用了下一代加速度传感器,将加速器传感的动态范围提高到了原来的两倍,最高加速度可以测到32g,此外,采样速度也提升到了原来的8倍。采用加强版的加速度传感器,Apple Watch 4能够检测到人摔倒的动作,一旦检测到摔倒将会提示拨打急救电话。

除了升级的加速度传感器之外,Apple Watch 4另一个亮点是心电图ECG传感器。在上一代手表中已经包含了使用LED做心率传感器,而在Apple Watch 4中则更是加入了ECG,从而能帮助检测心脏房颤。Apple Watch 4的ECG功能实现是由表盘底部和表冠上的两个电极实现的。在测量ECG时一个电极自然贴近手腕,而另一只手的手指放在表冠上持续30秒,在这30秒内ECG传感器电极会发射微电流并检测返回信号,从而完成ECG的测量,并把ECG测量结果储存到Health App中,方便健康管理。值得一提的是,Apple Watch的ECG功能已经通过了FDA认证,因此其测量结果可以作为医生诊断的辅助依据。

Apple Watch 4中的传感器目前主要还是针对热爱运动的人群,加速度传感器可以在运动摔倒时及时报警避免二次受伤,而ECG则可以在运动中感觉不适时及时诊断。在未来的人体传感器中,最重要的一个特点就是能实现持续测量并获得连续信号,这也将是未来精确化医疗的重要条件。

在发布会上,苹果请到了美国心脏协会的主席Ivor Benjamin医生,Benjamin医生表示目前许多病人的心脏病信号往往并不发生在就诊时,从而为心脏病的诊断带来了困难。苹果的ECG测量功能则可以看作是人体生理信号持续测量的雏形,至少可以在任何时刻用户都可以主动开启测量过程而无需去医院并将ECG数据记录下来,从而能够帮助医生诊断。

Apple Watch 4的传感器功能是否真正实用还有待观察,但是这也是苹果强化Apple Watch中传感器成分的重要举措。要知道之前Apple Watch的定位是一个时尚手表搭配个人助手,能完成简单的通话、短信等辅助功能,传感器并非其最大的卖点。但是随着其他公司的可穿戴设备逐渐跟上,Apple Watch必须树立起除了设计精美之外的其他竞争壁垒,而传感器看来就是苹果的尝试方向,而且我们可望在未来看到苹果把传感器的针对人群从运动人群推广到更多的普罗大众,让更多人能享受传感器带来的便利。在Apple Watch 4发布之后,预计我们也会看到市面上出现许多跟随者发布拥有类似传感功能的便携式设备,这样我们的数字化健康管理时代可望将会在技术逐渐成熟后真正来临。

A12 Bionic处理器部分:中规中矩的继承者

本次发布会中,大家关注的焦点之一可谓就是苹果新手机中的SoC处理器了。本次苹果发布的A12 Bionic可谓中规中矩,是继华为之后第二个发布7nm手机芯片的公司。A12总共包含60多亿个晶体管,集成了6核CPU以及4核GPU。在6核CPU中,有两个是“性能内核”(类似ARM架构中的大核),在执行游戏等场合提供高性能;另外四个是“能效内核”(类似ARM架构中的小核),在上网收发邮件等常规操作中提供较长的待机时间。

相对于上一代SoC,A12的大核速度快了15%,功耗节省了40%;而小核则把功耗降低了50%。在这里我们可以看到随着半导体工艺进步,使用7nm的处理器速度相对于使用上一代半导体工艺的处理器仅仅快了15%,但是功耗降了40-50%,可见半导体工艺的进步在7nm节点对于性能的帮助已经很有限了(尤其是15%的性能提升中还包括了芯片设计改进带来的提升),而对于功耗还是有较大帮助。

A12 媒体处理部分:AI结合AR的战略

A12的CPU以及GPU部分可谓是意料之中,而A12的Neural Engine和ISP部分则成为其中的亮点。可以说,苹果下一代手机与其他手机相比最大的差异点可能就是AI和AR的结合。

随着人工智能的概念大热,AI已经接着这股东风进入了手机,如华为与去年秋天就发布了第一款以人工智能为卖点的手机。然而,目前大热的AI最主要还是一种工具,例如可以从大数据中提取规律,从图像中识别特定物体等等,而手机目前来说并不缺AI作为工具带来的提升。因为手机的工具属性不强,因此直接把AI搬到手机的效果并不能算太好,至少很难成为一个爆点。具体来说,之前手机结合AI的主要卖点是拍照超分辨、智能场景识别、智能任务管理等等,这些特性属于锦上添花,但是很难说有消费者会冲着这些AI相关的特性而购买。归根到底,AI起的作用应当是为合适成为卖点的特性赋能,而不是自己试图成为卖点。

在苹果的规划中,这个卖点特性就是基于摄像头的AR应用,而AI则能作为赋能者带来独一无二的玩法。在发布会上苹果演示了多个AR+AI的例子,其中最有趣的App是Home Court,可以帮助用户在打篮球时通过摄像头自动识别投篮的类型、手臂角度、跑动速度、投篮角度等等,并将这些信息叠加在实时真实场景上实现AR的效果。在这些自动识别的背后则是复杂的AI算法,包括人体姿势识别和物体识别等。这样的安排也完美符合“AR做卖点,AI做赋能”的策略。

AR作为一种新媒体在具体应用上可以有很大的想象空间,例如可以作为一个新的信息入口在日常真实场景中叠加额外信息(例如识别出场景中的商店名并上网搜索实时将大众点评上的评分显示在商店上,这其实和发布会上苹果演示的Home Court原理很类似),也可以作为人际互动的工具实现telepresence虚拟现场(例如未来facetime中可以把对方的模型叠加在真实场景中仿佛他就在你身边),还可以作为游戏的新类型。可以说AR大概就是2007年的触摸屏——技术已经完全成熟,就等应用上出现愤怒的小鸟之类的爆款点燃消费者的热情了。

在A12 SoC中,对于AR的硬件支撑除了CPU、GPU做渲染之外主要就是Neural Engine和图像处理ISP。如前所述,苹果的AR背后需要AI算法的支持,因此苹果放上了8核neural engine模块,能实现5TOPS的神经网络相关高速计算,完成算法的实时演算。相比上一代A11中neural engine的0.6TOPS快了8倍不止,可见苹果对于AR+AI的决心。此外,ISP也非常重要,如运行双摄像头相关算法实现景深识别等也将成为AR应用中的重要部分。

总结与展望:再下一代苹果手机芯片将会如何发展?

从我们之前的分析中,我们可以发现苹果对于未来的布局重心在于AR上。根据这样的结论,我们可以预测再下一代苹果手机芯片的一些发展可能性。

首先,CPU和GPU部分还将继续加强,但是随着摩尔定律接近尾声,CPU和GPU的性能提升可能不会太多,主要集中在功耗的优化上。为了满足应用的性能需求,硬件上更有可能做的是在SoC上集成专用计算单元,而非强行提升CPU/GPU的性能。

此外,ISP作为AR相关的重要模块,可能会有新的模块和功能加入。例如为了实现AR中需要的定位、位置关系建模等,往往需要计算光流(optical flow),效率最高的办法就是在ISP中加入光流的专门计算模块。事实上Nvidia用于自动驾驶的SoC Xavier中就已经包含了专用光流处理单元,因此苹果在未来也有可能会根据AR应用的需要而加入类似模块。

在AI方面,neural engine一定会继续进化,其提升幅度未必做到一次8倍这么多,但是两到三倍的提升还是可以预期的,同时也可能会加入稀疏矩阵运算、网络压缩等高效计算特性。

AR方面另一个可能的需求是传感器。为了实现手势识别和场景三维建模,在手机的背部安装ToF传感器将是最好的选择,而iPhone下一代在背部安装ToF传感器的传闻事实上已经出现很久了。除此之外,为了实现室内定位等AR需要的需求,惯性传感器也可能得到更新换代。

-

芯片

+关注

关注

454文章

50689浏览量

423015 -

摩尔定律

+关注

关注

4文章

634浏览量

78982 -

加速度传感器

+关注

关注

12文章

471浏览量

55140

发布评论请先 登录

相关推荐

详细解析vivado约束时序路径分析问题

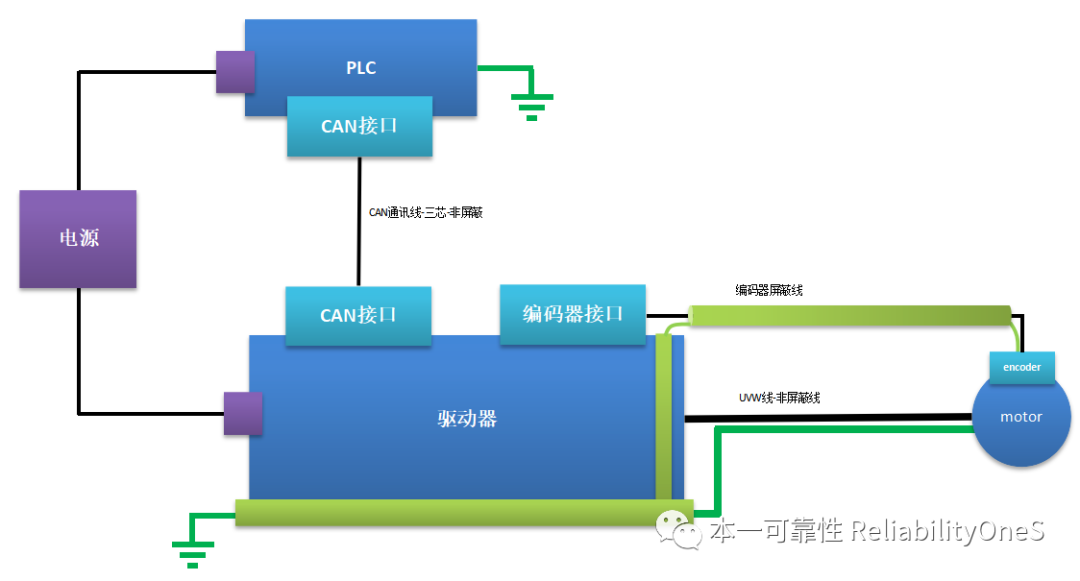

驱动器共模电流路径与数学模型分析

芯片失效分析简单介绍

网络数据集进行一个最短路径分析的例子

ArcGIS的路径分析

一文教你进行PCB设计过程中的回流路径分析

高速PCB设计——回流路径分析

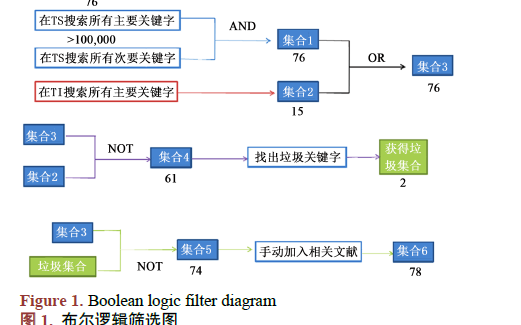

如何使用WOS进行负面口碑发展之路径分析

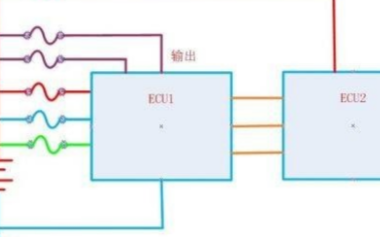

汽车电子系统中潜在路径分析技术的探讨

散热障碍与散热路径分析资料下载

基于路径分析和关系描述的知识图谱补全

时序路径分析提速

关于苹果芯片的发展路径分析和介绍

关于苹果芯片的发展路径分析和介绍

评论