在存储器中直接添加数据处理功能正在引起人们的重视,尤其是那些数据量巨大、在各类存储器和处理器之间来回传输数据需要耗费太多的能量和时间的应用。

在过去的十年中,将处理器添加到存储器的想法断断续续出现在人们的脑海中,人们将其作为未来可能的发展方向,但这被认为是一种昂贵且未经测试的器件微缩替代方案,从而遭到了摒弃。如今,由于热效应、各种类型的噪音,以及飞涨的设计和制造成本,微缩的效益减少了,所有的选择都摆上了桌面。尤其是汽车中的计算机视觉应用,因为此时激光雷达和摄像传感器将产生视频流;还有人工智能/机器学习/深度学习领域,因为此时需要快速处理大量数据。

AMD公司客户产品首席架构师Dan Bouvier表示:“如果你能在存储数据的地方处理数据,效率就会高得多。如果你必须要跨越链路,就会消耗大量功率,尤其会占用大量I/O。这会让PHY无法微缩。而且此处的封装技术太昂贵,无法进入更精细的接点间隔(bump pitches)。而你当然希望尽可能紧密地压缩。如果你使用的是异构处理器,那么本地电源管理就容易很多。 ”

这在数据中心中非常现实,就像在自动驾驶汽车和其他边缘设备中一样,而且这远非惊人的新发现。AI/ML/DL和视频流都不是新技术。但随着它们开始跨越多个市场,涉及功率和延迟的独特挑战正在出现。简而言之,需要处理的数据量预计将超过微缩所带来的性能和功耗方面的效益,而解决这一问题的唯一方法是通过架构改进和软硬件协同设计。

Babblelabs公司首席执行官Chris Rowen表示:“自从计算机出现以来,平衡内存带宽和计算带宽一直是计算机系统架构中的核心问题。甚至在50年前,人们就说,‘我需要以一种通用的方式逐个字节进行运算。’”

这些年来,这个方程式并没有显著改变,改变的是更高效地实现这一点的方法。例如:

将多次运算组合到一个周期中;

通过缓存或降低计算精度,改变数据在处理器和存储器之间移动的频率;

缩短处理器和存储器之间的距离,同时确保有足够的带宽。

上述三个领域的工作都在进行中,并且都大有希望。但是减小处理器和存储器之间的距离在许多方面都提出了有趣的挑战。

Rambus公司首席科学家Craig Hampel表示:“从技术的角度看,减小距离当然是可行的。而且它适合在神经网络训练中增加权重的需要,因为你无法承受延迟。问题出在经济上。如果你看看DRAM,就会发现位元是按照一种非常规则的方式组合的,因此它具有成本效益。3D的目标是缩小这些距离,2.5D肯定也有帮助。但这两种方法都使热问题更难以解决,而且更难以测试。 ”

由美光和三星开发的Hybrid Memory Cube提供了一个案例,通过在3D配置中将存储器堆叠在逻辑器件上,并使用硅通孔(TSV)连接不同层,从而实现距离的减小和数据吞吐量的提升。

Kandou Bus公司首席执行官Amin Shokrollahi表示:“人们对直接访问存储器非常感兴趣。问题是,你必须能够构建它,这样你才能进行正常的编程。软件和硬件同样重要。”

这是一个经济上特别恼人的领域。Shokrollahi说:“Hybrid Memory Cube没有成功的原因之一是没有第二个来源。HBM(高带宽内存)更为简单,但它提供了对所有存储器的访问,而且它是多源的。HBM封装还可以支持更多的层,而且你可以非常轻松地冷却它。因为如果你将处理器封装在存储器中,它会变得非常热。”

一种可能的解决方案是限制处理器和存储器的大小。在上月举行的Hot Chips 30会议上,总部位于得克萨斯州奥斯汀的初创公司Mythic介绍了一种新的矩阵乘法存储器架构,旨在用于AI /机器学习市场。Mythic的方法是在flash存储器中进行模拟计算以提高性能。

Mythic公司的首席技术官Dave Fick表示:“我们将使用flash阵列中的flash晶体管来表示权重矩阵。我们采用这种flash阵列,然后将其打包成小块。我们有基于小块的架构,其中每个小块都有一个这样的存储器阵列,还有其他支持重新配置和中间数据存储的逻辑。SRAM提供中间数据存储,因此在中间阶段我们将数据存储在SRAM中。我们有RISC-V处理器,用于在小块内提供控制。我们有路由器,实现与相邻的小块通信。然后有SIMD(单指令,多数据)单元,它提供的运算不是矩阵乘法。”

这里的局限是专业化,因为flash晶体管不能快速编程。Fick说:“你需要拥有一套固定的应用,但这对于边缘系统来说非常典型。我们可以通过将不同的区域映射到不同的应用来支持多个应用,因此我们可以一次支持多个应用。”

图1:Mythic公司提出的架构,应用于深度神经网络。 (来源:Mythic / Hot Chips 30)

制造挑战

还有其他问题需要解决。减小信号在存储器和逻辑器件之间传输的距离会带来热量和成本方面的挑战。但是直接在存储器中构建处理功能中会增加集成和兼容性问题。

OneSpin Solutions总裁兼首席执行官Raik Brinkmann表示:“最大的问题是,存储工艺和逻辑工艺无法结合在一起,因此你无法合理地将这些器件组装在一起。这引发了制造方面的另一波创新浪潮。例如,对于单片3D架构,逻辑层和存储层之间有非常细的连线连接着两层硅片。存储器中的计算基本就是这个样子。”

在这一点上,没有人确切知道这种方法在制造中会产生怎样的收益。

Arm公司研究员Rob Aitken表示:“这增加了一系列全新的挑战。这种工艺中,有趣的架构创新之一就是像斯坦福大学那样使用基于像素的工艺系统。在这样的系统中,像素彼此相对独立并且存在于2D表面中。问题是,当你把两个晶圆放在一起时,收率可能不同于单一晶圆的情形。例如,‘这个晶圆的收率是75%,那个晶圆的收率是75%,当我把它们放在一起时,收率是30%。’实际上,你必须建立一个系统,让三维堆叠中隐含的冗余与你一起工作,而不是与你作对。但即使你不使用单片3D,你只是想在存储器中或者存储器附近进行计算,那也会涉及到数据移动问题。如果你的系统需要移动数据,那么处理器的精妙程度和速度并不重要,因为这不是限制因素。”

设计挑战

这在设计方面引发了一系列其他挑战。

eSilicon公司营销副总裁Mike Gianfagna表示:“这不仅仅是如何在设计中添加更多的东西,部分原因还在于你如何改变芯片设计的传统方法。近存储器队列需要复杂的并行设计。”

这还需要深入了解如何在设计中使用各种类型的存储器。AMD公司的Bouvier表示:“一个重要的死对头是虚拟内存子系统,这是用反常的方式移动数据,相当于二次转化。 ”

但Bouvier指出,对于不同类型的芯片如何利用DRAM有不同的衡量标准。Bouvier表示,对于discrete GPU,DRAM的运行效率在90%左右。对于APU或CPU,它的运行效率在80%到85%之间。

对于AI/ML/DL应用,这在推理方面尤为重要。

Babblelabs公司的Rowen表示:“英伟达之所以如此强大,并不仅仅是因为它们有并行架构,而是因为它们有大量的内存。推理过程的一个显着不同之处在于,每个字节的内存通常有数百次运算。所以这个问题的不同之处在于你通常不用关心内存,至少对于推理而言是如此。你可以抛出大量与问题密切相关的计算,而不会出现内存瓶颈。导致诸多创新的原因之一是,人们推出了非常密集的计算架构和粗粒度阵列,得到的反应是‘这很好,但没有具有这些特征的问题。’他们中的大多数都失败了,因为他们没有足够的内存带宽。但现在,我们遇到的问题确实存在带宽不成问题的特征。”

这使得在内存中或非常接近内存的地方添加内存更加引人注目。尽管这还不是一个确定的赌注,但除非经过严肃的讨论,否则它不会被抛弃。

-

存储器

+关注

关注

38文章

7481浏览量

163751 -

数据

+关注

关注

8文章

6989浏览量

88932 -

数据处理

+关注

关注

0文章

594浏览量

28554

发布评论请先 登录

相关推荐

一个串口数据处理的VI程序 实现对数据文件中的读取、验...

hmc5883的坐标数据处理?

【教学基地】labview大数据处理(初步分析部分)

基于DDR3存储器的数据处理应用

电流数据处理与分析相关资料分享

基于MatrixVB光电实验数据处理

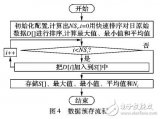

基于部分存储和选择性加载的数据处理算法

关于存储里的数据处理分析

关于存储里的数据处理分析

评论