历经数十年的发展之后,集成电路产业发生了很多变化。例如芯片公司从最早的IDM为主发展到现在的Fabless成为主流。再如凭借CPU豪占半导体企业营收头把交易的Intel被依仗存储壮大的三星赶下马。又如之前被集成电路产业人员奉为金科玉律的摩尔定律,因为材料和技术的限制,逐渐失去了往日的风采。另外还有技术的更迭、材料的革新和架构的演变,集成电路产业开始呈现出了全新的形态。

在这个新技术和创意频发的时代,集成电路产业将迎来新的时代。在近日于南京举办的“2018中国集成电路技术应用研讨会暨南京国际集成电路技术达摩论坛”上,来自产业研的专家就集成电路产业的未来发展,给出了他们的观点。

许居衍:AI芯片的未来靠架构创新

根据摩尔定律的定义,芯片的集成度每18个月会提升一倍,性能也会提升一倍,与此同时,单晶体管的成本就会下降。换句话说就是每一美元买到的芯片性能提升一倍。这个在过去几十年基本都是通过晶体管微缩实现的。但在多方因素的影响下,制程推进已经脱离了摩尔定律的规律。业界围绕着摩尔定律的生死,也有了很多的讨论。

中国工程院院士许居衍院士认为,摩尔定律已经死了,这就使得类似AI这样对芯片性能要求比较高的应用给集成电路带来巨大的压力。他指出,虽然英伟达、谷歌和寒武纪等一众厂商都投入了AI芯片市场,无论是FPGA或者ASIC,都凭借各自的优势,在AI市场并获得了不错的表现,其中尤以英伟达凭借GPU在AI训练市场表现出色最为亮眼。但他认为,片上系统的存在让计算变得无处不在,算力的持续提升让它到达了一个拐点(Volta GPU的性能与2014年的超级机差不多)。在这个环境下,芯片需要从架构上创新,才能满足性能需求。许居衍院士强调。

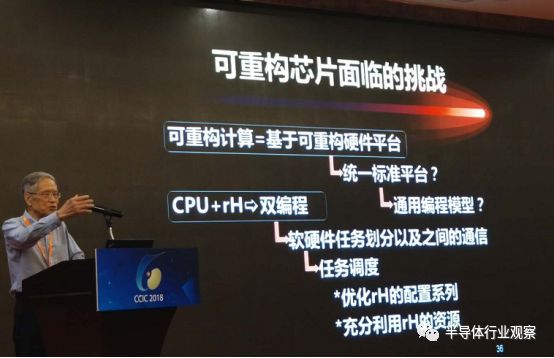

在他看来,芯片的编程技术在过去的发展中经历了几波浪潮,第一波就是封装编程,那时候的“芯片”是算法固定、资源固定;到后来英特尔制造出MPU之后,则迎来了软件编程,这时候任何一个算法进来,芯片都能应付得来,这时候的特点是算法可变,资源固定; 之后就迎来了算法可变、资源可变的硬件编程。但他认为,受限于硅技术瓶颈和冯诺依曼架构的指令流导致算力上不去的问题,未来的芯片架构需要创新。系统视野、多片与堆叠架构、异构架构就是许院士看好的方向,用户可重构SoC则是他推崇的一个选择。

许居衍院士表示,可重构的SoC性能能够超过FPGA,且非常灵活、安全、低成本,这就使他能够从资源配置上满足更多的需求,是我们应该关注的发展方向。而国内的也有了清华Thinker和南大RASP可重构芯片,这是值得称赞的。但许院士也强调,可重构计算面临多样化的挑战,需要我们正确对待。

张卫:半浮栅器件是存储器的新选择

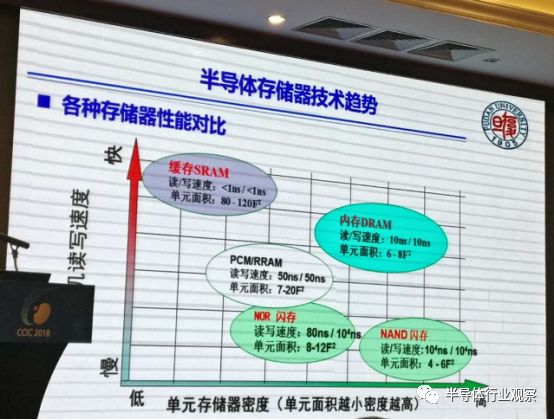

最近两年,因为疯狂涨价,大家对Flash和DRAM为代表的存储器市场有了更多的关注。据复旦大学微电子学院执行院长张卫介绍,2017年,全球存储器的销量为1240亿美元,同比增长了61.5%。这主要是由DRAM和NAND Flash贡献的。

从数据上看,存储器的使用量正在攀升。从应用上看,存储也是所有产品必须的。但是存储却面临这各样的瓶颈。以DRAM为例,这个最大的单一集成电路产品(去年创造了700多亿美元的营收)因为受到了电容瓶颈等限制,存储电容越来越小,导致数据保留时间缩短,功耗增加。另外,由于阵列晶体管驱动电流太小,漏电流也增大了。各种各样的原因综合,使得原本和逻辑器件一样遵循摩尔定律微缩的DRAM一直停留在17nm。

看到这种趋势,业界很多人已经PCM、MRAM和RRAM这些新型存储器探索。但因为各自的问题和限制,都没取得太大的突破。

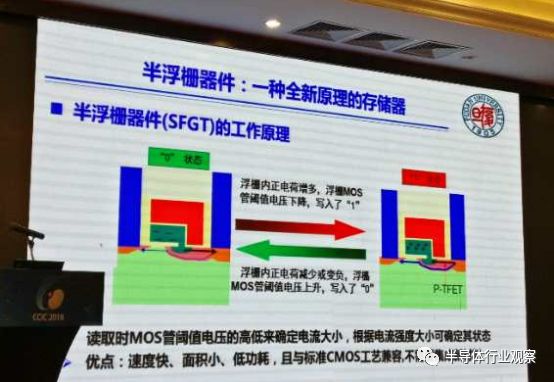

譬如颇受大家欢迎的RRAM,因为导电filament行程的随机性的存在,直接就制约了RRAM的产业化。为了推动整个产业发展,张卫团队推出了一种称为半浮栅器件的产品。

我们平时所用的是“非挥发性存储器”,意思就是芯片在没有供电的情况下,信息仍能被保存而不会丢失。这种器件在写入和擦除时都需要有电流通过一层接近5纳米厚的氧化硅介质,因此需要较高的操作电压(接近20伏)和较长的时间(微秒级)。张卫团队则巧妙地通过一个隧穿二极管把浮极和栅极连起来,用隧穿二极管来控制对浮栅的充放电,从而构成了一个存储器,这就是他们所说的半浮栅器件。这种器件具有速度快、面积小、低功耗,且与标准CMOS工艺兼容,不需要集成新材料等优势,在海内外获得了高度认可。

张卫表示,目前他们已经基于上海华为微电子公司的40nm工艺平台,完成了8M基于半浮栅器件的高速低功耗缓存芯片的设计与制造,测试结果也达到了设计要求。在他看来,这个产品将会是我国存储发展的一个新机遇。

宋继强:摩尔定律将继续有效

无论其他人怎么看摩尔定律,英特尔方面始终对其充满着信心。在日前的大会上,英特尔中国研究院院长宋继强继续强调:“于摩尔定律本身,我们可以把他看成是经济上的一个观察。它的经济效益还是继续存在,虽然这个速度不会像以前那么快。但我们认为,这个经济效益将持续存在”。坚信CMOS还能缩放,是他对摩尔定律还有信心的一个重要原因。

宋继强表示,现在的CMOS微缩还远远没有到物理极限这个程度,依然可以继续往下走。但和以前不一样,现在的微缩碰到了如何实现大批量、高精度芯片生产的问题。而新的3D工艺技术,新的材料将会成为继续微缩的动力。如三五族晶体管、纳米线晶体管和铁电体就是当中的选择。

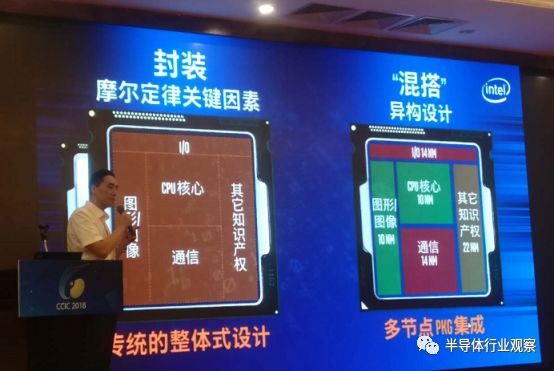

不过他也指出,虽然这些新的材料有很好的特性,但目前来说还没有一个能够作为CMOS的替代品。但为了获得性能提升,英特尔通过异构的方式把CMOS等器件整合在一起,同时再加上一些新算法功能的处理、数据处理模块、清晰的处理架构去获得性能上的提升。获得经济效益的提升,延续摩尔定律。

MIX & MATCH (混搭)则是英特尔延续摩尔定律寿命的另一个招数。

按照宋继强的说法,所谓混搭是把不同制程下的芯片放到一起,将它封装集成起来。这种技术可以根据需要封装不同的CPU核心、IO、GPU核心甚至FPGA、AI芯片,帮助英特尔灵活应对不同业务的需求,进一步提升经济效益。为了达成这样的设计,需要有很好的连接技术和功耗管理技术,而英特尔在上面已经有了很深的积累。

进一步增大硅片的面积,则是又一个新方向。

宋继强告诉半导体行业观察记者,把硅片从300毫米增加到450毫米虽然增加了单一硅晶圆的成本,但因为我们获得了更多芯片数量,综合计算下来,单个芯片的价格还是继续在下降,这也是符合摩尔定律的规定的。

来到新工艺方面,宋继强表示,由于在10纳米上采用了几种新的方法,目前已可以看到比较好的良率。在他看来,英特尔明年在10nm上将有更有高的良率,届时将有大批量的10纳米的产品面世。至于7纳米的话,基于10纳米的技术积累和经验,他非常看好英特尔未来的工艺走势。

-

集成电路

+关注

关注

5387文章

11516浏览量

361547 -

摩尔定律

+关注

关注

4文章

634浏览量

78982 -

AI芯片

+关注

关注

17文章

1877浏览量

34975

发布评论请先 登录

相关推荐

关于资深专家对于集成电路的未来分析

关于资深专家对于集成电路的未来分析

评论