多种趋势正在将FPGA推向两条截然不同的发展道路。

在第一条路上,FPGA不断优化,主要用于加速数据中心工作负载。 数据中心是大型供应商关注的下一个“圣杯”。

在另一条发展道路上,有传统的FPGA网络市场、蜂窝基站、国防、商用航空、工业4.0和医疗。 在这些应用领域,许多工程师认为他们正在被抛弃。 他们面临的发展挑战与大型供应商关注的数据中心焦点截然不同。 设计人员面临着越来越难以平衡的行为,因为他们试图在不牺牲性能和安全性的情况下,实现低功耗和低成本。

要想实现这种平衡,就需要以新的方式来看待FPGA,采用新的工艺技术选择、结构设计、收发器策略和内置的安全措施。这孕育出了一类新的、中等规模的FPGA,为传统FPGA开发人员提供了新的功能。

新的工艺技术选择

降低功耗同时优化中等规模FPGA成本的一种方法是:使用新的工艺技术。 例如,在28nm技术节点上使用Silicon-Oxide-Nitride-Silicon(SONOS)非易失性(NV)技术,其与相同或更小节点上的基于SRAM的FPGA相比,具有更低的功耗优势。 使用65nm及以上浮栅NV技术的上一代非易失性FPGA比SONOS昂贵。 鉴于浮动栅极技术需要17.5 V来编程使用消耗大量芯片面积的大型电荷泵,SONOS技术只需要7.5 V编程,因此电荷泵可以更小。 这项技术可以缩小芯片尺寸,并有助于提供更具成本效益的器件。

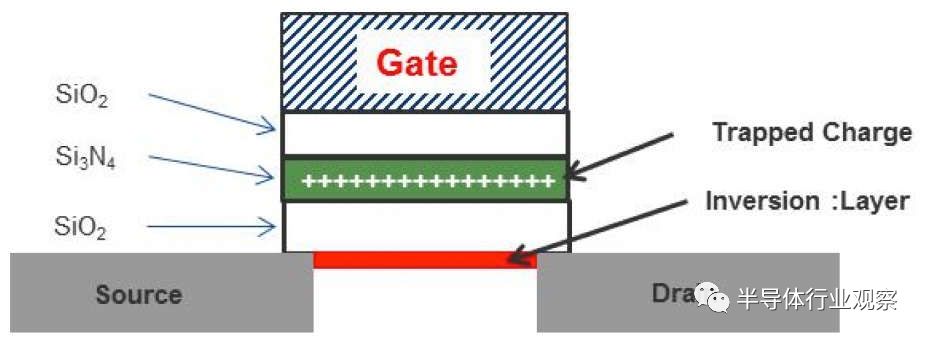

SONOS技术通过使用具有非导电氮化物电介质层(Si3N4)作为电荷存储单元的单个多晶硅晶体管堆叠(见图1)来实现这些优势。 使用这种方法,在底部氧化物中可能存在的任何缺陷附近,只有非常少量的电荷将流失。

由于储存的电荷在绝缘氮化物层中不可移动,所以大部分储存的电荷仍然保持原样,完好无损。 与浮栅技术相比,可以使用更薄的底部氧化物,并且可以用更低的编程电压(〜7.5 V)和更小的电荷泵进行编程。与SRAM存储单元相比,使用SONOS所需的晶体管数量更少。

图1:SONOS技术。 (来源:Microsemi)

SONOS技术通过使用包含N通道和P通道NV器件的推挽式单元来提高可靠性。 NV器件不处于数据路径,仅用于控制用作数据路径开关的标准晶体管。 这提供了很大的功能优势,因为NV器件阈值电压(Vt)的任何变化都不会改变开关电导。设备互动的方式充当了内置的准冗余,可防止产品在使用期间的性能下降。

功耗也会降低。 首先,SONOS NV FPGA配置单元启用两种不同的可编程“配置”状态,控制FPGA数据信号路径,关断和开启时优化开关器件以提供比标准晶体管低得多的漏电。 其次,SONOS技术可以将器件置于一种状态:将电源电压关闭至FPGA逻辑模块中的配置存储器,同时将用户的状态保存在低功耗锁存器中。 这降低了约三分之二的待机功耗。

SONOS还有两个重要的优势。 首先是“即时开”功能:因为FPGA逻辑配置单元在掉电后保持其状态,所以当电源返回时不需要重新加载FPGA设计代码,也不需要外部引导PROM。其次,与基于SRAM的FPGA中的配置存储器不同,该器件可由于中子轰击而翻转状态,SONOS器件的FPGA逻辑配置不受SEU影响。 SONOS NV电荷存储在氮化物电介质中,不容易受到中子轰击带来的电荷损失。

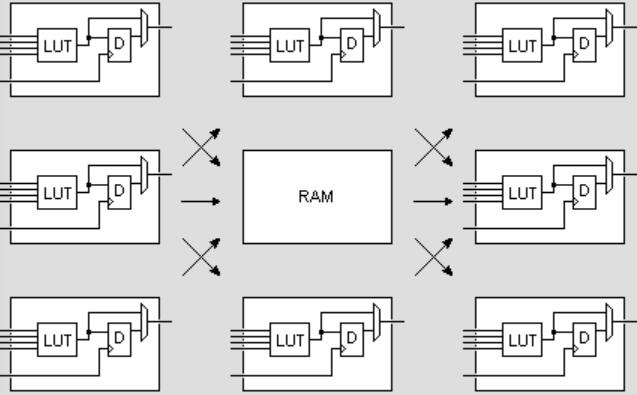

新的结构设计

另一种提高中等规模FPGA性能的方法是:改变可编程逻辑结构。 这使得器件能够满足主流性能要求,同时,静态功耗仅为SRAM FPGA的十分之一,以及总功耗的一半。

功耗和性能需要权衡考量。 例如,6输入LUT可提供一些速度优势,但4输入LUT是现代工艺技术中功率和成本优化FPGA的更好选择。 同时,随着工艺技术从65nm发展到28nm及以上,由于金属线和通孔电阻的缩放差,布线的延迟已成为逻辑延迟的主导因素。 拓宽金属线会增加芯片面积和成本。 因此,随着每一代后续的工艺技术的发展,集群间(inter-cluster)延迟将成为关键路径的首要问题,6输入LUT的速度优势将会减弱。 确保相邻LUT之间的快速直连可以减少集群内延迟,尤其是与先进的综合和布局算法相结合。 某些逻辑功能(如MUX树)会从直连中受益良多。

为了获得最佳效果,应该仔细优化FPGA系列的功耗性能折衷方案,以便核心逻辑电源电压略低于其制造过程的标称电压。 在28nm SONOS器件中,这意味着优化1.0V核心逻辑电源电压,在需要额外速度时可选择使用完整的1.05 V电源。

FPGA架构的最后一块是数学模块,它应该支持18位乘法累加操作。 通过提供具有完整19位结果和输入值级联链的预加法器,并通过确保数学模块支持精确的9位操作,包括9×9点积模式。 后者非常适合用于图像处理和卷积神经网络(CNN)。

FPGA收发器

收发器在优化FPGA成本,功耗和性能要求方面发挥着重要作用。 许多应用需要高达24个高速全双工收发器通道。 他们还需要SerDes收发器,可以支持250 Mbps到12.7 Gbps的波特率,以覆盖全系列的SDI,高达10Gbps的以太网,JESD204B转换器和其他应用。 优化收发器的一个主要优势在于降低从高端FPGA调整的更高速SerDes的性能,因为与降级的SerDes方法相比,它在所有波特率下的功耗都要低得多。

多种架构选择有助于降低FPGA收发器功耗,从使用半速率架构实现收发器到使用高度共享的传输PLL架构。 理想情况下,FPGA应该具有1~6个四通道收发器,最多可以有24个SerDes通道。 许多均衡功能允许更长距离,并在印刷电路板和背板中使用低成本材料。 特殊的锁相环(PLL)特性可为用户提供更多灵活性,从更灵活的时钟和波特率选择到简化的radiated-emission要求,以及更高的带宽选项。

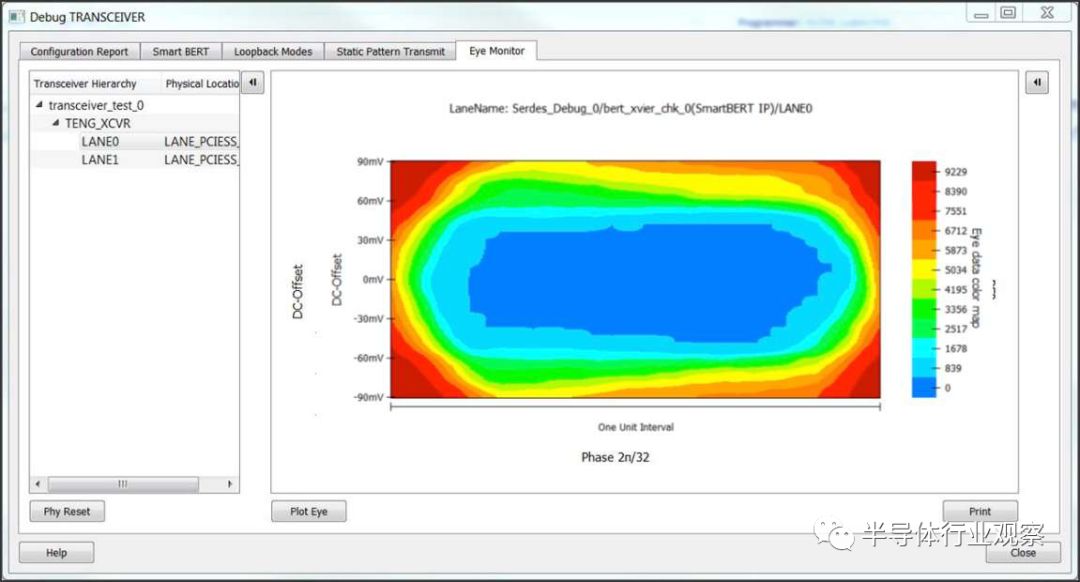

调试和测试也很重要,包括内置伪随机二进制序列(PRBS)发生器和检测器的可用性以及支持非直流耦合信号的IEEE 1149.6“AC JTAG”。 包括带调试软件支持的内置眼图监视器,设计人员无需示波器即可调试SerDes。 人们可以实时优化DFE和CTLE参数,并调用最终产品的理想设置(参见图2)。

图2:SerDes眼图监视器智能调试软件

解决安全挑战

目前,设计的安全性存在许多威胁。 从用户设计IP到制造过程的所有内容都可能受到影响。

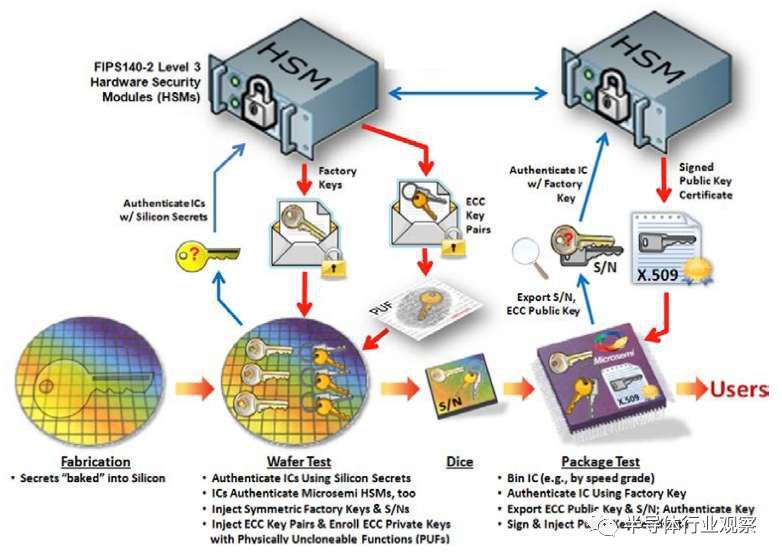

关键的安全技术和性能包括可信任的硬件roots,强大的加密技术以及每个阶段的顶级密钥管理,以及内置被动和主动对策以防止篡改的设备。 图3显示了使用唯一序列号、密钥和X.509公钥证书进行安全FPGA配置的最佳实现方法。

图3:设备证书信任链

有了这些组件,就可以解决设计和数据安全问题。 设计安全性要求FPGA使用制造商提供的密钥和证书,以及其他技术(从专利的差分功耗分析(DPA)对策到防止侧向信道攻击的技术),以保护用户的IP。 另一种提高设计安全性的方法是使用物理不可克隆功能(PUF)技术来生成硬件固有密钥。

数据安全性要求使用专用于核心NIST认证的FPGA用户的加密处理器,以实现许多最常用的加密算法,如AES,SHA 2,ECC,RSA和DH,并包含加密级TRNG。 与向FPGA架构添加加速器相比,用户加密处理器适用于许多应用,从而降低成本(面积、功耗和其它相关)。

市场对需要成本优化的中等规模FPGA的需求不断增长,在通信、国防和工业市场,对密度高达500K逻辑单元(LE)的情况下,要求功率密度显着降低。 一个新的发展路线图已经出现,它将新的工艺技术和结构设计与重要的收发器变化和安全特性相结合,使FPGA能够解决主流应用的成本、功耗、性能和安全要求,同时提供非易失性技术的所有优势。

-

收发器

+关注

关注

10文章

3524浏览量

106444 -

存储器

+关注

关注

38文章

7552浏览量

164810 -

数据中心

+关注

关注

16文章

4946浏览量

72628

发布评论请先 登录

相关推荐

如何选择满足FPGA设计需求的工艺?

FPGA架构的功耗及影响功耗的用户选择方案

FPGA选择和系统设计架构

关于Vivado时序分析介绍以及应用

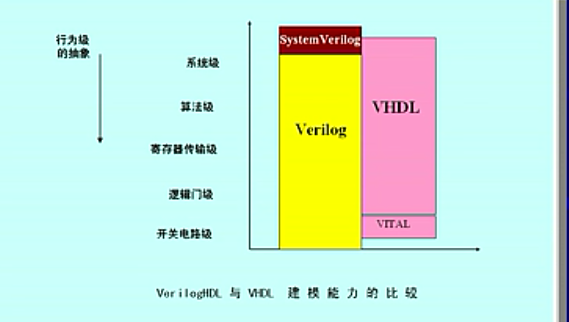

FPGA视频教程之学习FPGA选择verilog还是vhdl详细资料说明

关于FPGA的新变化的分析和介绍

关于FPGA的分析和介绍以及应用

关于基于FPGA的图像FFT滤波处理的分析和介绍

关于FPGA与GPU分析介绍

详细介绍关于FPGA开发板内部ram是如何操作的

为FPGA选择合适的电源稳压模块

关于FPGA的开源项目介绍

关于FPGA的新选择的分析介绍

关于FPGA的新选择的分析介绍

评论