目前,几个晶圆厂工具供应商正在推出新一代自对准图案化技术,以向10 nm/ 7nm及以上的新器件演进。

应用材料、Lam Research和INTEL正在开发基于各种新方法的自对准技术。最新的方法涉及采用多色材料方案的自对准图案化技术,该技术旨在用于在逻辑晶体管本身内开发新的finFET和结构。也有其他公司正在开发下一代晶体管和存储器的新方案。

用于形成逻辑和存储器的自对准图案化技术属于半导体制造中“图案化”的通用范畴。 图案化是在芯片上开发微小特性和图案的“艺术”。 其他技术也属于宽泛的“图案化”部分,例如极紫外( EUV )光刻和光学光刻等。

几年前开发的自对准技术,利用各种工艺步骤来确保结构彼此正确对齐。 一般来说,新的自对准技术分为两个部分 - 多重构图 ,以及自对准接触/过孔和其他结构。有人对第二部分使用不同的名称。 Imec将其称为“缩放增强器”,而应用材料公司将其称为“材料使能缩放”。

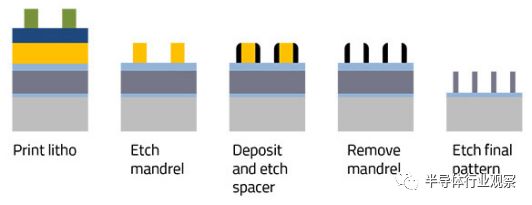

在多重图案化中,其思路是在工厂中使用一系列工艺步骤来缩放芯片的特征尺寸。 最著名的例子是自对准双重图案(SADP)和自对准四重图案(SAQP)。

除了多重图案化之外,芯片制造商还使用不同的自对准技术来开发晶体管内部的各种结构,例如接触和过孔。 业界将这些结构称为自对准接触和过孔。

举一个例子, Intel最近推出了10nm finFET技术。 采用自对准技术,英特尔在finFET内部集成了有源栅极(COAG)结构的触点。有其他公司正在开发完全自对准的过孔和相关结构。

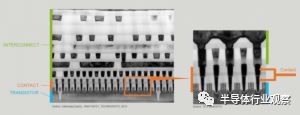

图1:标准触点与有源栅触点。 来源:英特尔

这些经常被忽视的技术正变得越来越重要。 “像COAG这样的自对准结构是缩放的关键,”英特尔高级研究员兼过程架构与集成总监Mark Bohr表示。“英特尔和行业内的其他厂商过去都采用了自对准功能,如自对准接触和自对准过孔,这些功能都需要实现缩放。”

自对准技术在工厂中使用各种工艺步骤,例如沉积、蚀刻和光刻。 其他方案更多的是以新的材料组合沉积/蚀刻为中心,根据设备而有所不同。 在图案化领域还有其他选择,包括直写电子束、定向自组装、EUV、光刻和纳米压印。

但为了帮助行业在自对准技术领域走在前列,半导体工程公司正在紧跟、研究多模式图案、接触/过孔和未来方案的趋势。

转向多重模式

该过程从光掩膜设施开始。 在这个流程中,芯片制造商设计一个IC,将其转换成文件格式,然后,基于该格式开发光掩膜。

光掩膜是给定IC设计的主模板。 掩膜开发后,它被运送到工厂并放置在光刻扫描仪中。

然后,将晶圆放置在扫描仪中的独立台上,晶圆上涂有光敏材料,称为光刻胶。 扫描仪通过掩膜投影光线,在晶圆上形成微小图像。

多年来,传统光刻是一个简单的过程。 光刻扫描仪使用单次曝光对晶圆上的特征进行成像。 这或多或少是单一模式的过程。 长期以来,业界认为传统的光刻系统将持续到45nm左右。 理论上,最新的光学技术--193nm波长光刻技术 - 应该以80nm线宽或40nm半线宽达到其物理极限。然后,在45nm处,芯片制造商应该转向极紫外(EUV)光刻技术,EUV使用13.5nm波长,在纳米尺度上图案化特征。

然而,EUV的开发比以前想象的更复杂,并且技术已经被推迟。 现在,EUV的目标是7nm和5nm。 由于延迟,业界开发了另一种解决方案,即通过多重图案化技术来延长当今的193nm波长光刻技术。

从单一模式转向多重模式并不容易。 多年来,该行业在光掩膜上使用了光学邻近校正(OPC)技术。 OPC使用微小形状或次分辨率辅助功能(SRAF)。SRAF被放置在掩膜上,这改变了掩膜图案,从而改善了晶圆上的可印刷性。

然而,在20nm处,SRAF在掩膜上变得太密集,使得在晶圆上印刷可辨别的特征更加困难,而这正是适合使用多重图案化的地方。

“在多重图案化中,原始掩膜的形状被划分为两个或更多,使得每个形状在其周围具有足够的空间,以使得OPC操作能够使其可印刷,” 西门子Mentor的DFM项目主管David Abercrombie在博客中说: “然后将每个掩膜分开打印,最终将整套原始形状成像到晶圆上。”

从22nm/ 20nm开始,芯片制造商采用两步法在晶圆厂实施了各种多重构图方案。 第一步是使用193nm光刻和多重图案在晶圆上构图微小线条。然后,线条被切割成小而复杂的图案。

对于这些产品线,该行业借鉴了存储器行业中使用的技术 - SADP和SAQP。 SADP / SAQP使用光刻步骤,以及附加的沉积和蚀刻步骤来定义间隔物状特征。 使用SADP / SAQP,芯片制造商可以将线宽扩展到40nm以上。

然而,这里有一个很大的挑战,就是将这些线条切成小图案。 为此,一些芯片制造商使用SADP和SAQP。

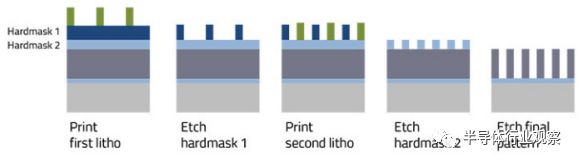

还有厂商使用双重图案化,这可以将线宽减少30%。 这个过程使用光刻和蚀刻来定义单个层。 这也被称为光刻 - 蚀刻 - 光刻 (LELE)。还有厂商使用三重图案化,这需要三次曝光和蚀刻步骤(LELELE)。

图2:自对准垫片避免了掩膜错位。 来源:Lam Research

图3:双重图案增加密度。 来源:Lam Research

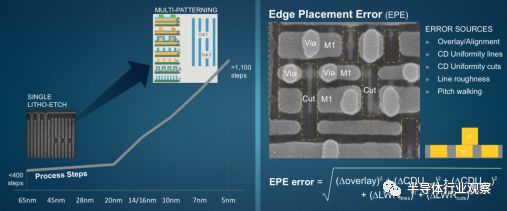

多次构图延长了IC的缩放比例,但同时也增加了复杂性。 首先,每个节点都有更多的流程步骤,这会转化为时间和成本。

设备功能在每个节点处变得更弱,这使问题更加复杂。 最重要的是,这些功能必须精确并且放置在设备每层的确切位置上。 28nm器件具有40到50个掩膜层。 相比之下,14nm / 10nm器件具有60层,并且该数量在7nm处预计会上升至80至85层。

总而言之,每个节点的挑战都在增加,这就增加了在这个过程中出现错误的可能性。 “我们可以通过乘法来制作更小的特征。 但将它们相对放置,是一个根本挑战。当您正尝试将多个图层彼此叠加时,可能会出现错误,“ 应用材料公司图案化技术总监Regina Freed表示。

在图案化处理中,目标是在精确的位置上设置微小的特征。 如果这些不精确,会导致不能对准,这通常称为边缘放置误差(EPE)。

EPE是IC布局的预期功能和打印功能之间的差异。 如果在生产流程中出现一个或多个EPE问题,则该设备会出现短路或收益率低下的情况。

EPE由数值表示,简而言之,EPE等同于各种度量的组合 - CD均匀性、覆盖度、线边缘粗糙度(LER)和变化。

图4:多重构图过程和EPE挑战。 来源:应用材料公司

有些流程可以轻松满足所需的EPE数值或预算, 但有时,更难的流程可能会超过EPE的目标水平,这将导致收益率下降。

解决方案

所以,对于10nm / 7nm及更高工艺节点来说,什么是最好的图案化解决方案? 哪一个会符合EPE的目标呢?

没有单一的解决方案可以满足所有需求。 与以前一样,芯片制造商根据复杂性、成本和其他因素选择特定的制造技术。

应用材料的Freed说:“以某种分辨率获取图案有多种方式,会有很多不同的选择。 你可以做SAQP,可以使用EUV /双重图案化,可以进行EUV光刻蚀刻 - 光刻蚀刻。 每个选项都有其优点和缺点。 客户可以综合使用这些技术。”

EUV是一种可能性,因为它有望减少流程中的步骤。 DSA , 多光束和纳米压印也是可能的。

自对准是另一种解决方案。 这些技术与其他晶圆厂工具协同工作,以帮助对齐特征。 例如,EUV可以与SADP / SAQP方案结合,用于多重图案化。

一般来说,该行业已经将今天的自对准技术扩展到10nm / 7nm,而使用传统方法变得具有挑战性。 “随着行业进入高级节点,与尺寸缩放相关的处理挑战变得越来越重要,” INTEL高级工艺工程师Eric Liu在最近的SPIE会议上发表的一篇论文中表示。

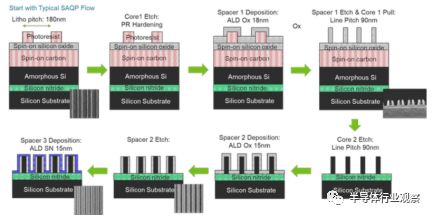

在这篇论文中,INTEL描述了一种新的SAQP方法,用来执行30nm线宽的线切割。 “线切割步骤中最具挑战性的模式是单线切割,且要求没有缺陷形成,”Liu说。

为此,INTEL使用多色材料设计了SAQP(这与用于多重图案化的多色掩膜布局不同。)

传统上,在SADP / SAQP中,流程涉及各种步骤和不同的材料,通常,每种材料具有相同的颜色。 问题在于,当使用传统方法以30nm线宽进行线切割时,INTEL计算出EPE预算超过了7.9nm的目标值。

INTEL的新方法是遵循具有各种光刻、沉积和蚀刻步骤的标准SAQP流程。 但是在这种方法中,基于蚀刻选择率,每种材料被分配不同的颜色,例如,该过程需要两条不同的生产线, 每条线都分配有不同的颜色,掩膜板被分配不同的颜色。

图5:从光刻到隔离层3沉积的2L1C的分步多色工艺流程。 来源:INTEL

简而言之,颜色可以作为流程中的指导,从而实现更精确的特征。 “如果用不同的材料制作长线条/空间图案中的其他线条,并且这些材料具有不同的蚀刻速率,则可以在蚀刻工艺中切割一条线条,而不用担心相邻线条是否因错位而损坏裁剪图案“,Fractilia的首席技术官Chris Mack在博客中解释说。

尽管如此,总体而言,多色彩多重图案化方法仍然需要权衡。 “ Lam Research技术总监Richard Wise表示:”我们已经将测试架构作为逻辑应用研发活动的一部分,通过构建具有不同颜色(材料)的线条,随机放置切割工艺可以使用选择性蚀刻工艺自动对准底层线条。 这可以有效地将这些削减的覆盖裕度加倍或更多。“

但是它增加了更多的工艺步骤和成本。 “只有在使用标准晶圆厂技术无法满足覆盖预算的情况下,这些解决方案才是必需的,而且在复杂性、成本和设计方面的权衡具有较强的成本敏感性,”Wise说。 “在产品中采用需要权衡,用于自对准的多色SAxP以牺牲工艺复杂性/成本和设计灵活性为代价提高了叠加效果。 然而,设计仍然是个挑战。 在这一点上,业界专注于使用其他不需要这些权衡的技术改进产品覆盖。“

总而言之,具有多色技术的SADP / SAQP不是唯一的选择,但它们确实给客户提供了更多选择。

触点和过孔

领先的芯片由三部分组成 - 晶体管、触点和互连。晶体管由源极,栅极和漏极组成。

位于晶体管顶部的互连由微小的铜布线组成,这些布线将电信号从一个晶体管传输到另一个晶体管。 通常情况下,芯片可能具有10到15个级别的铜互连,这些互连使用过孔连接。

晶体管连接和互连通过一个微小的触点实现,触点是具有小间隙的3D结构,其缝隙里充满了钨。

图6:各个节点处的互连、触点和晶体管。来源:应用材料。

直到最近,芯片制造商在触点和过孔方面几乎没有问题。 以触点为例。 在大多数芯片中,一个栅极位于两个触点之间。 在90nm处,从一个触点到另一个接触点的长度约为200nm。 但是到了22nm时,器件的尺寸缩小到了触点很小的地方。

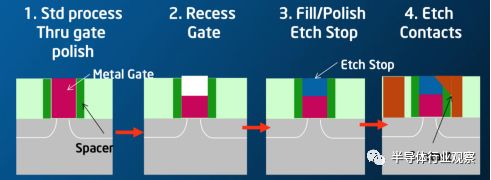

为了解决这个问题,芯片制造商转向自对准的连接方案。 例如,在22nm处,英特尔将触点放置在栅极旁边。 使用自对准方案,金属栅极凹陷。根据英特尔的说法,氮化硅蚀刻停止层被放置在金属的顶部,触点用钨填充。

图7:22nm自对准接触。 来源:英特尔

实际上,自对准接触使芯片制造商能够在设备上填充更多结构,这一举措提高了总体面积缩放比例。

在10nm时代,英特尔又向前迈进了一步。 它将触点放置在有源栅(COAG)上。 采用不同的自对准工艺,英特尔使用碳化硅材料作为蚀刻停止层。 另外,钴取代了钨,以降低线路电阻。

还有其他一些例子,例如完全对齐。 多年来,该行业已经使用damascene般的流程进行接触和过孔。 在接触和过孔中,使用193nm浸入式和多图案技术,可以在表面上形成孔洞,用蚀刻机钻一个小孔,然后,排好洞并填充不同的材料。

在先进的节点上,芯片制造商面临几项挑战,首先,这些结构与多重模式(如EPE)具有相同的挑战;每个节点上的触点和过孔变得越来越小,越来越难以制作。

因此,为了图案化接触孔和通孔,芯片制造商希望从193nm光刻切换到7nm / 5nm的EUV。 结构的其他部分也需要更复杂的制造技术。应用材料公司蚀刻和图案化战略副总裁Uday Mitra说:”在过去的美好时代,EPE的利润率很高,现在它不再只是简单的缩放。实际上是把触点放在栅极上,这就像3D缩放。“

COAG和完全自对准过孔是晶体管内部复杂的类3D模块。 许多类似3D的结构更多地依赖于沉积、蚀刻和新材料。 Gartner半导体和电子产品研究总监Gaurav Gupta说:“基本上,光刻一直是缩放的主要驱动因素,但对于3D设备,当你试图缩放时,它不仅仅是光刻,蚀刻和沉积变得更加重要。“

为了实现这样的结构,供应商开发了一系列工具、材料和流程。 “采用自对准方案的一种方法是使用多种材料,选择性蚀刻,选择性去除和CMP,”Applied的Mitra说。 “你要尽可能使用标准材料。”

还有利用多色材料的自对准技术。“整个世界正在朝这个方向发展,不只是光刻或EUV。有或没有EUV,都需要自我对准的方案。 你需要材料使能的图案化处理,”他说。

例如,应用材料公司称之为“材料使能的缩放”。材料使能的缩放并不完全是一个新技术市场,它基本上是当前自对准技术的演变。 “你仍然必须使用自对准结构,需要不同材料的组合,处理步骤的顺序可能会有所不同。 这是一个由材料解决的图案化问题,而不是经典的光刻收缩或覆盖,“他说。

下一步怎么走?

还有更多方案。 应用材料和其他公司正在研究一种称为选择性沉积的技术,使用原子层沉积工具,选择性沉积是一个在确切位置沉积材料和膜的过程。

选择性沉积仍处于研发阶段。 随着时间的推移,这些技术有望促进各种新设备发展。 Gartner公司的Gupta表示:“对于材料驱动的缩放,新材料将用于制造Ge / III-V,纳米线、石墨烯、VFET和TFET。

锗(Ge)和III-V材料是下一代晶体管的目标材料。 纳米线、垂直FET(VFET)和隧道FET(TFET)是下一代晶体管类型。

显然,自对准方案将支持新器件,并为IC缩放提供急需的推动力。 如果没有这些创新,摩尔定律可能很难演进。

-

芯片

+关注

关注

453文章

50297浏览量

421277 -

摩尔定律

+关注

关注

4文章

630浏览量

78910 -

晶体管

+关注

关注

77文章

9615浏览量

137717

发布评论请先 登录

相关推荐

高性能连接器的选择与应用

恒讯科技分析:海外抖音专用服务器的选择标准以及价格影响因素

关于Patterning的选择和性能分析以及应用

关于Patterning的选择和性能分析以及应用

评论