三星宣布全新的 10nm LPP 工艺已经投产了,而 LPP 工艺相比骁龙835使用的 LPE 工艺,性能提升了10%,功耗下降了15%。但作为一个辣鸡小编,其实我是看不太懂的,都是10nm制程,怎么还能提升性能呢?这些 LPP、LPE 都是指的什么,还有之前看到的 FinFET 这些词又都指的什么?相信和小编有同样疑问的读者不在少数,索性今天我们就来刨根问底一番,看看现在火热的半导体究竟有哪些秘密。

制程的秘密:多少nm很重要吗?

摩尔定律大家肯定都知道:每过18个月,单位面积上的晶体管数量增加一倍嘛!然而多年来半导体制程从65nm到32nm,再到28nm,还有近两年的14nm、16nm和10nm,感觉也没什么规律啊!这里我们就需要认识一下尺寸的计算方式,以及“半代升级”和“整代升级”的概念了。

首先,单位面积内晶体管数量翻倍并不意味着制程就要缩小一半,缩小一半的话单位面积晶体管数量不就翻4倍吗?所以如果要保证两倍的成长,那么整代升级应该乘以0.7。所以从14nm 到10nm,以及后面从10nm 到7nm,都是遵循了摩尔定律的整代升级。

但是在几年以前,我们却经历过一段“半代升级”的风潮,打破了0.7的规律。在 40nm 前后几年,正好是存储器需求飞速发展的时间段,考虑到0.9倍的制程升级就能将闪存容量提升1.24倍,且0.9倍的升级技术简单,半年就能完成,所以不少代工厂开始“半代升级”制程来帮助 NAND 闪存厂商抢占市场。

正常来说制程升级应该是45nm—32nm—22nm—14nm—10nm,也就是经典的Tick Tock。但是台积电当年在 45nm 之后却推出40nm,这也迫使英特尔和三星等厂商打破了规律,在2010年前后启用了 NAND 专属的 35nm 制程(有趣的是华为海思四核也用了35nm 制程)。而鸡贼的台积电后来又跳到 28nm,抢占制程高地,这显然让英特尔和三星很不开心,所以后期三星和英特尔都回到了正常的升级策略,并且从那以后,英特尔就一直对半代升级嗤之以鼻(恼羞成怒)。

而台积电在坚持了 20nm 和 16nm 两代之后,也主动回到了 10nm 的正轨。原因非常简单,因为 NAND 颗粒并不是制程越小性能越好,20nm 之后就会发生严重的电子干扰,所以在 20nm 制程后,各大厂商都转向了3D NAND 技术(如果大家对闪存有兴趣我们今后也可以科普),再往后大家也不在 NAND 的制程上较劲了。

工艺的秘密:这些字母其实很好懂

至于后缀的那些英文其实也不难理解,比如 FinFET 工艺(注意哦,多少纳米叫制程,而后缀指的是工艺),这一工艺最早由英特尔在22nm 制程时提出,而现在英特尔、台积电和三星都用的FinFET 。

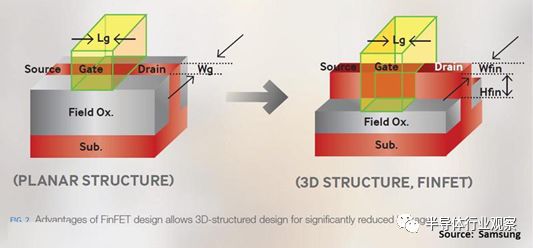

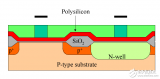

因为制程中 22nm 是指每个晶体管中两个栅极之间的距离,所以 22nm 并不是指晶体管尺寸,一般一个 22nm 制程的晶体管尺寸高达 90nm ,而栅极间距越小电子流动的时间就越短,所以性能就提升了。但是随着栅极距离越来越小,绝缘效果就会下降导致漏电,所以每经过几代制程升级,就需要有一次工艺升级来解决这个问题。FinFET 之前已经有过High-K、HKMG 等工艺了,而 FinFET 之后,我们还会见证 FD-SOI 、GAA的竞争。

至于 FinFET 的原理,它的全称是“鳍式场效晶体管”,简单说来就是讲栅极之间的绝缘层加高,来增强绝缘效果减少漏电现象,是不是觉得挺傻瓜的?但往往是看起来很简单的想法,实现起来却无比困难。

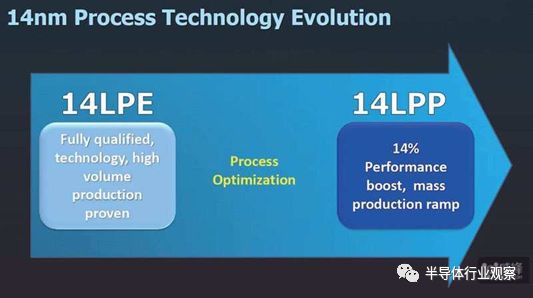

说完了 FinFET,我们还有最后一个后缀,就是昨天报道中的 LPP、LPE 了,其实这些指的都是同一代工艺中的不同种类,比如 LPE(Low Power Early) 指早期低功耗工艺,而 LPP(Low Power Plus)指成熟的低功耗工艺,而适用于移动设备的 LP 系列其实还包含 LPC、LPU 。而且这些后缀并不是10nm 专属,三星 FinFET 工艺都是这样的命名方式,比如14nm FinFET 中,骁龙820是 LPP,而骁龙821则是 LPU。

并且除了 LP 系列之外,当然还有主打高性能的 HP(High Performance)系列, 这其中又分为很多种,这里就不展开讲了。但是这也只是三星芯片的划分方法,像台积电虽然也是 FinFET 工艺,但是却分为了FinFET Plus、FinFET Compact 等几种。

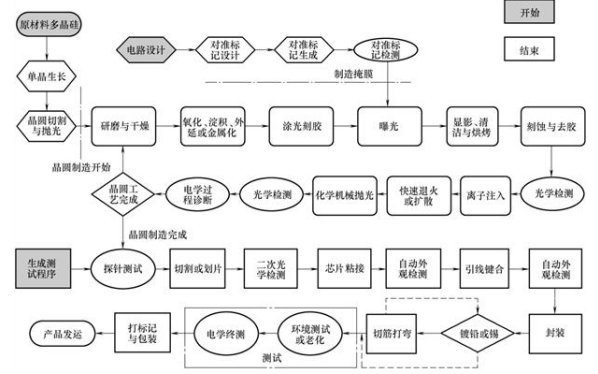

生产的秘密:光刻机被卡脖子啦!

说完了技术,我们最后不如落到生产上聊一聊?毕竟随着工艺的提升,对于生产设备的要求也越来越高了,过去各家在蚀刻晶圆的过程中用的都是深紫外光微影系统,简称 DUV,而随着制程超过10nm,现在 DUV 已经满足不了精度要求,这时极紫外光微影系统(EUV)就上线了。

说到 EUV 是不是觉得很眼熟?没错,不久前三星刚刚以1.5亿欧元每台的价格从 ASML 订购了10台 EUV ,然而 ASML 这么久也一共才生产了23台,很显然,三星是想在 8nm/7nm 时代抢占先机。这已经不是他们第一次这么做了,当初在 OLED 的发展初期,他们就买走了市面上仅有7台蒸镀机中的5台(蒸镀是OLED 生产中的重要步骤),借此延缓了 LG 和京东方的 OLED 生产计划。

-

半导体

+关注

关注

334文章

27380浏览量

218944 -

晶体管

+关注

关注

77文章

9694浏览量

138229 -

光刻机

+关注

关注

31文章

1150浏览量

47414

发布评论请先 登录

相关推荐

半导体制程简介

半导体制程

半导体制造企业未来分析

半导体制造的难点汇总

半导体制造车间的环境与生产要求以及设施规划

半导体工艺几种工艺制程介绍

从7nm到5nm,半导体制程 精选资料分享

先进半导体的工艺会给芯片成本带来多少变化?

半导体制造工艺教程的详细资料免费下载

关于半导体制程/工艺/生产的性能分析和介绍

关于半导体制程/工艺/生产的性能分析和介绍

![[<b class='flag-5'>半导体</b>前端<b class='flag-5'>工艺</b>:第二篇] <b class='flag-5'>半导体制程</b><b class='flag-5'>工艺</b>概览与氧化](https://file1.elecfans.com/web2/M00/B1/D7/wKgZomVdeemAEcbqAAInhahz1Ko856.png)

评论