技术应用虽然已经开始,但哪一种技术路径最好、谁家的最好仍不得而知。

经过多年研发,几家晶圆厂设备供应商终于在去年推出了基于原子层刻蚀(ALE)的下一代蚀刻系统。

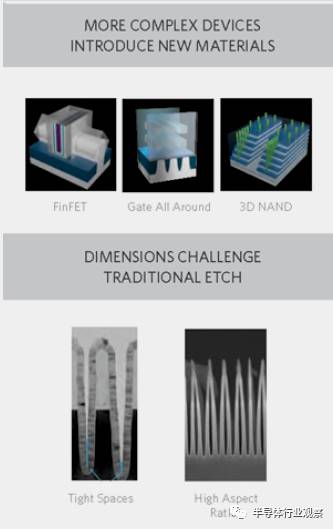

ALE虽指向16 / 14nm的技术方向,但其必将在10 / 7nm甚至更远的技术领域内发挥重要作用。业界也正致力于开发应用于先进逻辑处理器和存储器生产制造的新一代ALE技术。

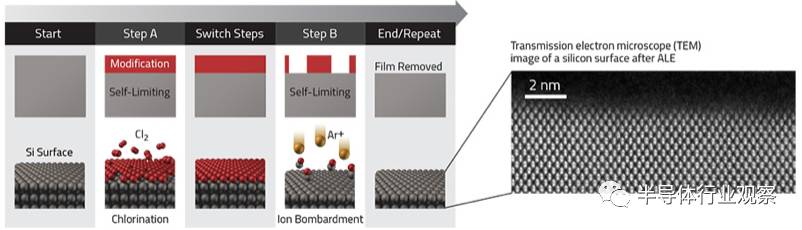

传统蚀刻设备连续的无选择的蚀刻晶圆,该系统在芯片制造商中已应用多年。新一代蚀刻技术ALE有选择地去除原子尺度上的目标材料,而不会损坏结构的其他部分,可以蚀刻出具有10Å~15Å 或5个原子宽度间隙的沟槽。 (1Å=0.1nm)

现在业界正开发的几种类型的ALE,正变得让人困惑。基本而言,业界目前有以下方向发展:

1、ALE设备供应商正在推出的蚀刻系统仍是基于各向异性等离子体蚀刻技术的ALE。

2、该行业现在专注于高温ALE的开发,这种ALE可以各向同性或单向的蚀刻。一些其他厂商也正使用一些不同的ALE方法进行各向同性蚀刻。

3、一些正在开发混合高温等离子体ALE。

4、最终目标是开发出有选择性的ALE,可以有选择性地去除表面上的单一类型材料或原子。

总而言之,等离子体ALE正协助各种芯片制造商实现更先进的生产制造。投资银行Morningstar分析师Abhinav Davuluri表示:“目前,ALE仍处于早期阶段。 我们优先考虑在逻辑芯片领域和专业的代工厂里首先应用,当它逐渐发挥作用的时候,DRAM的性能就会一点点提升。”

ALE无法取代很多传统蚀刻步骤,因为它在产能方面相对而言算是慢的。不过,传统蚀刻无法完成的工作领域,ALE正获得应用。应用材料公司蚀刻和掩膜策略方面的副总裁Uday Mitra说:“业界正在更多的向ALE过渡。随着3D技术的发展,传统蚀刻技术的限制越来越多。随着更先进工艺节点的进入,我们将看到ALE更快的增长。”

Applied Materials, Hitachi High-Technologies, Lam Research , TEL是市场上ALE设备的主要供应商。如今,ALE只占整个蚀刻设备市场的一小部分。研究机构Gartner的数据显示,全球干法蚀刻市场规模2017年将达到96亿美元,高于2016年的72亿美元。

ALE到底是什么?

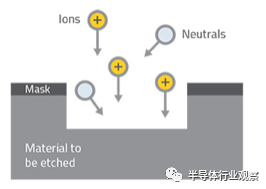

蚀刻,从晶圆上去除材料以形成图形特征的工艺步骤,分为湿法和干法两大类。湿法蚀刻使用液体化学物质去除材料。干法蚀刻通过等离子体轰击晶圆面上的物质来去除材料,市场占比更大。

数十年来,芯片制造商在工厂中使用了被称为反应离子刻蚀(RIE)的干法刻蚀技术。RIE中提到的等离子体(plasma)是由部分电子被剥夺后的原子及原子团被电离后产生的正负离子组成的离子化气体状物质,尺度大于德拜长度的宏观电中性电离气体,其运动主要受电磁力支配,并表现出显著的集体行为。它广泛存在于宇宙中,常被视为是除去固、液、气外,物质存在的第四态。等离子体是一种很好的导电体,利用经过巧妙设计的磁场可以捕捉、移动和加速等离子体。当被加热到足够高的温度或其他原因,外层电子摆脱原子核的束缚成为自由电子,就像下课后的学生跑到操场上随意玩耍一样。电子离开原子核,这个过程就叫做“电离”。这时,物质就变成了由带正电的原子核和带负电的电子组成的、一团均匀的“浆糊”,因此人们戏称它为离子浆,这些离子浆中正负电荷总量相等,因此它是近似电中性的,所以就叫等离子体。

图1:传统等离子刻蚀工艺 来源:Lam Research

RIE设备虽快速可靠,但挑战仍存。首先,芯片制造商必须处理那些很小甚至没有空间的微小功能。如据Lam所说,一个晶体管栅极结构可能是10nm宽,制造中只允许在1nm范围内变化。

然后,传统蚀刻设备中电极在高温高压下激发等离子体轰击晶片,这对于微小的结构制造很有效,但也有可能会损坏结构。因此,不论是对于这种结构还是其他某种结构,需要有选择性地去除目标材料而不损坏其他部分。

那这就是ALE应用的场景。应用材料的Mitra认为:“ALE有两个基本条件:一是它以自我限制的方式去除单个原子层;二是它不会触及和破坏底层和周围的材料。”

自20世纪80年代以来,ALE的研发一度停滞过几年。它是一个一直在寻找适合应用场景的技术。但在过去的一两年里,ALE市场开始升温。 Applied,Lam,TEL等设备制造商在市场上推出了第一批基于ALE的蚀刻系统。

最后,芯片制造商发现了未来生产对ALE的需求。 Lam Research高级副总裁兼技术研究员David Hemker在最近的一次活动中表示:“ALE是使某些集成工艺步骤能够在7nm和5nm进行蚀刻的唯一方式,而且我们看到ALE将会越来越多地被应用。”

ALE正在应用于一些特定的领域。TEL公司技术开发和工艺工程高级总监Peter Biolsi说:“目前ALE在两个主要领域得到应用,一是那些间距或者空间商非常紧密的可能发生孔洞“堵塞”的蚀刻,二是具有超高选择性和均匀性应用。”

在技术方面,ALE与原子层沉积(ALD)也有关系。ALD的原理是反应物先被泵入腔室铺满表面,然后清除化学物质并重复该过程,从而一次形成单原子层的单层材料。

ALD是一个缓慢的过程,但是技术应用几年前就已经开始。如今,ALD应用于逻辑芯片制造中高K值金属栅极的堆栈、DRAM中的电容成型及多重掩膜化。

相比之下,ALE与ALD相反。 ALE以一种自我限制且有序的方式在原子尺度逐层去除材料。

ALE可以匹配不同的应用场景,可以是在现有蚀刻设备配备具有针对性的ALE腔室也可以是专用ALE系统。

但不管如何匹配,ALE过程都涉及到复杂的物理化学反应。在Lam提供的事例中,ALE腔内注入氯气,氯分子被吸收到表面形成氯化层,从腔室中除去未反应的氯气,然后注入氩离子轰击晶圆,除去薄氯化层不需要的部分。

图2:ALE工艺循环 来源:Lam Research

还有其他通过大量材料组合来实现ALE的方法。那么最好的是什么呢?

TEL的Biolsi说:“我们觉得没有最好的办法,我们需要具备使用所有方法的能力,以最好地适应所要蚀刻的材料和应用场景。”

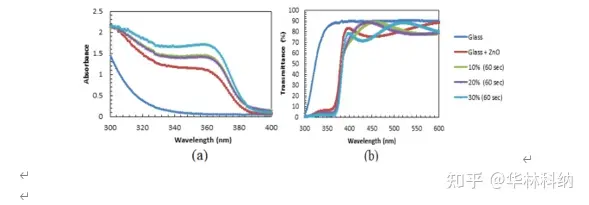

尽管可能有多种分类方法,但根据科罗拉多大学化学与生物化学系教授Steven George的说法,ALE可分为两大——等离子体ALE和高温ALE。当然也有试图结合两种技术的高温等离子体ALE技术。

等离子ALE和高温ALE适用于不同类型的蚀刻,尽管在某些相同的过程中它们是一起使用的 。George说:“ALE方面,等离子体ALE使用高能离子或中性物质从表面上剔除物质的方法来进行蚀刻;而高温ALE应用于特定的高温气相反应。”

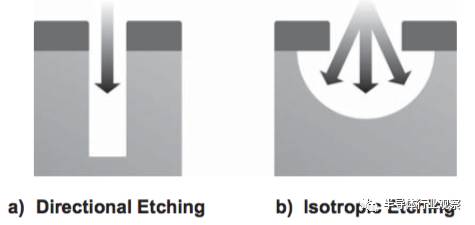

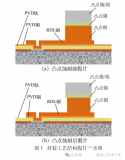

长时间以来,等离子体ALE一直在生产中应用。通常是等离子体ALE进行各向异性或定向蚀刻,相反的,高温ALE执行各向同性或单向蚀刻。

“等离子ALE是定向的。例如,如果您需要钻一个孔,则需要等离子体来完成该操作。等离子体ALE或等离子体处理一般可以做到的事情,你无法用高温ALE的方式来完成。”George说。

等离子体ALE具有有限的各向同性能力。他解释说:“被加速的等离子体是有方向性的,而且等离子体也可以产生其他诸如自由基一类的物质。这些自由基也来自等离子体源,它们的运动有一定范围,不会四处游走。”

相反,高温ALE针对更具挑战的各向同性蚀刻。高温只是一种各向同性蚀刻方法,但并不唯一。有些厂家正在使用更加激进的方法。

图3:定向蚀刻(a)垂直方向的蚀刻速率远大于横向的蚀刻速率,以及各向同性蚀刻(b),其在所有方向上以相同的速率蚀刻材料。来源:Lam Research。

对于各向同性蚀刻,ALE设备会发出可以在任何地方传播的气体分子。所以蚀刻发生在气体分子存在的任何地方。 George说“这些气体分子对于原有体系来说是活跃的新物质,就像新闯入一个街区的小孩,吸引着所有人的注意,这就让高温ALE具备一些等离子体ALE所不具备的潜在能力。高温ALE的互补性使它可以让你决定如何蚀刻而不需要特定材料。这是一个大问题。”

高温ALE不会取代等离子体ALE,反之亦然。芯片制造商可以使用两者来完成不同的任务。

同时,一些研究机构正在开发高温等离子体ALE技术。“这样就可以获得一些高温ALE的优点和等离子体方向性上的优势。” George说。

混合技术仍然在研发当中。等离子ALE已经应用与生产中,但高温ALE仍处于早期阶段,必须在更广泛的材料上进行实验。

然后,不管用何方法,对于ALE的各向异性和各向同性蚀刻都有一些挑战。据埃因霍温科技大学(EIT)应用物理系教授Erwin Kessels介绍,对于各向异性的ALE,挑战在于维持自我限制机制,这要求精确控制离子能量和工艺条件。

各向同性的ALE更具挑战性。Kessels说:“我一直在说每个人都想要各向同性,但是还没有人知道如何去做。开发各向同性的ALE工艺是一个挑战。”

通常,高温ALE利用气相反应来实现各向同性的蚀刻。其他人正在使用不同的方法获得相同的结果。

例如,利用其专用的ALE设备,应用材料公司使用它所认为的先进工艺(radical-based)来进行各向同性蚀刻,通过两个步骤实现,首先进行表面特殊化处理,然后基于自由基的蚀刻方法去除目标材料。

Applied的Mitra说:“我们不需要继续加热,因为(radical-based)工艺温度更高,这种方法选择性非常高。它可以蚀刻一种材料而不接触另一个表面。”

EIT的Kessels在解释这个特定的过程时说:“这就是我们所说的各向同性蚀刻过程,它是由自由基驱动的。所以,你可以用它做各向同性的蚀刻工艺。根据晶圆上的材料组合,您可以以极佳的选择性做到这一点。”

总之,ALE实现了广泛的应用。以下是各向异性和各向同性的一些对比:

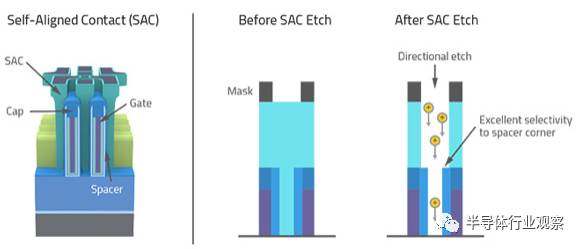

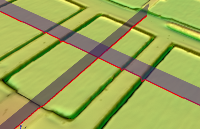

1、晶体管结构:目前,ALE正在生产中用于创建自我匹配的连接 (见下面图3)

2、极紫外光刻:ALE将被用作平滑技术来解决由EUV掩膜版引起的线边缘粗糙度问题,ALE也是针对类似应用而设计的。

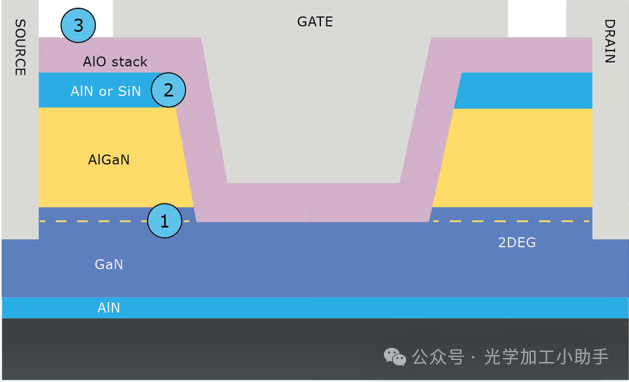

3、全栅极FET:全栅极(GAA)是一种finFET,其侧面上具有栅极缠绕的,未来可能出现在5nm工艺中。

图4:自对准接触的ALE工艺。来源:Lam Research

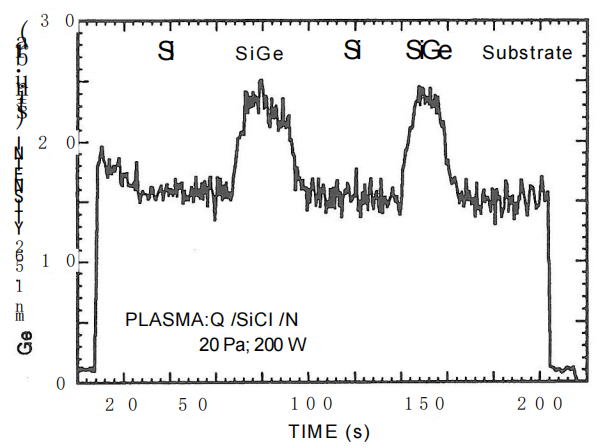

GAA流程的第一步是制作由硅锗(SiGe)和硅(Si)交替层组成的超晶格结构。在工艺过程中,硅锗层必须被去除而不接触硅层。对于这个工艺流程,ALE是唯一的方法。

图5:使用ALE的原因。资料来源:应用材料

ALE的下一步是什么?

综上,ALE正在生产中应用。但是它未来仍会在业界取得什么重大的进展?

现在得出讨论还为时过早。ALE仍处于起步阶段,逻辑芯片厂和代工厂是16nm / 14nm/ 10nm的首批采用者。晨星公司的Davuluri说:“10nm工艺下,ALE主要用于形成接触。未来最有可能的情况,是当我们转向7nm,5nm和3nm工艺时,它将主要应用于晶体管成型。”

但是和以前一样,ALE也有一些挑战 - 成本和产能。他说:“与ALE提高的精确性和准确性相伴,成本也是极高的,工艺流程中的工艺时间和步骤周期,都比一些更传统的蚀刻方法要大得多。

这将限制英特尔,台积电和三星采用ALE。他说:“除了绝对必要的地方之外,他们会试图限制使用AIE。那是一些需要绝对完美的蚀刻的地方。”

还有其他因素。例如,据报道英特尔在10纳米的某些步骤使用ALE。最初英特尔的10nm工艺本来应该在今年年底量产。他说:“取代年底量产计划的,是2018年全面实施。”

考虑到这些问题,ALE市场的总体规模是一个动态的目标。根据晨星公司的数据,目前ALE的业务介于5000万美元到1亿美元之间。他说:“这是一个相当乐观的估计,到2020财年,包括ALE在内的选择性蚀刻将具有4.5亿美元的市场。”

实际上,应用材料公司销售两套ALE系统。第一个设备(Sym3)是一个通用的蚀刻系统。它可以匹配各向异性蚀刻的等离子体ALE,例如自对准接触和基底间隔物成型。

应用材料的Mitra说:“你可以在现有的反应腔体里做ALE。通过正确的控制做快速切换和脉冲,升级现有的反应腔体。ALE最大的缺点是很慢,关键是如何将反应物快速移出。所以你需要一个电导率非常好的反应腔体。“

第二个设备(Selectra)是专门用于各向同性应用的ALE系统。“在选择性蚀刻领域,我们是唯一有设备能力的公司。”米特拉说。

逻辑芯片是第一个应用,但不是唯一的。 Mitra说:“虽然各向异性现在有更多的应用,但各向同性蚀刻适应新的应用和变化。它使客户能够解决新的问题,特别是当客户正在越来越多的向3D制程进军时。如果你看一下3D NAND结构,就知道为了深入到结构中进行蚀刻,就可能需要横向蚀刻。这是传统的蚀刻系统无法做到的一点。“

然后,在研发方面,应用材料正在为ALE开发下一代电子束等离子设备。电子束在腔室中产生等离子体,得到更低的电势(0.3eV)和离子能量(<2eV)。Mitra说:“这是才真正的原子控制,电子束是用来产生电势很低的离子。”

电子束ALE仍处于寻路阶段。 Mitra说:“你可以用它来做一些奇特的事情。对于接下来的两三个节点,我认为你不需要像电子束源那样的东西。”

所以公司当前的ALE设备可以为未来的两到三个节点做好工作。展望未来,目前设备的目标是提高能力和产能。

与此同时,Lam Research发布了一个具有定向ALE功能的刻蚀系统。现在,Lam正研究在最新的设备型号(Kiyo和Flex)中应用新的定向ALE技术。

Lam公司蚀刻产品副总裁Thorsten Lill表示:“我们看到ALE可以应用的节点数量不断增加,大多数关键的蚀刻需要方向性,因此定向ALE值得被关注。”

像应用材料一样,Lam也看到了对各向同性ALE的需求。 Lill说:“垂直器件集成驱动了对各向同性蚀刻的需求,未来将有必要增加各向同性ALE蚀刻技术”。

同时,TEL销售传统的蚀刻产品以及ALE气体化学蚀刻系统(Certas)。TEL的Biolsi说:“TEL已经采用各向异性和各向同性的ALE方法进行硅的电介质蚀刻和各向异性蚀刻。硅的各向同性ALE仍在改进之中。

晶圆厂设备供应商正在忙于研究不同的ALE方法。该技术正在被用于有针对性的场景,但是随着时间的推移,该技术还将与ALD技术一起应用。

ALE也将在一个名为选择性沉积的新兴领域发挥作用。将新型化学品与ALD相结合,选择性沉积涉及在确切位置沉积材料和薄膜的工艺。

CU的George说:“ALE将与原子层沉积相辅相成,你可以用ALD控制薄膜。然后使用ALE,就能够以相辅相成的方式去除材料。”

选择性ALE是另一项需要关注的技术。当前的ALE技术条件下,设备可以去除目标结构。选择性ALE更进一步,仍然在研发中。George说:“想象一下你有一个基板或设备,表面上有许多不同的材料。 当你想蚀刻所有的氧化铪或者蚀刻所有的硅。为了做到这一点,控制将是非常重要的。”

芯片制造商仍在探索ALE的所有可能性。这项技术还处于起步阶段,目前正在整合中。 EIT公司的Kessels说:“蚀刻,表面处理或者沉积技术的组合将会诞生许多混合工艺,我们正站在原子尺度制造工艺的开端。”

-

芯片

+关注

关注

455文章

50714浏览量

423139 -

等离子体

+关注

关注

0文章

122浏览量

14223 -

PCB设计

+关注

关注

394文章

4683浏览量

85546 -

原子

+关注

关注

0文章

87浏览量

20292 -

可制造性设计

+关注

关注

10文章

2065浏览量

15532 -

华秋DFM

+关注

关注

20文章

3494浏览量

4457

发布评论请先 登录

相关推荐

原子结构模型及特点 原子的组成及结构解析

AUTOSAR通信组件介绍 AUTOSAR通信层功能分析

湿法蚀刻的发展

玻璃基电路板的蚀刻和侧蚀技术

基于光谱共焦技术的PCB蚀刻检测

中微推出自研的12英寸原子层金属钨沉积设备Preforma Uniflex AW

江苏鲁汶仪器股份有限公司揭示原子层刻蚀新方法

影响pcb蚀刻性能的五大因素有哪些?

蚀刻机远程监控与智能运维物联网解决方案

半导体资料丨氧化锌、晶体硅/钙钛矿、表面化学蚀刻的 MOCVD GaN

Si/SiGe多层堆叠的干法蚀刻

关于原子层蚀刻的分析和介绍

关于原子层蚀刻的分析和介绍

评论