几大晶圆厂的Roadmap我们可以看到,TSMC、三星和格芯可能回来明年上马7nm产线。届时新工艺将会为下一代产品提供更多高性能的芯片。从现在的格局看,Intel也许有稍微落后,但可以肯定的是他们一定会持续投入到这个节点。为了应对日益增加的开发和制造成本,三星、台积电和Intel都探索将芯片集成度提得更高的可能。他们也还在加大研发,希望在7nm之后的下一代工艺领先于其他竞争对手。

7nm还没到来,

围绕4nm的竞争已经开始打响!

7nm工艺的领先者台积电计划在2019年试产5nm,也就是说在2020之前,我们并不会看到商用的4nm芯片。落后于台积电的格芯在7nm上的投入也有一段时间,按照他们的说法,这个工艺将会持续一段时间,也就是说到2021年,我们应该都看不到他们的5nn工艺细节。和前面两家相比,三星的策略似乎显得有点激进。

得益于在EUV方面的提前投入,并率先将新一代光刻机引入到7nm节点。这个领先于所有对手的决定,让他们可以在公司布局上走得更前。

在今年的ARM技术大会上,三星电子一再强调他们在7nm的野心,并大谈特谈他们在2018的计划。按照他们的说法,他们将会迅速推进6nm、5nm工艺的发展,并最早在2020年带来4nm。这个领先于所有竞争对手的规划,会给台积电带来压力吗?

率先布局EUV,

三星的优势

虽然三星并不是EUV光刻机的制造商,三星甚至不是ASML的股东,但公开的信息显示,三星似乎已经在EUV光刻机的采购和产线布置上全面领先所有竞争对手。昨天新闻甚至说到三星为其DRAM芯片采购了四台EUV光刻机,提早布局的EUV将会是三星的一大武器。

随着摩尔定律的演进,传统193nm光刻机并不能满足缩小晶体管的需求,而EUV则被看做是未来先进工艺发展的重要技术之一。面向尺寸更小、生产速度更高、成本更低等要求的新一代晶体管,只有波长更短的EUV光刻才能达到这样的要求。

从表面上看,引入EUV工艺可以大幅提升性能,缩减曝光步骤、光罩数量等制造过程,节省时间和成本。不过显然引入EUV技术并不容易,其需要投入大量资金购买昂贵的EUV设备,同时需要进行大量的工艺验证以确保在生产过程中获得较佳的良率,才能以经济的成本适用于生产晶元。三星恰恰拥有这个优势。

由于他们拥有多个产业,可以为它的先进半导体制造工艺提供资金支持,而它多年来也愿意为此付出巨额的资金;三星也是全球最大的存储晶元生产企业, 可以通过在存储晶元上锤炼先进工艺。三星在2015 年7 月即携IBM,利用EUV 打造7 纳米芯片原型,在过去这三年其就采用EUV技术处理了20万片晶圆生产SRAM。在256MB的SRAM上,三星甚至实现了80%的良品率,这是三星在未来竞争中的基础优势。

在今年十月,韩媒BusinessKorea透露,业界消息显示,三星正向荷兰业者ASML洽谈,打算购买10台EUV设备。EUV极为昂贵,一台要价2,000亿韩圆(约1.8亿美元)。报道进一步指出,ASML是全球唯一的EUV生产商,今年只制造12台,要是其中10台都被三星订走,其他业者买不到设备,那么三星的地位就更稳了。

在之前,我们也做过很多关于EUV的报道。也说到三星将于TSMC和格芯布局EUV。根据之前的报道,三星将会在7nm工艺上引入EUV,但TSMC和格芯在第一代7nm上将会继续采用浸没式光刻的做法,到第二代才引入。这就使得三星在EUV的量产经验上领先于竞争对手。帮助他们在后面的工艺发展上,走在竞争对手前面。

5nm和4nm之后,硅晶圆制造商不但在推进EUV技术,他们还在探索FinFET之后的新设计,满足更小设计的要求。

FinFET之后的探索,

三星技胜一筹

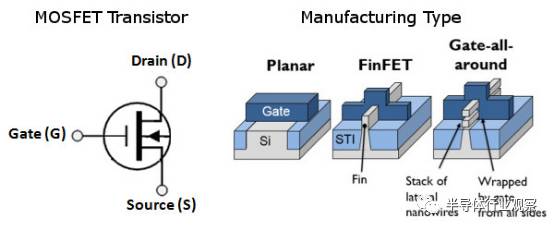

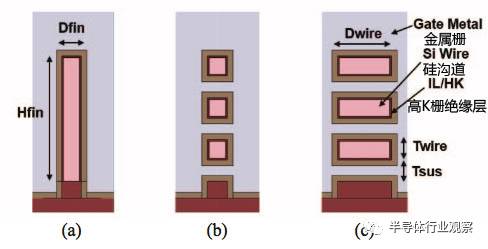

以前的手机处理器使用的MOSFET硅晶体管,后来随着工艺研究,漏电电流逐渐增加,于是业界都走向了FinFET,这也是现在的主流晶体管。现在随着制程的推进,业界正在探索在探索新的可能。三星也很早就分享了他们在这方面的见解。

在年初由SEMI主办的中国国际半导体技术大会上,三星指出,随着7nm的到来,沟道变窄了,那就要求在在设计制备的时候需要从架构、沟道材料和工艺制备上进行创新,而GAA (Gate-all-around)FET、三五族沟道材料和EUV光刻是对应的最好答案。

他们认为在GAA上有两种方案,一种是水平的,它能够打破FinFET的限制。另一种是垂直的,能突破更多的物理限制。

在这里,我们介绍一下GAA 。GAA有时候被称作横向纳米线场效应管。这是一个周边环绕着 gate 的 FinFet 。GAA 晶体管能够提供比 FinFet 更好的静电特性,这个可满足某些栅极宽度的需求。

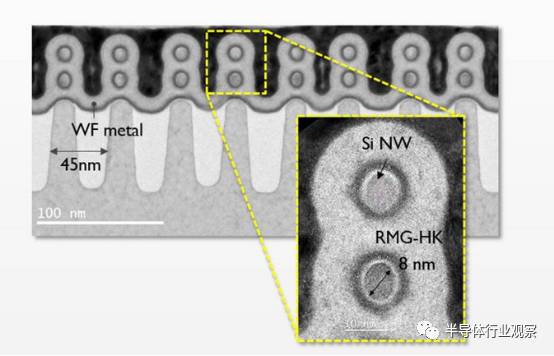

从表面上看, GAA 和栅极夹杂在源极和漏极之间的 MOSFET 很类似。另外, GAA 同样包含了 Finfet ,但和目前 fin 是垂直使用的 Finfet 不同, GAA 的 Finfet 是在旁边。GAA Fet 包含了三个或者更多的纳米线,形成沟道的纳米线悬空且从源极跨到漏极。其尺寸是惊人的。 IMEC 最近介绍的一个 GAA fet 的纳米线只有 8nm 直径。

控制电流流动的 HKMG 架构能够填补源极和漏极之间的差距。但是从 FinFet 向 GAA 的转变并不会有很大的优势,当中你只是获得了对晶体管静电性能控制的提升。GAA 最大的提升在于缩小了栅极宽度。这样你就可以得到一个全环绕和一点的静电性能的控制。当然, gate 的缩小是必不可少的。

在今年早些时候,三星、格罗方德与IBM一起,合伙推出了世界上第一个基于EUV和GAAFET打造的5nm硅芯片。根据三星最新的消息,他们将会在4nm的时候将GAA技术正是引入。那就意味着5nm之后,三星将会用GAAFET取代FinFET。三星方面也表示,到时不排除引入新材料。

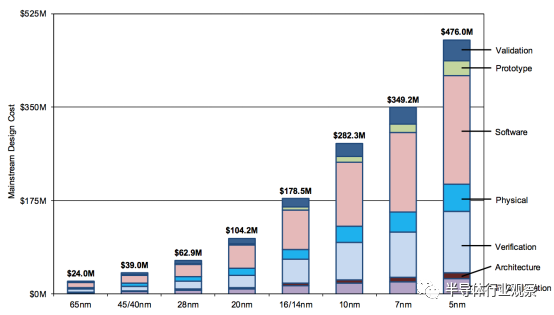

对GAAFET来说,最大的挑战就是其制造会比FinFET困难许多。那么其成本会更加贵。根据IBS的估算,在5nm节点,设计一款主流芯片的成本将高达4.76亿美元水平,而7nm节点的成本仅3.492亿,28nm则是0.629亿。

大战已经开启,

三星胜算几何?

虽然对消费者来说,到2018年甚至2019年,他们都不能从7nm芯片上受益。但是晶圆厂已经在这两项技术上投入了很多。三星也已经开始到处展现他们在上面的成就了。从他们的公开信息我们可以看到,他们似乎对EUV和GAAFET很有信心,凭借这两项技术在4nm上领先于所有竞争对手。从三星在晶圆厂的表现看来,4nm将会是他们超越台积电的一大重要节点。

不过我们应该看到,三星并不是唯一一个在EUV和GAA技术上布局的厂商,其他晶圆厂也在上面的布局应该也很快会面世。虽然目前来看三星表现得很激进,领先也很多。但在晶圆代工领域,预先布局,并不代表你能领先。我们期待看到台积电和格芯的更多进展,才能做出一个更公正的评价。

举个例子,台积电一贯以来在研发先进工艺上出了名保守。在研发16nm工艺的时候它就先在2014年量产了14nm工艺然后再在2015年引入FinFET工艺,而三星则直接在2015年量产14nmFinFET首次取得在先进工艺上对台积电的领先优势。但是在后来的苹果处理器上发生的“芯片门”表示,台积电还是领先于三星。

另外,我们还要看到,客户的支持对于晶圆厂的进展有很大的帮助。目前台积电前三大客户分别是苹果、高通和博通,其次分别是联发科和大陆手机芯片厂海思;从前五大客户组合来看,代表手机芯片是台积电最重要客户群。而这些客户都是走在芯片制造技术的前沿,他们给台积电的加持,是三星所不能企及的。

而在三星方面,虽然一直有高通在加持,但在今年7月有消息传出,高通骁龙845将会转向台积电生产,这对三星来说也许会是一个障碍。

据《路透社》七月报道, 三星执行副总裁暨晶圆代工制造业务部门的负责人 E.S. Jung 表示,三星的晶圆代工业务希望未来 5 年内把市场占有率提升至 25% 的比例。但联想到台积电今年的市占达到了56%,其高额的利润将会成为他们未来技术竞争的最好保证。再加上大摩早前的报告指出,存储产业的超级周期终于终结。这个占三星营收60%的业务的放缓,加上三星本身的“动荡”,会否阻碍三星未来的发展,这又给我们提出了疑问。

-

三星电子

+关注

关注

34文章

15859浏览量

180985 -

台积电

+关注

关注

44文章

5632浏览量

166408 -

晶圆厂

+关注

关注

7文章

620浏览量

37857

发布评论请先 登录

相关推荐

关于三星与台积电在4nm上的竞争分析

关于三星与台积电在4nm上的竞争分析

评论