那天,买了一个肉夹馍吃,吃了肚子疼,上了好几次厕所。回去找老板理论,老板说,昨天我卖出去一百个馍,只有你一个人反应肚子疼,你是想讹我吧!我说我不想诬赖你,千真万确,中午我除了夹馍根本没吃别的东西。老板说,这样吧,我退你钱。我说,不行,你得有所改正,万一以后再发生同样问题怎么办?以后更严重,把小朋友吃坏怎么办?老板说,你看,我的整个工序十几道,供应商也好几个,有可能是面粉的问题,有可能肉,有可能辣椒坏了,也有可能我烤馍没烤熟,我怎么改进呢?而且,唯一一个坏的夹馍,还让你给吃了,我查也没法查啊!我说,你要不改,我以后再也不来你这里吃了!

各位,你们觉得下次我还会去这家店吃肉夹馍么?

好吧,为了给非专业人士讲明白半导体良率这件事儿,处心积虑想出了这么个故事。但道理是相通的,每个晶圆厂(夹馍店)都希望自己的良率(夹馍质量)越高越好,这样大家都愿意来它这里投片(吃夹馍)。而每个IC设计公司都希望自己的产品成本越低越好,而且客户不要退货。

那么今天,我们就把晶圆,当做夹馍,来好好聊聊良率那些事儿。

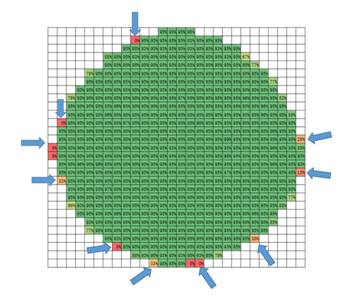

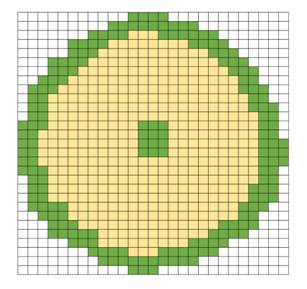

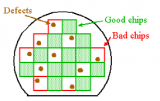

我们知道,每一片晶圆上,都同时制造数量很多的芯片。例如下面这张图,但是,不同的芯片有不同的大小。大的Soc芯片,有可能一片晶圆上只有几百个甚至几十个芯片。而小的芯片,一个晶圆可以有成千上万颗。

我们把每一颗芯片看做一个肉夹馍,那么一片晶圆上这么多“肉夹馍”,有多少质量过关的“肉夹馍”,这个比例就是晶圆测试阶段的良率。就如上面那个例子讲的,老板一天卖出去一百个夹馍,只有一个是坏的。那么良率就是99%。

那么,这个良率和什么有关呢?一般来说,主要和下列因素相关。

1.生产工艺:生产工艺包括生产条件(厂房,设备,材料),工艺水平,工艺经验与管理。

2.产品设计方法:我们这里讲的是可制造性设计问题。

3.测试方法:测试技术与管理。

那么我们详细讲一下:

第一, 生产工艺。

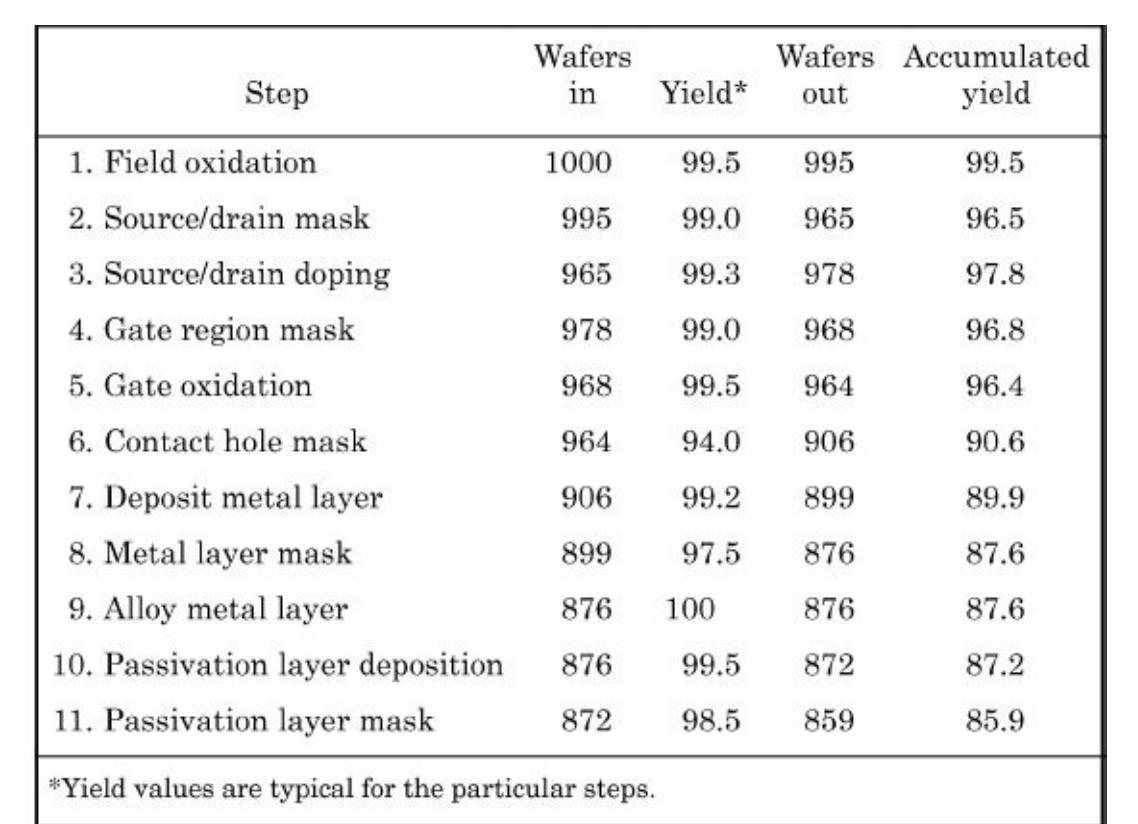

晶圆的生产工艺是非常复杂的,整个流片过程包含光刻、蚀刻、化学气相沉积、物理气相沉积、离子注入以及炉管等几百甚至上千步骤,需要单次或者多次进入不同的机台,这个可比肉夹馍的工艺复杂多了!每个步骤,都有可能导入缺陷。那么问题来了,客户在选择晶圆厂以及工艺的时候,还没有流过片,怎么知道这家晶圆厂好不好,这个工艺稳定不稳定,怎么预估自己的产品的良率和成本呢?

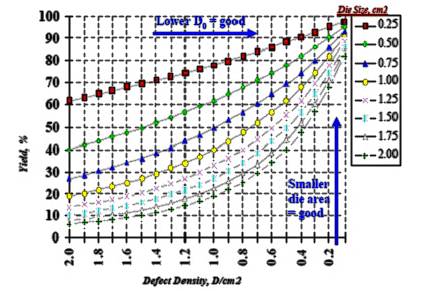

事实上,晶圆厂会给客户提供一个D0值(平均缺陷密度)以用来表征这个工艺的良率水平。根据这个Do值以及特定的计算公式(不同的晶圆厂可能提供不同的计算公式),可以提前预测产品的大概良率。

听上去是不是很神奇?那么这个Do是什么呢?又是怎么预测良率的呢?

其实D0就是表征这个工艺在晶圆单位面积上产生缺陷的概率。D0的推导是十分复杂的。但我们可以把这个概念简单化来理解它是一个什么东西,比如,一个肉夹馍,会夹100个肉丁,而100个肉丁里,会有1个肉丁是变质的。我们把这个缺陷密度看做0.01(1%)。另外一家店,同样100个肉丁里,会有10个是变质的,那么缺陷密度相对就是0.1(10%)。那么哪家的夹馍好呢?当然是0.01 要好于0.1. 一般来说,D0越小,表示这个工艺越成熟,良率越高。

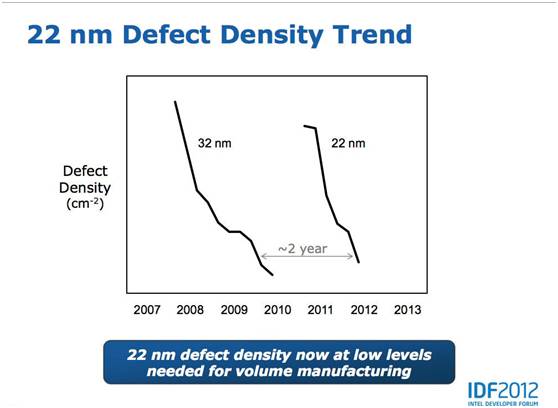

当然,晶圆厂会不断完善和改进工艺,D0一般从刚开始研发到成熟量产的两年过程中会不断降低。下面请看32nm和22nm工艺当初的D0发展趋势。

问题来了,良率只和D0有关吗?

非也非也!我们再回到那个夹馍,100个肉丁里,有一个是坏的。如果我们切100份,坏的肉丁影响了一份,那么良率就是99%。如果我们把馍切1000份呢?那么那个坏的肉丁还是只影响一份,但这时良率就变成99.9%了。我们把每一份想象成一个芯片,那么芯片的面积越大,良率就越低。其实,换句更通俗的话讲,这和战争中胖子比瘦子更容易中弹是一个道理吧。请看下图关于D0、芯片面积和良率的关系:

关于神奇的D0,讲到这里结束了吗?还没有哦,大家要注意,对于芯片里Logic(逻辑)电路和SRAM(静态存储器)电路,D0是不一样的!为什么呢?因为SRAM的密度要比Logic大得多,那么同样是掉一颗缺陷,落在Logic区域的,可能就掉在空地上了,而掉在SRAM区域的,很可能影响电路。所以,晶圆厂针对Logic和SRAM提供不同的D0值,在预测目标良率的时候要根据芯片里面SRAM和Logic的面积比例综合考量哦。

试想,如果天上掉下来一颗石头,哪里伤亡更惨重呢?

二、产品设计方法

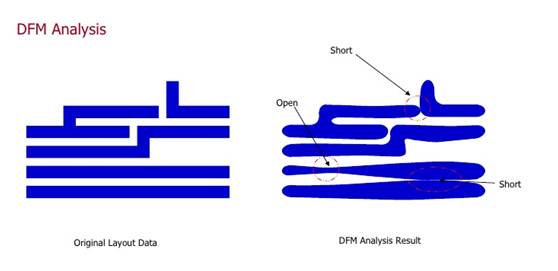

这里讲的设计方法,和良率息息相关的主要是可制造性设计(DFM)和可测试化设计(DFT)。可制造性,顾名思义,就是设计的时候要考虑到制造的因素。同样一个设计,版图不同的画法、元器件摆放方向、位置,都有可能影响到最终的良率。这是当工艺越来越先进,线宽越来越小时所带来的不可逃避的问题。

一般情况下,当工艺进入65nm及以下,晶圆厂就会提供可制造性设计规则供IC设计公司检查。但是一般认为65nm及45nm工艺,可制造性设计规则是供参考的。因为工艺足够成熟,可以不必在设计上花费很大的精力去遵守可制造性设计规则。但是到了28nm及以下,可制造性规则就是必须在设计过程中严格遵守了。

DFT比较复杂,避免把大家讲糊涂,这里就先不详述了。

三、测试方法

首先,需要强调一下,测试方法不会改变芯片本身的质量,不会因为不同的测试方法,将本身一个功能失效的芯片变成好的芯片。但是,经过优化的测试方法,可以在具有高测试覆盖率的前提下,控制成本又能降低在最终客户那里的DPPM(Defective Parts Per Million,表征质量的参数),减少退货率。

晶圆生产出来后,在出晶圆厂之前,要经过一道电性测试,称为晶圆可接受度测试(WAT)。这个测试是测试在切割道(Scribe Line)上的测试键(TestKey)的电性能。测试键通常设计有各种原件,例如不同尺寸的NMOS、PMOS、电阻、电容以及其他工艺相关的特性。这一道可以当做是初选。那些有严重生产问题从而使得测试键的电性能超出规格之外的晶圆会在这一道被筛选出来,报废掉。这一道报废掉的晶圆,因为还没有出货到客户手里,所以是不收取客户钱的,由晶圆厂自己吸收。

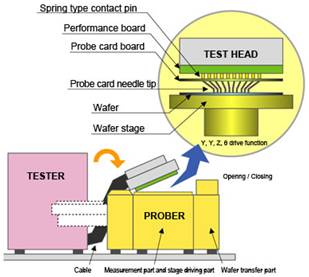

WAT测试结束后,晶圆工艺就算完成。下一步就是来到测试厂这里进行测试。第一道晶圆切割前的测试我们称为CP (Chip Probing), 因为这一道测试是在完整的晶圆上测的,用到的机台,我们称作Prober。每一个产品,都会有针对自己设计的Prober Card, 上面根据芯片的测试焊盘(Pad)的位置装有对应的测试探针及电路与测试台连接。每次测的时候,测试头从上面压下来,探针就会扎到Pad上,然后供电进行测试。

讲到这里,不得不提一下测试的成本问题。通常情况下,我们会发现,一个IC产品,测试的费用占了整体成本的很大一部分。所以,怎样将测试程式优化到简单而高效(达到必要的测试覆盖率),就是IC设计公司的测试工程师的工作了。测试程式越简化,需要的测试时间就短,测试成本就下降。

一般,在CP阶段,为了节约成本,不会测到全部芯片的功能。比如,有一些需要用到昂贵测试机台的模拟功能测试,可能在CP阶段就被省略,放到后面的FT(Final Test)再进行。

除了在测试程式上优化,在测试方法上优化也是大家一致在努力的方向。

一般用到下面几个方法降低CP测试成本:

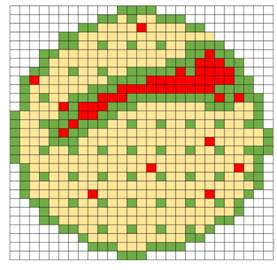

1.在生产一段时间后,对于晶圆边缘的低良率芯片,直接忽略掉,不予采用。

一般,我们拿到了一个产品的一定量的CP测试结果后,可以将结果堆叠。Wafer的周边,一些不完整的芯片或者因为过于靠近边缘均匀性受到影响的低良率芯片,直接在测试程式上删除。

将上图中的不完整芯片和低良率芯片删除,那么每片晶圆可以少测12个芯片,降低了成本的同时,良率和质量和质量也相对提升。

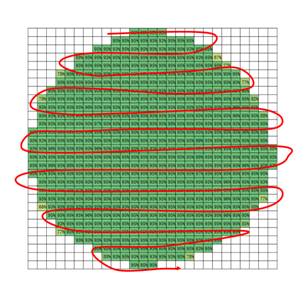

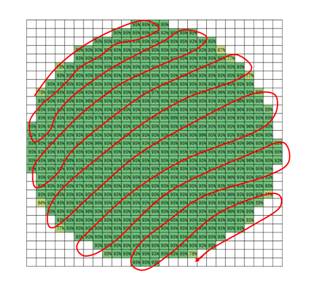

2.那么上面经过优化的测试map还可以优化吗?我们知道,同一个probe card可以同时测几个芯片,怎么排列是个问题。如果同时可以测6颗,那么排列是2x3 还是3x2,或者1x6,都会对扎针次数产生影响;不同的走针方式,也会产生不同的扎针次数。比如有可能下面第二张图就可能比第一张图少几次扎针,这样就会节省测试时间。现在市面上有专业软件可以模拟和优化这些。

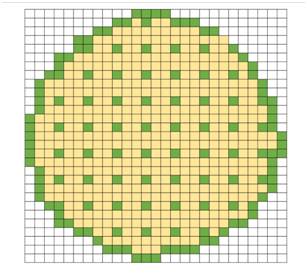

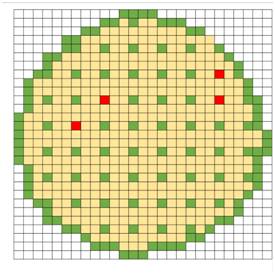

3.抽测:当一片晶圆上有几千颗甚至上万颗芯片,而且良率已经达到一个稳定的高度时,很多公司在CP阶段采用抽测(Sampling Test)的方式以减少测试时间。下面的图中,黄色代表不进行测试的芯片,绿色代表需要测试的芯片。下图是个典型的抽测方式。请注意,一般晶圆边上一圈良率相对较低,在抽测的时候有时会考虑这一圈全测。

还有采取只测良率最低的晶圆外侧及中心的芯片。例如下图:

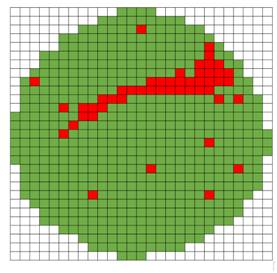

不管怎么变化,目标只有一个,那就是用最少的测试费用,尽可能多地筛选出不合格芯片,那么问题来了,上述抽测是否会错过一些异常低良率的晶圆,造成后面封装及终测的浪费?答案是肯定的。抽测肯定要比全测有更大的风险。以下图为例:假设下图为抽测结果,绿色表示好的芯片,红色代表失效的芯片。看上去只检测出四颗坏的芯片,良率还不错。

但是,如果进行全测,有可能是这样的,不仅遗漏了低良率的芯片,还可能因为这种遗漏造成潜在的可靠性问题:

那么,怎样在抽测的情况下尽量避免上述问题呢?

一些大数据实时监控软件可以在测试的同时监测并控制走针,测试者可以提前设置一个条件,例如,当测到一个点失效以后,测试探针自动围绕这颗失效芯片测试周围一圈的芯片是否是好的芯片。如果周围是好的,那么探针回到下一个抽测点继续抽测。如果周围一圈的芯片里面还有不好的,继续围绕这颗失效的芯片一圈测下去。那么我们会发现,如下图,这一条失效的芯片都被测出来了。基于可靠性的考量,测试者可以决定是否将这种失效芯片周围一圈的好的芯片也报废。

说了这么多,才刚刚结束了CP这第一道芯片测试。CP测试完的芯片,会经过晶背打磨、切割等程序,剔除掉失效芯片,将好的芯片送入到封装制程。

封装过程,芯片经历打线、冲模等高温高压过程,也会有一定的良率损失,但这部分在没有意外发生的情况下是很小并且稳定的,一般考虑的不多。但是近年也有公司在考虑使用大数据的手段,监控封装机台的参数,进行大数据分析,来提高封装良率,在这里不予讨论。

等封装完毕,这颗芯片就有模有样了,就像肉夹馍,饼已烤好,肉已加好,可以出锅!

之后,封装好的芯片进入终测(Final Test)。因为终测是很多IC产品商对自己产品的最后一道测试,这个测试相对会比CP测试要完整,而且终测可以做CP不能做的高速和混合信号(mix-signal)测试。

终测的良率,因为经过了前面的层层筛选,一般是不错的。但是,我们讲到,因为终测包含了比CP更多的项目,也有可能遭遇到低良率问题。一般情况下,终测的低良率,更难找到原因,更复杂。有可能与模拟参数有关,有可能与封装有关,也有可能与ESD失效有关,所以往往要用到各种各样的失效分析方式进行分析。

对于很多公司来说,产品到了终测之后,就可以出货给客户了。但是有一些公司或者一些产品,在终测之后,还会做系统级测试(SLT,System level test, 又叫Bench test)。 SLT是搭建实际系统应用环境来测试。以手机芯片为例,可以搭建open phone模拟客户的样机进行芯片测试甚至可以模拟客户使用中可能遇到的各种问题,例如,手机信号的方向性问题以及电池低温保护问题。这些测试在之前的CP和FT是无法测试到的。

当然,SLT会更耗费时间,所以可以采用定期抽测的方式进行。

好吧,说了这么多,你可能要问了,芯片可以出货了吧?其实还没有讲到质量(QA)管控的问题。 QA是一个大的体系包含各种验证,时间可能会很长。但是QA的目的是保证产品质量和可靠性,而不是良率提升,所以有时候产品部门会觉得QA部门就是来找麻烦、来挑刺的!这个QA部门就像是专门试吃各种夹馍,而且还长期监测个血糖、血压啥的,一有异常就回来找夹馍店老板麻烦!质量认证,先不讲了。留点悬念,回头再请大牛来讲一下哈!

回头一看,居然说了这么多,别把大家说糊涂了!

简单总结一下吧,良率是用来表征肉夹馍的好坏的。生产工艺越完善、设计方法越先进,肉夹馍就越好吃,次品就越少而且吃了越不容易拉肚子。通过优化测试方法来保证检测率并同时降低成本:你是要狼吞虎咽,还是配凉皮、冰峰慢慢享用,这个就看你自己啦!只能说狼吞虎咽对肠胃不好,可是没钱也别太讲究!

-

芯片

+关注

关注

455文章

50851浏览量

423903 -

半导体

+关注

关注

334文章

27390浏览量

219025 -

晶圆

+关注

关注

52文章

4917浏览量

128018

发布评论请先 登录

相关推荐

领泰 / LEADTECK领泰半导体(深圳)有限公司由一级代理提供技术支持

广立微INF-AI助力格科微产品良率提升

半导体工艺之生产力和工艺良率

关于半导体良率的详细介绍和分析

关于半导体良率的详细介绍和分析

评论