USB規範是USB開發者論壇(USB IF)維護的產業標準,規定了許多個人電腦與外接周邊設備間USB連接事項,比如電纜、接頭、連線協定、通訊以及電源。作為目前最新版本的USB規範,USB 3.2將資料傳輸頻寬大幅提升至10Gbps。USB 3.2 Gen2規範大幅提升了資料編碼效率,提供的速率比USB 3.1 Gen1一代提供的速率(5Gbps)快一倍。

USB Type-C(也作USB-C)支援最新的USB 3.2標準。特性完備的USB-C電纜可支援10Gbps的資料輸送量,是USB 3.2 Gen1標準的兩倍。根據DisplayPort 1.4標準,在每路顯示輸出中該電纜支援四通道,每通道資料傳輸率可達8.1Gbps。DisplayPort則是以資料包的形式通過數位介面同時傳輸高解析度音視訊訊號,總頻寬可達32.4Gbps。高速的資料傳輸率和常見的嵌入式時鐘架構的結合,有助於在差分訊號對通道中傳輸海量的資料和影音訊號。

訊號完整性成高速訊號傳輸挑戰

高速訊號在通過電纜或印刷電路板傳輸時,衰減現象很嚴重,甚至會導致訊號畸變。訊號通常透過傳輸線路傳輸,長度為10到12英吋的傳輸線路導致的通道插入損耗達20dB或更高。此外,反射、串擾、雜波訊號和散射都會導致訊號完整性與眼圖區間惡化。訊號傳輸距離增加導致訊號衰減程度加重且訊號品質下降,進而導致資料位元錯誤,無法在遠端或接收端成功復原傳輸的訊號。

為避免或減輕這種現象,須為資料傳輸率為8.1Gbps以上的序列介面設置中繼器,以濾除隨機雜波和系統雜訊,使訊號符合規範要求。中繼器通常部署在通道途中,以補償通道損耗。目前有兩種類型的中繼器:Retimer和Redriver。Retimer可對來自上游通道的訊號進行均衡,使用CDR恢復時鐘訊號,並生成數位應激訊號,傳送至下游通道。Redriver可均衡來自上游通道的訊號並將其傳送至下游通道。它的輸出訊號在輸入訊號的連續驅動下生成。Redriver不包含CDR,也不執行重定時操作。

桌機/筆電USB-C與USB-A介面訊號改善方案

在所有互聯協定中,資料傳輸速率不斷提高,對CPU的性能要求更高,進而提升整個通道的資料傳輸速率。當主流CPU供應商不斷減小其晶片尺寸以降低功耗、維持性價比時,這種情形尤其明顯,最終導致保證訊號符合規範要求的最大傳輸路徑長度不斷縮短。

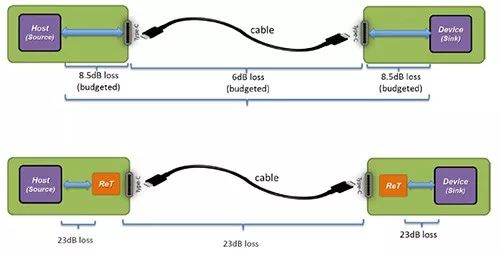

英特爾(Intel)的CNL和CFL平台USB3.1 Gen 2應用設計指南建議OEM廠商在使用USB-C接頭時,使用基於Retimer的主動複用解決方案;在使用USB Type-A接頭時,使用Retimer方案,以保證訊號完整性,獲得更好的JTOL區間。Retimer應用必須符合USB 3.2規範的附錄E,在USB 3.2 Gen2模式下能夠提供23dB的損耗補償。

USB 3.2規範定義了以下兩種類型的Retimer:

·SRIS Retimer

在SSC無關參考時鐘(Separate Reference clock Independent ofSSC, SRIS)Retimer應用中,傳輸時鐘訊號來自本地參考時鐘,與接收端復原的時鐘訊號無關。

·BLR

數據位元Retimer(Bit-Level Retimer, BLR)的應用中,傳輸時鐘訊號來自接收端復原的時鐘訊號(鏈路訓練的某些階段除外)。

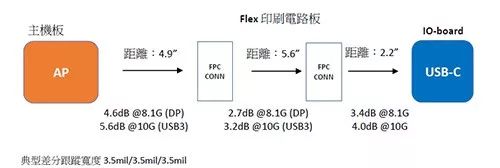

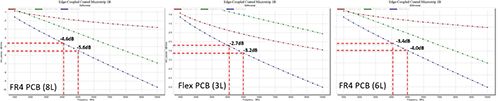

圖1 對桌機/筆電的USB-C插入損耗進行補償設計

圖1與圖2為對桌機/筆電的USB-C插入損耗進行補償的設計。從圖1和圖2可知,DisplayPort的插入損耗為10.7dB(資料傳輸率8.1Gbps);USB-3的插入損耗為12.8dB(資料傳輸率10Gbps)。

圖2 對桌機/筆電的USB-C插入損耗進行補償設計

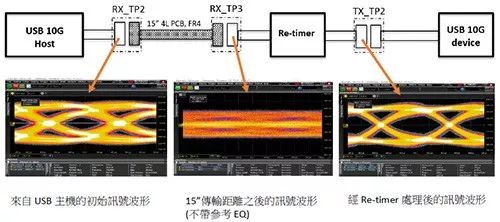

矽谷數模(Analogix)對此進行了一項測試,測試環境如下:

1. USB主機:Gigabyte GB-BSi5HA- 6200

2. 插入損耗板:15英寸(USB-C -micro-USB, FR-4)

3. Retimer(ANX7440)EVB

4. USB設備:Sandisk SSD Plus

5. 示波器:DS0Z334A(33GHZ)

圖3為測量位置與測量結果。安裝了Retimer的系統可望在主機到設備之間對最多23dB的插入損耗進行補償(圖4)。Retimer簡化了PCB布線,可以在不犧牲平台性能的前提下,確保個人電腦主機板和USB/DisplayPort電纜實現高輸送量訊號傳輸。

圖3 USB主機訊號測試示例圖

圖4 安裝Retimer的系統對插入損耗進行補償

DisplayPort訊號改善方案

若要透過主動電纜和菊輪鍊實現多個Retimer之間的無縫互通,須具備功能完備的DisplayPort Retimer,支援鏈路訓練可調PHY中繼器(LTTPR)模式和帶AUX Snooper的透明模式。

USB-A/USB-C訊號改善方案

使用菊輪鍊連接多個Retimer可以在通用連接系統中實現多功能的USB-C互聯。USB-C菊輪鍊提高了擴展USB-C電纜的訊號完整性。USB 3.2附錄E可確保以菊輪鍊形式連接的多個Retimer之間的無縫互連,若要滿足此標準,須在USB 3路徑部署採用SRIS或BLR架構且能夠進行23dB損耗補償的Retimer。USB 3.2規範附錄E的E.1.2.1.2小節給出了Retimer連接模型的要求,該規範支援Pending_HP_Timer_timeout配置下的4-Retimer連接,適用於10-μs USB 3.2主機和設備。

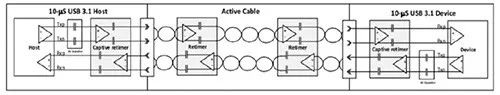

4-Retimer連接指10-μs主機或設備與另一個10-μs主機或設備的連接。在這種情況下,最多可使用四個Retimer,圖5顯示了一個4-Retimer連接,其中包括一個10-μs主機和一個10-μs USB 3.1設備,它們之間透過一條主動電纜連線。而針對下一代10Gbps筆電與桌機的Retimer應可實現4-Retimer菊輪鍊連接功能,滿足最新的USB 3.2規範附錄E的要求,以滿足USB 3.2 CTS互通測試要求的前提下,對USB 3.1 Gen 2 10Gbps訊號高達23dB的通道損耗進行補償。

圖5 10-μs主機與10-μs設備間的連接

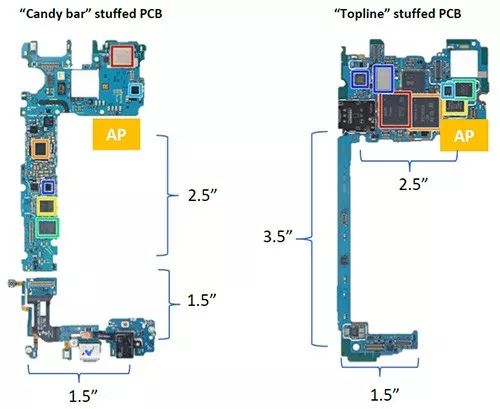

中繼器不僅用於尺寸較大的PCB電路板和較長的傳輸路徑,還可用於尺寸非常小的平台,比如智慧手機。理由如下:

1. CPU晶片組無法為各通道提供足夠的輸出驅動。

2. 部分通道會經過訊號損耗較大的PCB區域。

3. 天線附近的電磁干擾限制訊號的強度。

4. 與接頭相連的電纜會增加通道長度。

智慧型手機訊號改善方案

智慧手機會連接不同的外接顯示裝置,也會連接各種配件。如果不使用Retimer,智慧手機內部電路板的DisplayPort 1.4介面的損耗將為8到10dB,USB 3.2介面損耗將為10到12dB,這些損耗會導致智慧手機內部電路板性能下降,進而使DisplayPort 1.4資料傳輸率下降至5.4Gbps以下,使USB 3.2資料傳輸率下降至5Gbps以下。所以,應用處理器(AP)製造商通常建議將Retimer用於DisplayPort 1.4和USB 3.2的資料傳輸。

而針對下一代智慧手機設計的Retimer必須支援在各種長度的電纜上進行DisplayPort 1.4(8.1Gbps)和USB 3.1 Gen2(10Gbps)的高頻寬資料傳輸。智慧手機通常採用高速USB-C介面,而下一代應用處理器在Retimer的幫助下可在USB-C接頭上實現極高的資料傳輸率,使得智慧手機成為實現VR應用的理想選擇,因為連接頭戴式VR顯示器要求同時支援DisplayPort和USB 3傳輸,以通過細長電纜傳輸刷新頻率為90Hz、解析度為4K×2K的視訊訊號。

智慧手機連接到USB-C介面的監視器時通常使用DisplayPort替代模式,其有兩個資料通道,在60Hz刷新頻率下最高可達4K解析度。如果是連接USB-C配件,則通常為DisplayPort到HDMI連接,在60Hz刷新頻率下可實現4K解析度和USB 3的資料傳輸率。Retimer能夠在上述高資料傳輸率情況下確保資料完整,並保障主機到同步設備間的影像與資料傳輸。

電纜訊號改善方案

為外殼處的接頭部署中繼器或在接頭外殼內部署中繼器時,可以使用較細較長的電纜。主動電纜在接頭內的PCB上部署了中繼器。目前市場提供用於連接USB、DisplayPort、HDMI、PCI Express、SATA和SAS等介面的主動電纜(圖6)。

圖6 主動電纜接頭內的PCB上部署中繼器

針對長電纜情況,Retimer可以在長度為2公尺、5公尺甚至7公尺的主動電纜的兩端進行訊號復原,使得低成本電纜解決方案能夠滿足高速DisplayPort和USB 3.2訊號傳輸的性能和相容性方面的要求。

Retimer供應商須與主流CPU和AP提供商密切合作,努力確保其訊號改善產品滿足鏈路訓練要求,提供所需的相容性通道,並共同設計類比模型,以進一步改進設計,提高在高速介面使用Retimer的成功率。

-

中继器

+关注

关注

3文章

445浏览量

29631 -

传输速率

+关注

关注

0文章

52浏览量

16997

发布评论请先 登录

IDT信号完整性产品:解决高速信号传输难题

SI合集002|信号完整性测量应用简介,快速掌握关键点

使用MATLAB和Simulink进行信号完整性分析

Cadence工具如何解决芯粒设计中的信号完整性挑战

网络延迟具体是怎样影响电能质量在线监测装置的实时性和完整性的?

是德DSOX1204A示波器在电源完整性测试中的关键优势

普源DHO5058示波器在信号完整性测试中的表现

了解信号完整性的基本原理

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

电源完整性基础知识

信号完整性测试基础知识

使用罗德与施瓦茨RTE1104示波器进行电源完整性测试

关于中繼補償傳輸通道耗損 Retimer確保訊號完整性的介绍和回顾

关于中繼補償傳輸通道耗損 Retimer確保訊號完整性的介绍和回顾

评论