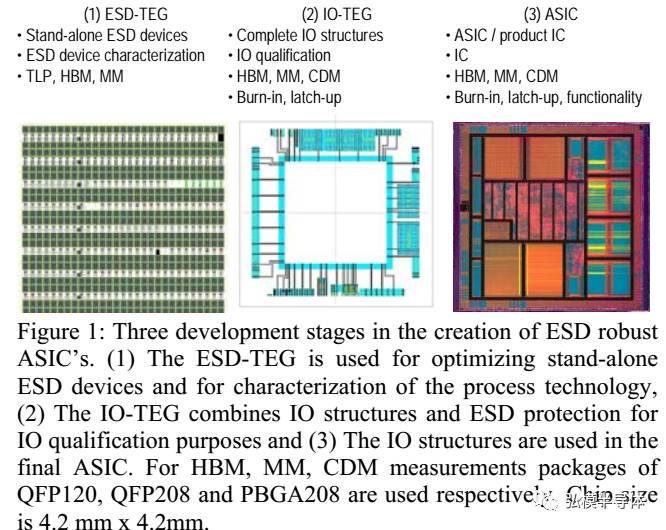

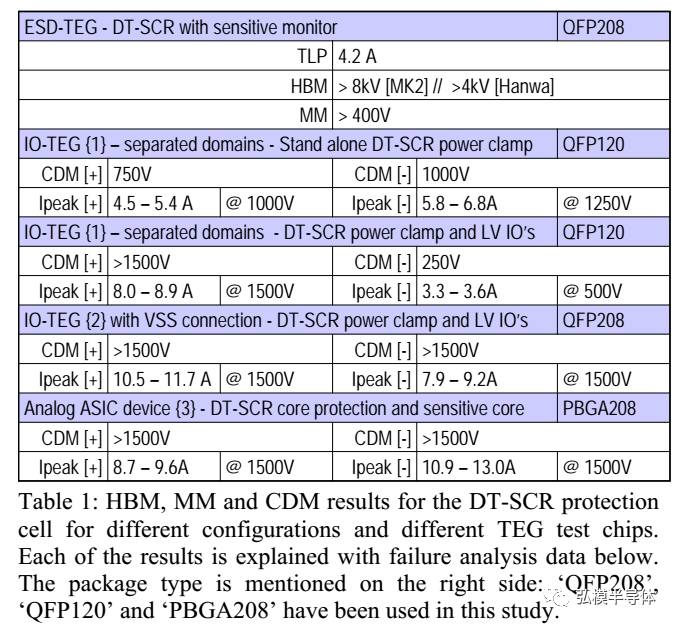

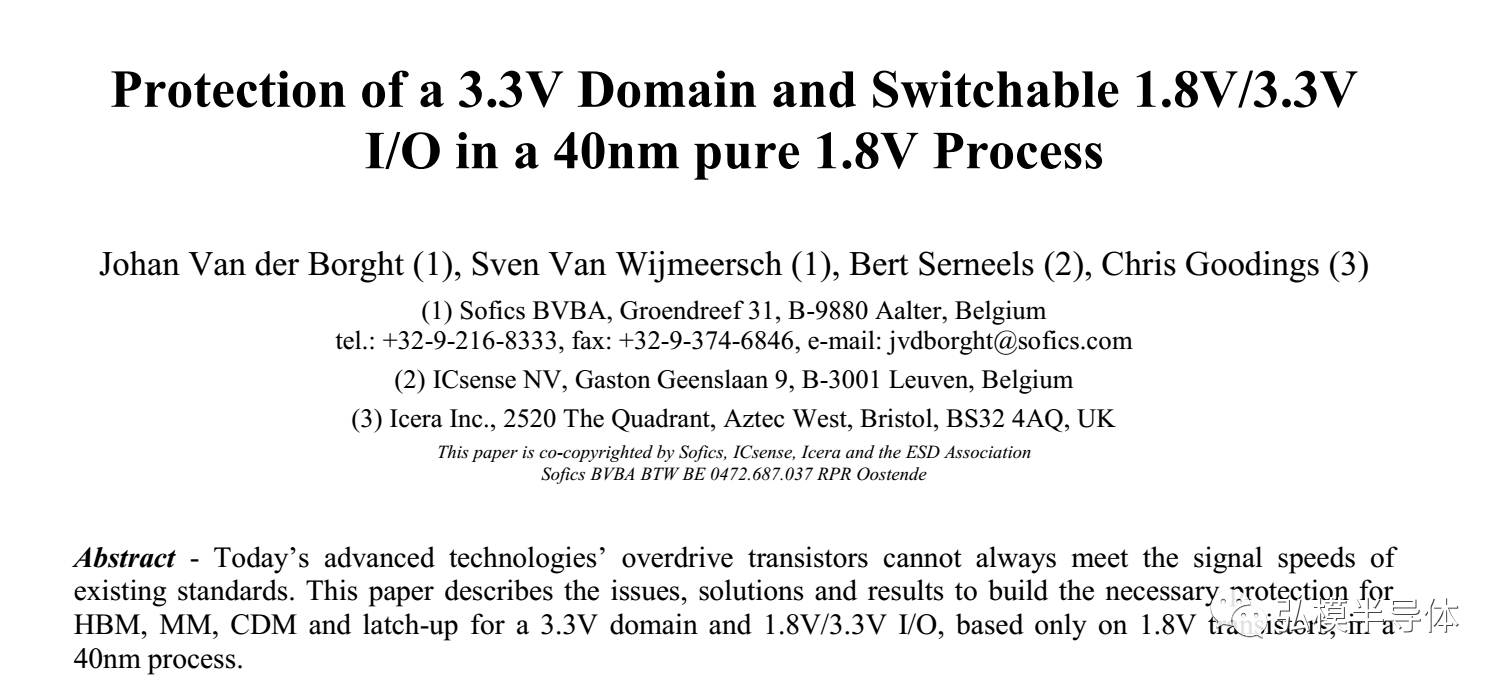

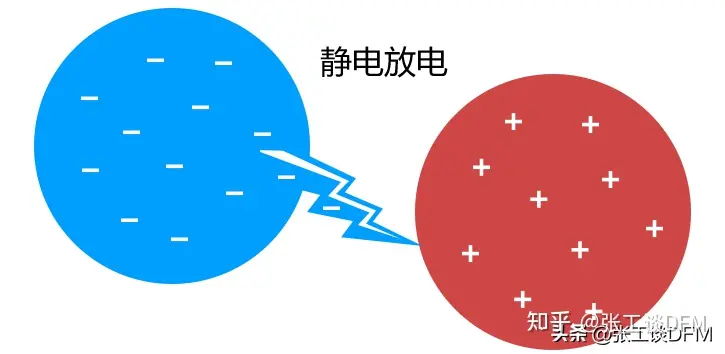

和on-chip ESD 中的HBM,MM不同,CDM的指标与IC layout ,封装,BONDING TYPE强相关。 因此很多IC公司会在一个测试芯片上,制作一个和实际产品相近的IC IO RING来选择最优的CDM方案。随着技术节点的减小和面对各种新型消费,工业产品,对ESD的要求变得更多样和更强大。 特别重要的是,first-time-right IC release对设计公司来说,越来越迫切,在这里,我们引用SOFICS的一些文章来介绍在CDM这块和设计公司共同合作的成果。 比如下面的这篇文章讲述了在引用了公司的ESD结构,在富士通的工艺线上的IO TESTCHIP上做不同的实验后,共同验证了对于CDM的性能影响是多方面的。

在这些不同的测试让我们得到以下结论,在同样的on-chip ESD 结构下:

DT-SCR ESD 结构在LV IO DOMAIN 里面还是外面有比较大影响

2. 通过低电阻的VSS和SUBSTRATE相连,可以大幅提高器件CDM 性能

3. 使用低电阻的衬底也会大大改善CDM性能

4. 单单通过IO TESTCHIP CDM测试,会误判内部核心器件的静电保护能力

更多此类的文章可以参考:

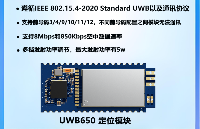

公司在on-chip ESD 领域给客户提供私人定制的需求,比如高速,高压,超低功耗等等,工艺覆盖所有半导体厂主流工艺并且IP转移非常方便。在给客户解决ESD和IO 方面问题的同时,帮助客户省芯片面积,省MASK,提高性能和TIME-TO-MARKET。

-

半导体

+关注

关注

335文章

27926浏览量

224868 -

低功耗

+关注

关注

10文章

2429浏览量

103999 -

静电保护

+关注

关注

1文章

197浏览量

19377

发布评论请先 登录

相关推荐

ESD静电保护器件选型及供应厂商选择

ADS1299的模拟输入IN1P~IN8N,这些引脚需要加ESD静电保护吗?

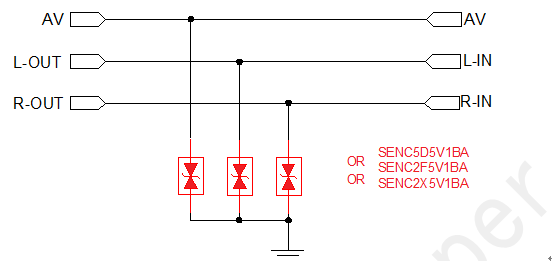

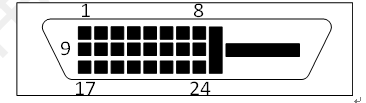

音视频转换器AV接口静电保护方案

静电保护二极管什么用途

静电保护二极管有极性吗

关于静电保护(ESD) 中的CDM需求的发和应用

关于静电保护(ESD) 中的CDM需求的发和应用

评论