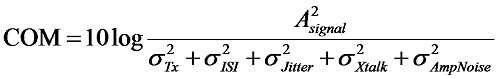

COM(通道操作裕度)将多个测量值组合成一个类似于信噪比的品质因数,类似于ENOB(有效位数),用于表征模数转换器。使用COM,边距越大,通道越好。因为COM是根据不同的测量结果构建的,并且包含了模型的结果,所以有很多方法可以使它失败。

当我们介绍这个新的可观察时,我们应该回顾一下我们如何处理类似的情况差不多15年前:抖动。

与COM相比,抖动似乎很简单:信号转换时间相对于理想的变化。很容易将分布视为这些时序变化的直方图。图1显示了示波器如何在眼图中显示抖动,现在它使用直方图来表征抖动。

图1.示波器可以为您提供抖动分布(来源:Teledyne LeCroy)。

总抖动的错误

Peak-to - 时钟数据表已经出现了几代的峰值抖动,结果证明是不合适的。来自随机过程的抖动 - 主要来自SerDes参考时钟内的相位噪声 - 随时间变化;测量峰峰值抖动的时间越长,得到的抖动就越大。在这一点上,我们这些推动高速串行数据技术标准的人遵循了Yogi Berra的建议:“当你走到路边时,拿走它。”

远离定义不明确的,不可能再现峰峰值抖动,我们做出了合理的选择,将BER(误码率)纳入新数量的定义TJ(BER)(BER定义的总抖动)。 TJ测量给定BER下的闭眼,也就是说,如果TJ(BER)小于指定BER的位周期,那么你有一些抖动余量,你应该没问题 - 这是峰值的理想特征 - 达到峰值测量。

听起来很棒!周围喝酒,对吗?

好吧,因为我们关心的BER非常低,1E-12到1E-18,TJ(BER)结果需要很长时间来测量并且是唯一的可以测量它的设备,BERT(误码率测试仪)非常昂贵,而且对于诊断实验室中的其他问题并不是那么有用。因此,我们开发了可以快速进行测量来估算TJ(BER)的技术,但这导致了一个巨大的问题;你可以称之为clusterjitter。外推技术依赖于示波器测量抖动的独立组件的能力:RJ,DJ,ISI,PJ,DCD,以及您知道或希望忘记的几个缩写。

不同的测试 - 和 - 测量公司开发了不同的方法,测量结果不一致。从2000年到2006年,来自不同T& M公司的设备 - 您知道并依赖的公司以及制造出色设备的公司 - 至少相差30%且经常超过100%。直到2004年,任何人都组装了一个系统,可以准确地区分哪些结果是正确的,哪些是错误的。

问题来自于我们如何选择将RJ,DJ,ISI,PJ等搅入我们估计TJ(BER)的炖牛肉。通过从相互依赖的数量的g building建立TJ(BER)(图2),我们无法确定进入炖牛肉的测量中的错误。你看,如果你改变了ISI的数量,你也改变了RJ。添加串扰,所有投注均已关闭。

图2.调整相互依赖变量的数字很难,COM是一个炖牛肉。

当我们从几Gbits/s前进到10+ Gbits/s ,ISI(符号间干扰)是最大的问题。 ISI是由频道的频率响应引起的;它将信号的幅度和定时偏移量取决于发送符号的顺序。这让我们看到了COM以及历史重演的可能性。

早在2003 - 2004年,当时安捷伦科技公司的一群人构建了一个精密抖动发射器,并提供了所有抖动分析仪。所有的测试和衡量公司的工作。我们将精确数量的RJ,PJ,ISI和DCD用于炖牛肉(随机抖动,周期性抖动,符号间干扰和占空比失真),进行了数百次测量然后......我坐在客厅的平静处确定最好的技术。我遇到的最大问题是成分太多了。尽管我非常精确地知道每种类型的每种类型的抖动有多少,但是没有办法确定为什么不同的技术失败(它们都失败了!)。

为了理解测量结果,我必须做基础科学:从我们可以构建的最干净,最低抖动系统开始,然后一次注入一种类型的抖动,比较结果,然后添加第二种类型的抖动,依此类推。花了六个整整一周的时间来分析数据并发现哪些技术是准确的以及为什么。经过两年多的时间,T& M行业开始在10-15%的范围内汇聚成结果 - 整个行业已经混淆了五年多,至少有一家公司因为未能准确生产而停业结果。

回到COM,从几个原因中产生的单一品质因数可以在不牺牲互操作性的情况下实现设计灵活性。这种组合 - 灵活性和互操作性 - 是技术标准的圣杯。没有人希望标准类似于技术社会主义,但每个人都希望它能确保互操作性。答对了! COM。

除非我们遇到与抖动相同的问题。

COM由信号幅度与集体信号损伤之比给出。它包括来自信号通道的损伤,所有串扰干扰源通道以及标准委员会可能想到的所有其他损伤源。

-

电路

+关注

关注

172文章

5936浏览量

172476 -

PCB打样

+关注

关注

17文章

2968浏览量

21742 -

华强PCB

+关注

关注

8文章

1831浏览量

27812 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43088

发布评论请先 登录

相关推荐

波形出现震荡带来的影响怎么避免

【原创视频】如何避免OCL电路交越失真设计

【原创视频】旋变驱动电路OCL电路避免交越失真设计

如何给视频进行防抖动处理

如何避免“断头线”带来的DFM(可制造性)问题

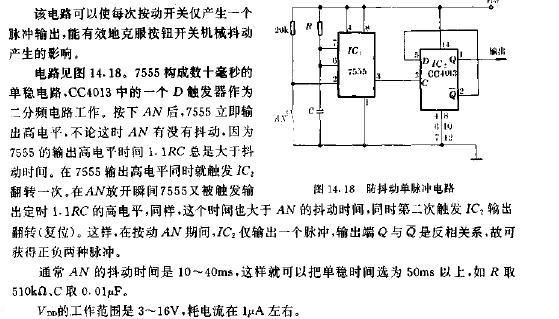

去抖动延时可调键盘电路的设计

图像抖动跟踪数据处理技术

扇出缓冲器中的附加抖动计算

高速ADC在低抖动采样时钟电路设计中的应用

如何避免抖动给电路带来的影响

如何避免抖动给电路带来的影响

评论