新的每秒10千兆位USB 3.1合规套件可以节省几周的时间,使其有资格获得USB-IF集成商列表

加利福尼亚州圣何塞, Jan。 20,2016 /PRNewswire/- Cancence Design Systems,Inc。(纳斯达克股票代码:CDNS)今天宣布推出Sigrity™2016技术组合,通过增强的PCB设计和分析方法改善产品创建时间是多千兆位接口的理想选择。

为加快USB实施者论坛(USB-IF)一致性测试的物理设计认证, Cadence®Sigrity技术组合包括自动支持IBIS-AMI模型创建,使用多个场解算器快速准确地提取信道模型,以及自动功率感知信号完整性分析报告,以验证虚拟USB 3.1通道。这些技术在一起使用时可以在设计过程中花费数周时间。

以前,IBIS-AMI模型创建是一个手动过程。 Sigrity 2016技术组合现在利用Cadence Design IP SerDes PHY团队使用的经过验证的均衡算法,并提供了一种自动化方法,用于将算法组合,参数化和编译为可执行模型。这可以增加能够有效开发SerDes I/O模型的工程师库。

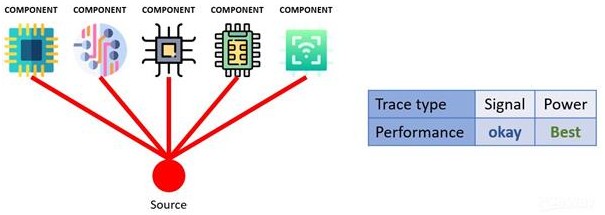

新的“剪切和缝合”技术通过混合使用混合和3D全波场解算器,能够以十倍的速度创建精确的通道模型。通过最少的手动干预,串行链路通道可以分为多个部分,解决并自动拼接成单个互连模型。快速模型提取技术使工程师能够权衡各种信号路由和层转换策略,并且仍能满足苛刻的上市时间要求。

在产品组合中增强的其他功能包括:

集成了3D全波和混合求解器技术的新型准静态三维场解算器,可用于IC封装和PCB分析

电气性能评估直接集成到IC封装设计器的布局环境中

针对Allegro®PCB布局更新的优化去耦电容器方案

改进PCB设计人员的电源完整性分析方法

"Sigrity 2016产品组合具有提高效率和加快设计过程的功能,使设计人员能够认证多千兆位标准接口,例如: USB 3.1,“C的副总裁Vinod Kariat说Cadence的ustom IC和PCB Group R& D.“这些功能消除了使用软件开发环境手动编写和编译代码以创建SerDes I/O模型的需要,并使收发器和互连的建模更快。”

“我们与Cadence的合作使两个工程团队都能够开发出可以改善我们共同客户产品创建过程的工具.Sigrity 2016版本与我们客户的需求保持一致,以解决串行链接分析挑战“我们可以帮助我们的共同客户缩短设计周期,因为他们使用Sigrity解决方案对USB 3.1接口进行原型设计并在实验室使用泰克解决方案。“

-

PCB打样

+关注

关注

17文章

2983浏览量

23719 -

华强PCB

+关注

关注

8文章

1831浏览量

29362 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44760

发布评论请先 登录

用于Xilinx Ultrascale Kintex FPGA多路千兆位收发器(MGT)的电源解决方案

千兆位数据传输的信号完整性设计

基于Sitara AM57x千兆位以太网EtherCAT主接口解决方案

千兆位设备PCB的信号完整性设计

深入分析探讨多千兆位串行链路接口的SI方法

千兆位设备PCB系统的信号完整性以及电磁兼容设计

FPGA自动符号生成节省PCB设计创建时间

如何利用PCB设计改善散热资料下载

利用PCB设计和分析方法为多千兆位接口改善产品创建时间

利用PCB设计和分析方法为多千兆位接口改善产品创建时间

评论