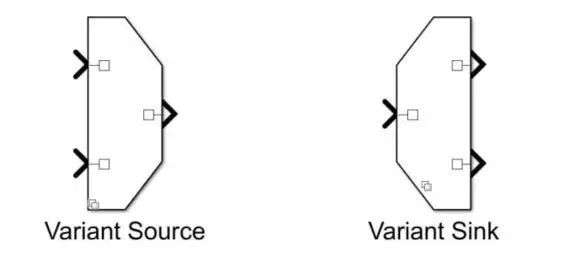

上次介绍过可以使用Variant Subsystem或者Model Variant实现带有条件编译的代码(条件编译助力Simulink模型平台化开发)。最近了解到,从MATLAB R2016a开始,又有一种新的方式可以实现C代码中的条件编译。这就是Variant Sourc模块的使用。

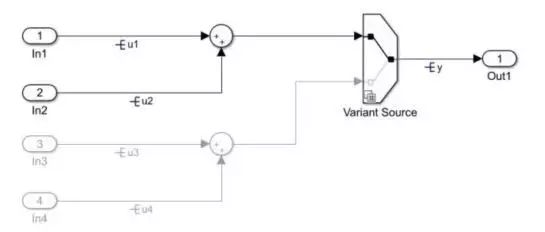

假设有如下模型:

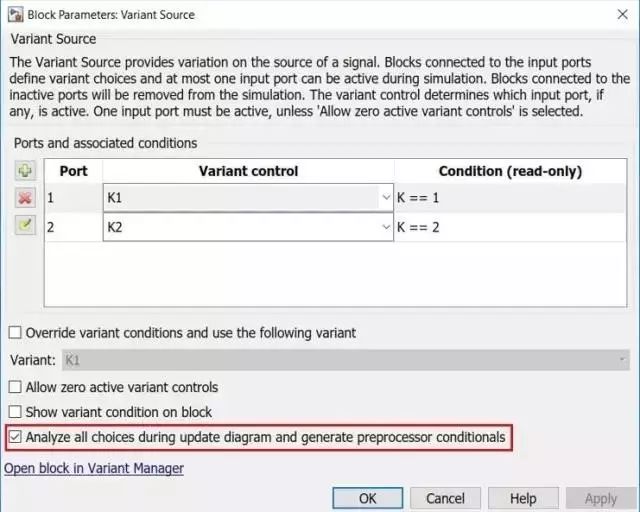

双击Variant Source模块,可以看到如下配置界面:

不难看出,除了要定义Simulink Variant对象K1、K2之外,还需要勾上Analyze all choices during update diagram and generate prepropcessor conditionals选项。显然,如果K==1条件成立,则Port 1分支对应的代码被编译,如果K==2,则Port 2分支对应的代码被编译。这里的K可以定义为Simulink Parameter对象,Storage Class定义为Define(Custom),并且需要指定宏定义的文件。

如此设置之下,得到的模型算法实现函数如下:

voidtestvariantSource_step(void)

{

real_T rtb_VariantMerge_For_Variant_So;

#ifK1

rtb_VariantMerge_For_Variant_So = u1 + u2;

#endif

#ifK2

rtb_VariantMerge_For_Variant_So = u3 + u4;

#endif

y = rtb_VariantMerge_For_Variant_So;

}

这种方式实现带有条件编译的代码也非常简单,条件编译的好处可以通过控制宏定义K控制需要编译哪部分代码,那么,如果不设置条件编译呢?

上述模型中,如果不再勾选Analyze all choices during update diagram and generate prepropcessor conditionals选项,我们得到如下代码:

voidtestvariantSource_step(void)

{

y = u1 + u2;

}

代码中只有当前参数条件下有效算法的代码。

跟上次介绍的条件编译相比,实现方式不同,应用场景也可能不同,如何取舍,这里就不去分析了。但是,在基于模型的开发模式下,到底在模型级别上做选择,还是通过C代码级别的条件编译做选择,这是个值得我们思考的问题。

-

代码

+关注

关注

30文章

4841浏览量

69225 -

编译

+关注

关注

0文章

663浏览量

33101

发布评论请先 登录

相关推荐

VirtualLab Fusion案例:K域和X域中的系统建模

使用OpenVINO™条件编译功能,压缩Windows应用体积

一种利用CSD16327Q3实现企业固态硬盘钽电容短路保护的方法

LIDAR激光雷达逆向建模能用到revit当中吗

对放大电路的分析方法介绍

一种无透镜成像的新方法

关于一种实现条件编译的建模方法分析和介绍

关于一种实现条件编译的建模方法分析和介绍

评论