所有大型晶圆代工厂都已宣布FinFET技术为其最先进的工艺。Intel在22 nm节点上采用该晶体管1,TSMC在其16 nm工艺上使用2,而Samsung和GlobalFoundries则将其用于14 nm工艺中3。与所有新工艺一样,对于IC设计人员来说最重要的问题是“这对我意味着什么?”新的,更小的工艺意味着设计人员将可获益于更低的功耗、更高的面积利用率以及源自半导体缩放的其他传统的改善。但除了这些优势外,还存在着一定的学习成本,以了解新的设计规则、参数差异,以及必须实施才能在新节点进行设计的新方法或改进的方法。目前为止,收益总能证明成本的价值所在。对FinFET来说也是这样吗?

与其他所有新技术一样,FinFET工艺包含一种与学习如何使用其进行设计相关的成本。由于FinFETs是一种完全不同的晶体管,问题变成,这种改变是渐进的(典型学习成本)还是革命性的(显著学习成本)。答案取决于你的观点…

渐进

首先要记住的是,对于大多数晶圆代工厂来说,16nm和14 nm的后道工序(BEOL)结构与20 nm节点的一样。20 nm采用了双重曝光(DP)4,对设计和制造界产生了极大影响。DP推动了设计流程的变化,是EDA工具在设计、验证、寄生参数提取和分析方面变化的催化剂。

幸运的是,DP的挑战就发生在最近。三重曝光或多重曝光业已到来,但并非用于现有的FinFET工艺。由于BEOL与20 nm相同,设计人员最需学习并了解前道工序 (FEOL)几何形状的变化。图1是具有单“鳍片”的FinFET器件图示,当然大部分FinFET器件都有多鳍片。

图1:单“鳍片”FinFET。

(信息来源:GLOBALFOUNDRIES)

第一次看到这些器件时,大部分设计人员会问以下问题:

1.如何设计?

2.一个器件应包含多少鳍片?

3.鳍片尺寸/间距应该是多少?

4.如何获取所需信息来了解几何形状与电气性能的折衷方案?

这些都是棘手的问题!通常,设计人员,尤其是数字设计人员,在权衡晶体管结构和电气性能时将宽度、长度和面积作为参数进行考量。FinFET设计的性质可能极大地改变这一切。幸运的是,大多数晶圆代工厂已考虑到这一点,并为FinFET工艺开发了一种与20nm及以上工艺相同的设计方法。

没错,对于这第一代FinFET,设计人员没有设计/开发鳍片(除非是SRAM设计人员)。如同之前的节点,IC设计人员将会通过定义器件的宽度、长度和面积来设计晶体管。设计、验证、提取和分析工具将根据晶圆代工厂的规范将版图分解为鳍片,然后执行必要的分析来进行物理验证、参数和寄生计算,甚至是执行几何形状填充和电路仿真。

通过这些EDA创新,如果你是即将采用FinFET工艺的数字设计人员且最近的节点是20nm,那么FinFETs只不过是一种渐进的变化。BEOL没有新的内容,物理设计在很大程度上仍旧保持不变,而EDA工具负责执行必要的分析。

革命性

图2更加真实地描述出了FinFET,用弧形代替了之前示例中的方框和平面。大部分设计人员都同意,预测这种结构的电气性能需要重大创新。器件及其互连周围的电场比他们在传统MOSFET中遇到的要复杂得多。另外,FinFET器件的驱动能力比同样尺寸的MOSFET更强,这意味着设计人员在预测电气行为方面将需要更高的精确度。为满足这些要求,就需要新的技术来进行器件和其互连的建模。

图2:弧形结构的FinFET图示(TEM图片来源:ChipWorks;仿真来源:Gold StandardSimulations Ltd.)

另外,从模拟或IP设计人员的角度来看,上述设计方法(鳍片由晶圆代工厂实施)并非首选模型。这些设计人员希望能获得更大的自由度,以减少渗漏、匹配驱动能力、提高频率响应以及推动电气和几何限制,而这些都是固定鳍片无法做到的。根据其性质,这种设计是定制的,而无法控制鳍片数量或大小对于其中很多设计人员来说是非常别扭。

对于从28nm或以上工艺跳到FinFET工艺的定制、模拟或IP设计人员来说,这种设计是革命性的,但不一定是字面上的“全新改良”。虽然有工具创新来缓和这种过渡,进行这种设计的方法与其习惯的设计手法相比可能更显严格。采用传统MOSFET工艺,这些设计人员设计定制化的晶体管包括定制其尺寸和方向。对于FinFET,设计人员将通过更少的变量来达成所需的电气响应。有人怀疑是否可以通过FinFET 工艺来完成先进的模拟设计,而关于此问题,已经有很多人讨论过了。答案是肯定的,但需要对设计方法进行重大改变,且可能需要更多的实验。

-

电路设计

+关注

关注

6678文章

2456浏览量

204649 -

晶圆代工

+关注

关注

6文章

859浏览量

48612

发布评论请先 登录

相关推荐

射频分析仪的技术原理和应用场景

硬件电路设计的思路介绍

如何在电路设计中优化电阻

元器件在电路设计中的重要性

求助,关于LM386芯片内ESD保护电路设计和引脚分配情况求解

上海 10月25日-26日《硬件电路设计、调试与工程案例分析》公开课即将开始!

快恢复二极管在电路设计中的应用

对放大电路的分析方法介绍

multisim中逻辑分析仪怎么连接

蓝牙模块的工作原理与电路设计

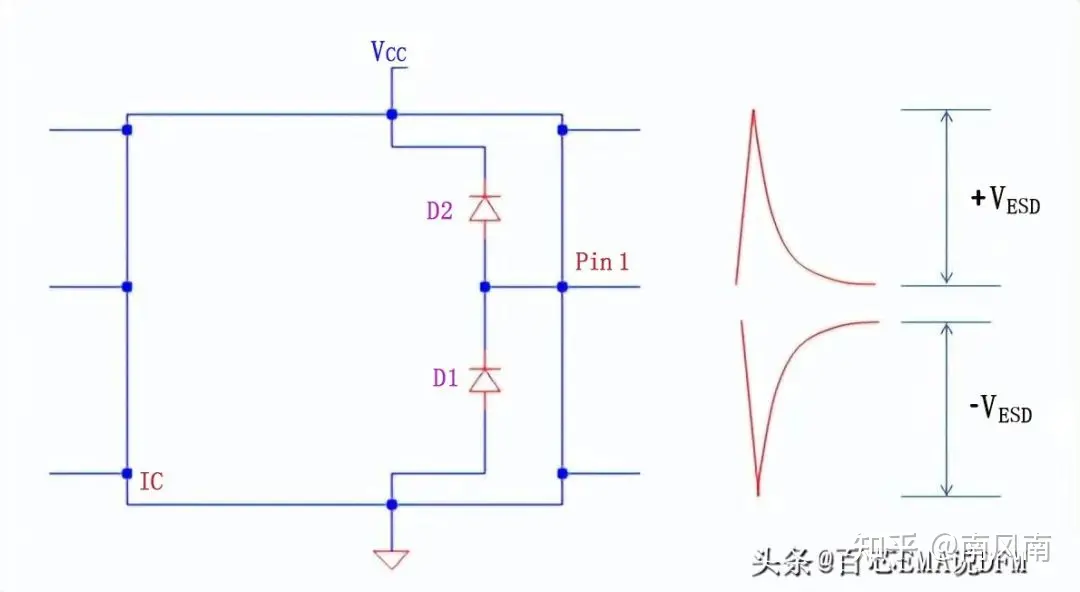

电路设计中如何减少ESD?

关于FinFET技术中的电路设计的分析和介绍

关于FinFET技术中的电路设计的分析和介绍

评论