显然,无论是功能丰富的高端工具还是基本的入门级工具,常年使用同一种EDA工具都能提高效率。人们往往会习惯于自己所用的PCB设计工具,接受该工具的所有优缺点。但是,随着技术的快速发展,我们应当考虑做出改变,采用最新的技术方法,从而取得更好的结果。在本期中,笔者将重点讨论阻碍PCB设计流程的生产率问题。

到目前为止,PCB设计工具的选择仍然局限于高端企业级解决方案或是入门级桌面解决方案。前者较为昂贵且因延长了学习和设置时间而导致成本的增加;后者虽然容易上手,但功能有限并且容易出错。Mentor Graphics的新PADS Professional可提供这两种解决方案的最佳版本,完美解决这一问题。PADS Professional以久经验证的Xpedition技术为基础,注重易于获取、易于使用和性价比高等特点,并且仍然包含当今设计人员进行最复杂的设计所需的全部功能。

通常,基于高速计算机的设计采用两次或三次迭代进行工作产品开发。但是,现在的产品生命周期都非常短,因此上市时间才是关键所在。依据您的研发投入,一次电路板迭代也可能代价高昂。我们不应只考虑工程设计时间,还要考虑产品上市延迟所造成的成本。若错失机会,您的公司即使没有失去全部市场份额,也可能损失数十万美元。

在之前的专栏(板级仿真和PCB设计流程简介)中,笔者曾提到过,若在设计周期中采用仿真,将能大幅降低开发成本。相比在大规模生产后进行更改,在设计流程初期进行设计更改的成本要低得多。更改成本随着开发时间的增加而增加。

基本上,设计更改可以分为生产前修改和生产后修改。生产前更改通常发生在概念、设计、样机制作或测试阶段。生产后更改则发生在产品投入生产时,或者甚至是在产品上市后。越晚进行更改,修复问题的代价就越大。虚拟原型的优势在于,它可在设计流程初期发现问题,因此能及时进行更正,以免其演变为重大问题。

多年来,入门级工具让我们可以快速进行设计以及构建原型,其中一些是基于芯片供应商的参考设计进行的。遗憾的是,这种日子已一去不复返,开发团队发现,他们需要采用分析工具,以在发布前对其设计进行验证。他们无法将这些参考设计应用于实际的操作环境中。因为,这些设计通常由具有高学历水平、但缺乏可性或可制造性设计意识及真实体验的研发团队打造。

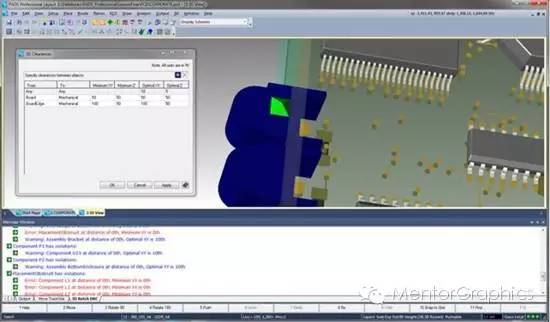

当今设计环境中,随着每项新技术的采用,多个快速上升时间信号以越来越快的速度进行传递,这种在线设计、查找并修复的方法在这样的环境中显得尤为重要。我们无需再构建原型、进行测试、然后对必要之处做出修改。包括信号和电源完整性、热分析、DFM和三维干扰验证等在内的虚拟原型,不仅可以减少改版次数,而且对于设计效率也至关重要。图1显示的即为三维干扰验证。我们可以设置三维间距,然后三维间距检查即可显示违规情况,并自动放大所选设计不妥之处。

图 1:三维干扰验证。

若使用入门级工具,往往要拥有一定技能的工程师和PCB设计人员方能检测出设计流程中出现的潜在问题。但是,现在需要约束驱动型、“设计即正确”的方法来进行复杂设计。创建好规则后,下游工具将遵循这些规则,并由各种设计规则检查器 (DRC) 验证是否符合要求。

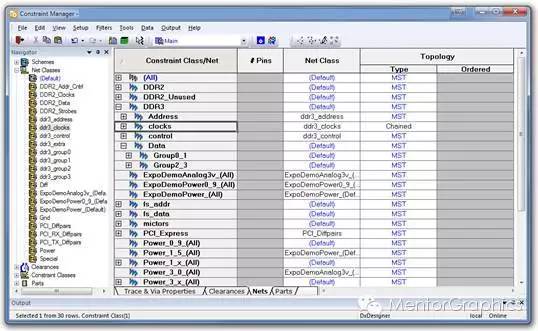

图2说明了典型的约束规划和高速DDR2与DDR3设计的定义。约束应当在原理图级别进行定义,并在Layout流程中一直沿用。这种方法的优势在于,工程师能准确无误地将其意图传递给PCB设计人员。或者,独立工程师(全程包办的工程师)可以在整个设计流程中使用同样的约束管理工具对约束进行管理。另外,从之前已经验证的设计中复用约束不仅可以确保应用一致的规则,还可以最大限度地降低错误率。

图 2:原理图级别的约束规划。

网络类用于组织和加快具有类似属性的网络的布线约束定义。对于每个网络类,您可以定义允许布线的层、这些层对应的走线宽度范围,以及允许的过孔类型。对于差分对,可以根据计算的阻抗定义层相关的差分对间距,以确保各层之间的阻抗一致。

在设计流程的早期阶段对网络类和约束类进行正确的分组和定义,可显著简化约束的定义和管理。分组约束可提高PCB设计效率,缩短设计时间,以及最终降低PCB设计成本。

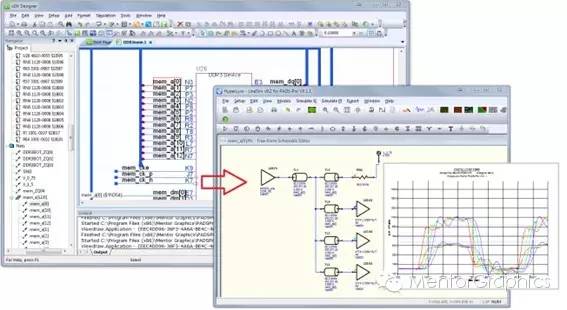

布线前仿真允许设计人员在设计流程的早期阶段预测并消除信号和电源完整性、串扰和EMC问题。对于设计具有更少迭代的电路板而言,这种方法最具成本效益,而不用从布线后仿真开始更改。我们可以快速仿真复杂的互连场景,包括IC、传输线、连接器和无源元器件,以确定哪种场景最适合特定设计。

集成的“设计即正确”元器件库还可确保在定义元件后,立即同步更新符号、单元和元件映射。这种方法消除了网表驱动型设计模式中常见的导致设计迭代的主要因素。

除了使用信号和电源完整性分析工具外,大多数设计人员仍然凭眼力查找Layout中的多处不一致性。例如,HyperLynx DRC可以验证不易仿真的复杂设计规则,比如EMC约束。利用针对诸如跨越分割平面的走线、参考平面变化、屏蔽和过孔检查等项目的DRC,我们可以快速检测并更正可能在后期造成间歇性信号和电源完整性问题的问题。我们也可以自定义DRC,从而允许用户为其可能手动进行的、以消除人为错误的所有检查创建约束。

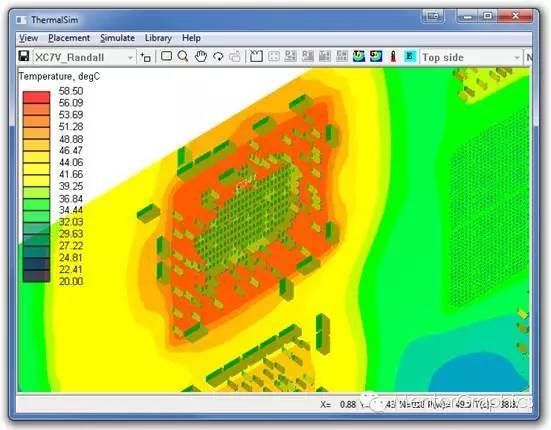

如今,具有亚纳秒级切换时间的高性能处理器采用具有高瞬态电流和高时钟频率的低直流电压,以尽可能减少耗电和散热。但是,快速上升时间、低输出缓冲器阻抗和同步总线切换在电源和接地平面中形成了高瞬态电流。这反而会降低产品的性能和可靠性。在不良操作环境中也存在较高的热失效风险。热分析独立于电源完整性分析,可以检测热点、过热元器件以及可能使产品降级的其他散热问题。其自身可运行热仿真或者通过直流压降进行协同仿真。单独热仿真考虑到了IC和其他元器件的散热、环境气流和环境温度。另外,散热/直流压降协同仿真还包括经过连接稳压器模块 (VRM) 与DC Sink管脚模型的铜线的电流产生的热量。

图 3:导出到LineSim的DDR3存储器地址网络拓扑。

当然,采用当今先进布线技术可以带来令人惊叹的生产率提升,尤其是采用需要您高度注意细节的最新高速DDR4存储器接口时。当为所有关键信号设置定义的约束后,即可完成布线并进行验证,所需时间大大少于手动方法。

总之,使用虚拟原型,包括信号和电源完整性、热分析、DFM和三维验证,现在对于减少设计迭代、满足紧凑的日程以及保持领先的竞争地位都非常重要。但是,成本会是多少呢?我们可以选择能确实完成任务的企业解决方案;也可以考虑使用价格实惠的工具套件,不过这都无法提供处理最为苛刻的设计所需的所有必要工具。是否该考虑更高效的替代方案了呢?

要点:

• PCB 设计工具的选择仍然局限于高端企业级解决方案或是入门级桌面解决方案。

• 通常,基于高速计算机的设计采用两次或三次迭代进行工作产品开发,既耗费工程师的时间,又延迟了上市时间。

• 相比在大规模生产后进行更改,在设计流程初期进行设计更改的成本要低得多。

• 开发团队发现,他们需要采用分析工具,以在发布前对其设计进行验证。

• 包括信号和电源完整性、热分析、DFM 和三维干扰验证等在内的虚拟原型,不仅可以减少改版次数,而且对于设计效率也至关重要。

图 4:PCB 底部热点的热仿真。

• 若使用入门级工具,往往要拥有一定技能的工程师和 PCB 设计人员方能检测出设计流程的潜在问题。需要约束驱动型、“设计即正确”的方法来进行复杂设计。

• 从之前已经验证的设计中复用约束不仅可以确保应用一致的规则,还可以最大限度地降低错误率。

• 网络类用于组织和加快具有类似属性的网络的布线约束定义。

• 设计人员仍然凭眼力查找Layout中的多处不一致性。但是,DRC工具可以验证不易仿真的复杂设计规则,比如EMC约束。

• 热分析独立于电源完整性分析,可以检测热点、过热元器件以及可能使产品降级的其他散热问题。

• 当今先进布线技术可以带来令人惊叹的生产率提升。

-

存储器

+关注

关注

38文章

7513浏览量

163987 -

缓冲器

+关注

关注

6文章

1923浏览量

45527

发布评论请先 登录

相关推荐

衍射级次偏振态的研究

衍射级次偏振态的研究

浅谈关于考虑新能源储能配置下的电动汽车有序充电策略的研究综述

关于欧盟法规中测试场景的研究

优化TC3xx系统运行效率的策略

论文 | PEMFC 热电联供系统能量管理控制策略研究

浅谈综合能源充电站有序充电策略的研究与设计

求助,关于D类功放的几个问题求解

基于峰平谷电价的新能源汽车有序充电策略研究

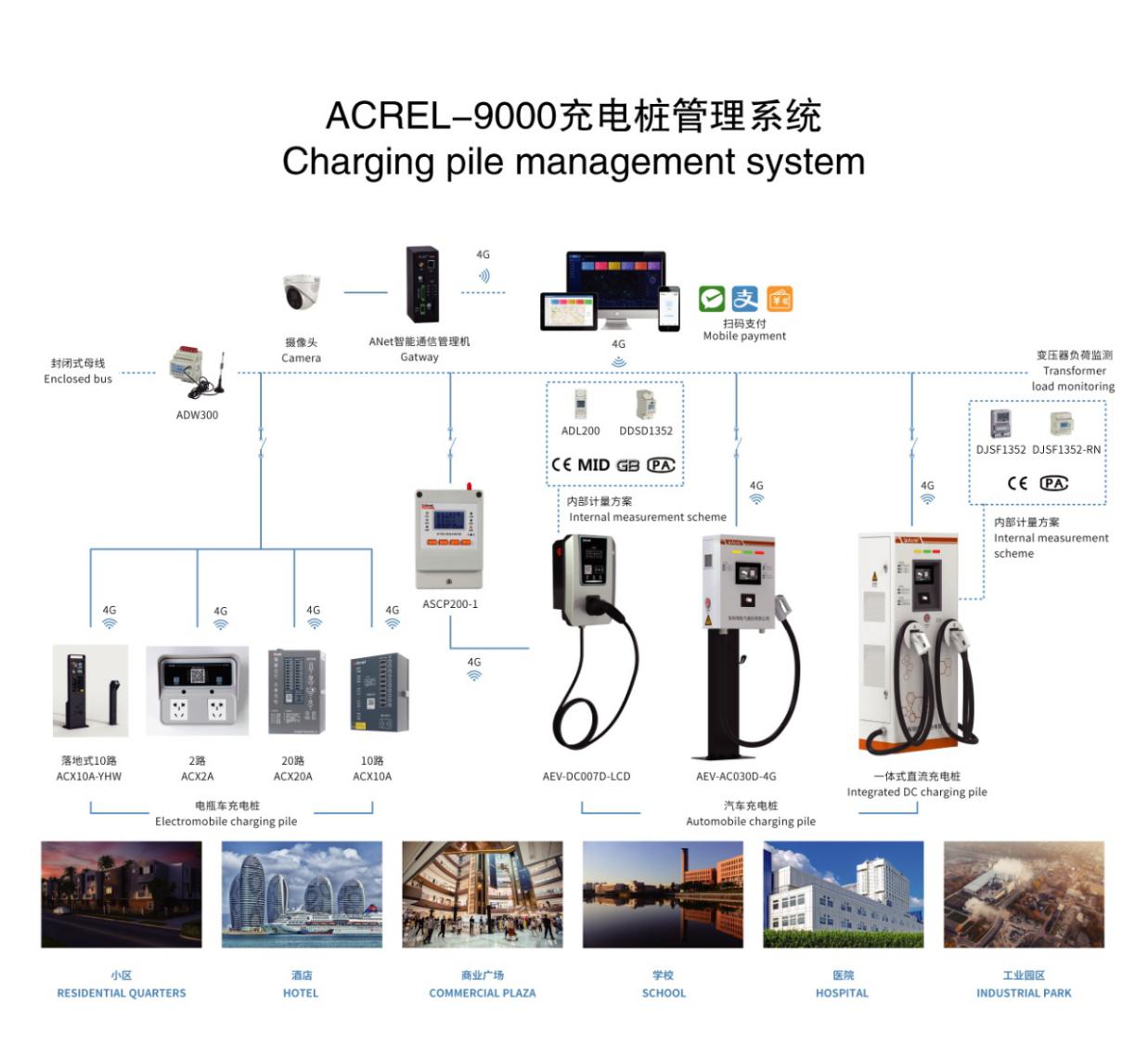

安科瑞综合能源充电站有序充电策略的研究

综合能源充电站有序充电策略的研究与设计

电机控制系统的神经网络优化策略

量子效率测试:Micro-LED量子效率的研究进展

浅谈居民小区电动汽车有序充电策略研究

DC电源模块的节能与环保设计策略

关于设计效率策略的研究和分享

关于设计效率策略的研究和分享

评论