为提高带宽,很多类型的 Memory 都采用了 Double Data Rate(DDR)interface,它对在内存控制器(memory controller)设计过程中的时序收敛和后仿真提出了挑战。

1 引言

Double Data Rate (DDR) 接口在 ASIC 领域应用得很广,尤其在 Memory 领域,从 DDR SDRAM 诞生后 Memory 经历了 DDR2,DDR3 乃至现在主流的 DDR4,它们在数据接口上都使用的 Double Data Rate(DDR)interface[1-4]。DDR interface 是一种源同步接口,时钟(DQS)和数据(DQ)都由发送方提供。读操作时 Memory 提供时钟和读数据,Memory 仅在有数据的时间段内驱动时钟(DQS),时钟和数据是沿对齐(edge alignment),内存控制器(Memory controller)使用收到的时钟(DQS)的上下沿采样数据。写操作时内存控制器提供时钟和写数据且仅在有数据的时间段内驱动时钟(DQS),时钟和数据是中间对齐(center alignment),内存(Memory)也使用时钟的上下沿采样数据。基于这样的协议,通常读操作时内存控制器使用延长线延迟输入的 DQS, 以满足足够的建立保持时间采样读数据。而写操作时,内存控制器需要将输出的 DQS 做一定延迟以使内存有足够的建立保持时间采样写数据。因为是时钟上下沿都需要采样数据,随着 Memory 时钟频率的加快,对时序收敛和后仿真都提出了挑战。

本文介绍了一种通过静态时序分析工具进行时序检查及指导后仿真工作的方法。

2 DDR Memory 读接口

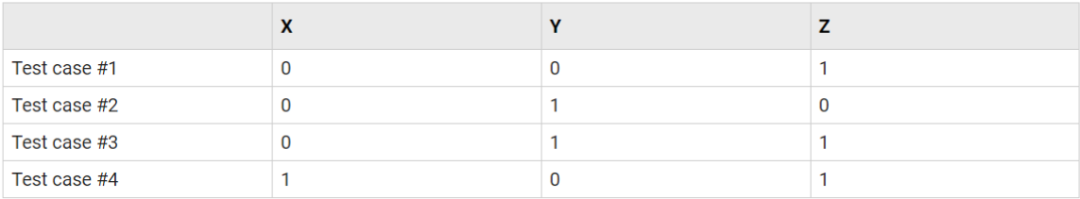

根据 JEDEC Spec,DDR Memory 读的时序如图 1。

DQS 上升沿的参数:① tDQSQ 是最晚有效数据的翻转,它反映着 DQ 的偏移(Skew)。② tDH是最早无效数据的开始,它反映着 DQ 的有效宽度。

DQS 下降沿的参数:① tDQSQ 是最晚有效数据的翻转,它反映着 DQ 的偏移(Skew)。② tDH 是最早无效数据的开始,它反映着DQ的有效宽度。

读操作时 Memory 提供时钟和读数据,Memory仅在有数据的时间段内驱动时钟(DQS),时钟和数据是沿对齐,内存控制器(Memory controller)使用收到的时钟(DQS)的上下沿采样数据。鉴于DDR Memory 这个特性(上下沿都会发送数据),内存控制器一般会使用延长线去延迟输入的 DQS 然后再去采样数据的电路,其结构可如图 2。

根据电路结构,它的时序约束可以如下设置(以 DDR3-1600 为例)。

使用 create_clock 和 create_generated_clock 定义了 Memory 产生的 dqs 经过延迟线延迟后到达 i_rdata_r/f 的 clock。

因为 Memory 既在上升沿发送数据又在下降沿发送数据,所以需要使用下面两条命令来约束输入数据的建立时间(setup time)的要求。

根据时序要求还需要设置输入数据的保持时间(hold time)的要求如下。

“set_multicycle_path 0”反映着图 2 电路的工作机制,i_data_r/f 的采样时钟是经过 delay chain 延迟后的 clock,理论上的建立时间不是通常时序电路中的一个周期,所以设为 multicycle_path=0。

根据上面的时序约束可以在静态时序工具中得到如下的时序报告。pd 到 i_rdata_r 的建立时间(setup time) 报告如下。

从上面报告看到输入数据被发送的时间从 0 ns 开始计算,而被采样的时间也为 0 ns 开始计算,这恰好是符合 i_rdata_r 采样的时钟是来自延迟后的 DQS 的上升沿,随着延迟线延迟的增大,i_rdata_r 的建立时间的余量会越来越大。

pd 到 i_rdata_r 的保持时间(hold time)的报告如下。

从上面报告看到新数据被发送的时间从 0.62 ns 开始计算并且上一笔数据被采样的时间也从 0 ns 开始计算,这也符合电路工作实际情况。延迟线延迟最小时 i_rdata_r 的保持时间的余量最大,随着延迟线延迟的增大,保持时间的余量会越来越小(表 1)。

上面的时序报告描述了 i_rdata_r 的时序情况,i_data_f 的时序报告类似,只是 launch/capture 的时间不同而已,在此不再赘述。

根据上面的分析说明时序报告符合电路工作预期,所以时序约束是正确的。但在实际时序收敛时还不能像一般芯片内部的数字电路那样简单地根据设定的时钟和 IO 约束进行时序收敛,理由如下。

图 3 是芯片内部一般数字电路的基本结构,它的时序关系如图 4 所示。

flop1/CP 在 edge 2 发送新的数据,flop2 会在 edge3 采样这笔数据,这是它们之间的建立时间(setup time)的检查。同样 flop1/CP 的 edge 4 也可能发送新的数据,这些数据不能被 flop2/CP 的 edge4 采样到,这个时序检查就是保持时间(hold time)的检查。基于这样工作模式和静态时序检查方法,EDA 工具能够比较容易根据时钟频率的要求和电路自身的快慢自动地满足上述电路的时序要求。例如当建立时间不满足时 EDA 工具可以通过缩短flop1/Q->flop2/D 路径的延迟或者利用 flop1/CP 和flop2/CP的skew 做到,但这些都不太适合 DDR Memory interface。因为图 2 中 i_rdata_r/f 的时钟是经过延迟线的,而这个延迟可能需要根据外接 Memory 的不同、工作频率的不同甚至工作电压及温度的不同进行调节以满足 i_rdata_r/i_rdata_f 数据端的建立保持时间的要求,这样才能够正确接收数据。因此在时序收敛过程中时无法按照确定的延迟线延迟进行时序收敛,如果固定延迟进行时序收敛有可能会导致延迟线可用工作范围变小。事实上,图 2 电路的时序收敛通常做法就是使 pd 到 i_rdata_r/f/D 的延迟和 dqs 到 i_rdata_r/CP 和 i_rdata_f/CP 的延迟尽量相等,这样才能保证将来做延迟线调节时有足够的调节范围,但这样做法可能导致在自动布局布线完成后 i_rdata_r或i_rdata_f 的数据端的建立/保持时间不是一直能够得到满足的,从而导致在后仿真时有可能遇到时序违例,造成后仿真失败,这种情况在 DDR Memory interface 是多 bit 时,由于不同 bit 之间的延迟偏差会更严重,给后仿真带来困难,因为仿真工程师需要找到一个合理的延迟线设置同时满足不同 bit 和上下沿的建立保持时间的要求。而且,它随着 DDR 速度的增加还会恶化。事实上基于前面的时序约束,通过脚本改变延长线的延迟设置然后做时序分析,可以很方便地利用静态时序工具获得后仿真时所需的延迟线的设置以满足所有 bits 及上下沿的时序要求。这样的方法也可以帮助我们分析读路径中实际可用的延迟线工作范围,从而指导时序收敛过程。如当自动布局布线工具 APR 时由于某种原因导致 dqs 到 i_rdata_r/CP 或 _rdata_f/CP 的延迟比 pd 到 i_rdata_r/D 或 i_rdata_f/D 的延迟偏大时,这会导致延迟线可调范围变小。设计者可以使用上述方法发现这样的问题。

通过静态时序工具可以得到上述方法的结果(表 1),它反映了随着延迟线的调整 i_rdata_r/f 的建立保持时间满足的情况,正值表示相应的时序是满足的,负值说明相应的时序是不满足的。可用的延迟线的设置是 i_rdata_r和i_rdata_f 的建立(setup)和保持(hold)时间都是正值。比较后得到 step=1~7 都是可以使用的延迟线设置,它们的中点大约为 step=4,这个值可以用来做 post-SDF 仿真。

因此上文中的 DDR Memory interface 的时序设置及后续时序检查方法可以很好地检查 DDR 读接口的时序满足情况并可以很方便地找到可用的后仿真设置,极大地提高了工作效率。

3 DDR Memory 写接口

类似 DDR Memory 读接口,JEDEC Spec 的 DDR Memory 写时序如图 5 所示。① tDQSH:Write DQS 高电平的宽度;② tDQSL:Write DQS 低电平的宽度;③ tDS:写数据的建立时间;④ tDH:写数据的保持时间。

写操作时内存控制器提供时钟和写数据且仅在有数据的时间段内驱动时钟(DQS),时钟和数据在内存的输入需要满足中间对齐(center alignment),这样内存端(Memory)就可以使用时钟(DQS)的上下沿采样数据。图 6 写电路工作时序如图 7 所示,i_wdata_r/f 的数据经过 MUX 选择后就会变成一个上下沿都翻转的数据,而 dqs 经过延迟线后可以和写数据达到中间对齐(center alignment), 从而满足 DDR Memory 对写数据的建立保持时间的要求。

根据图 5、图 6、图 7 写电路的时序约束可以添加图 7 中写数据和 DQS 间关系。对应在静态时序工具中可以得到时序报告。

综上,基于前述的 DDR Memory 写路径时序约束的静态时序报告和电路预期的工作模式是一致的,但和读电路类似,为了保证 write DQS 有足够的可调范围,写电路时序收敛时一般也只是尽量将数据和时钟的 path 做 balance, 而不能基于某个延迟线的设置或某个频率做简单地修 timing 的工作,并且 Memory不同工作频率下对于输入数据的建立保持时间的要求也不同,也不易按照一个固定的标准做时序收敛。这样有可能导致像读电路一样后仿真时需要调节写时钟延迟线的设置以满足写数据的建立/保持时间的要求。同样在多 Memory bit 的设计情况时这样工作也会随着频率的提高越来越不易,因此类似读操作时的做法,这项工作也可以通过脚本改变延迟线的设置,在静态时序工具里完成。

4 结语

本文介绍静态时序工具在 DDR Memory interface 的时序分析,以及其在后仿真中的应用。从实践角度弥补了 DDR Memory interface 时序收敛目标和后仿真目标之间的差异,可以在满足时序收敛目标的前提的情况下给设计者提供一种快速找到合适的后仿真设置的方法。

-

仿真

+关注

关注

50文章

4134浏览量

134139 -

时序

+关注

关注

5文章

392浏览量

37463

原文标题:静态时序工具在 DDR Memory 接口时序收敛和后仿真中的应用

文章出处:【微信号:appic-cn,微信公众号:集成电路应用杂志】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ADC的静态指标有专用的分析工具吗?

固定带宽与动态带宽的区别

ipc系统的网络带宽需求分析

海外静态IP:跨国业务与远程工作的重要工具

Perforce静态分析工具2024.2新增功能:Helix QAC全新CI/CD集成支持、Klocwork分析引擎改进和安全增强

利用静态检查工具完善功能安全中测试覆盖率

时序逻辑电路故障分析

IAR通过多架构认证的静态分析工具加速代码质量自动化

FPGA 高级设计:时序分析和收敛

AnyWay功率分析仪带宽是否越宽越好?

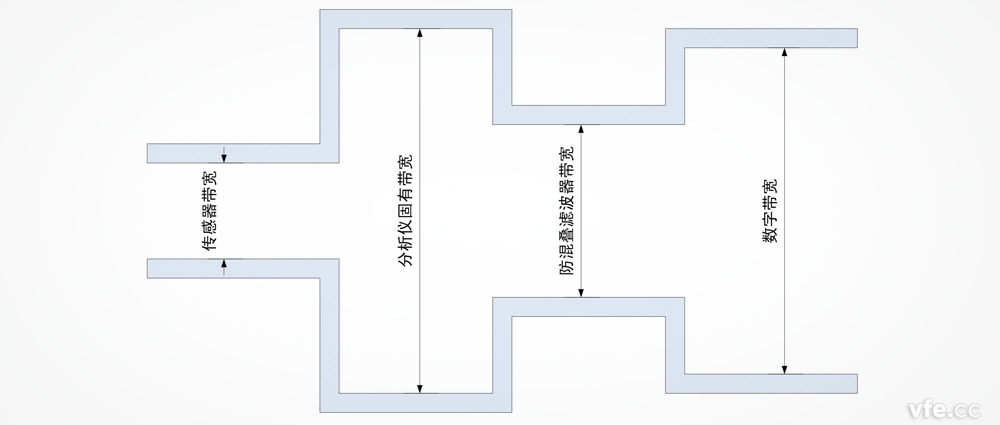

利用静态时序分析工具解决带宽不足问题

利用静态时序分析工具解决带宽不足问题

评论