光纤通道或异步传输模式(ATM)数据速率等新技术,如实时视频处理,医疗成像和电信,正在对当今CISCμP的功耗造成负担。 Windows NT的多用户多任务应用程序的预期增长将进一步加剧这一问题。随着处理需求的增加,似乎只有提供RISC性能数据的μP才能集中力量来满足这些任务。在过去几年中,已经有许多能够执行这些新技术任务的μP。

理解这些高性能μP中的所有特殊功能是一项艰巨的任务,然而。这些芯片提供了创新,以克服前几代产品中的缺点,因此包含x486 CISC式μP或更早版本中未提供的许多功能。超标量和超流水线架构是当今的口号。这些架构将μP性能方程扩展到极限。 μP执行任务的经典性能等式由下式给出:

执行时间=(无指令)×(循环/指令的平均数)×(循环时间)。

由于周期时间达到物理约束并且RISCμP平均有一个周期来执行指令,因此克服执行时间障碍的一种方法是并行执行多个指令。超标量μP具有指令调度器,其将未执行的指令馈送到可访问通用寄存器文件和片上高速缓存和总线的片上执行单元池。调度程序必须确定正在使用哪些寄存器,并选择非冲突指令以在每个时钟周期进行调度。从理论上讲,调度指令的数量没有限制,但是当前的技术水平是三个或更少。

Superpipeline架构通过在一个指令中执行一个以上的指令来实现性能提升时钟周期。任何指令的整体执行都是一个顺序过程,您可以分解为几个步骤。今天所有重型打击者都使用与步骤重叠的流水线架构,例如预取指令和数据的时间,指令解码时间,执行时间以及数据的写回时间。通过将CPU时钟周期分成子循环并在每个子循环中发出新指令来实现每个时钟周期执行多个指令步骤。虽然一些超标量体系结构也允许每个时钟周期执行多个指令步骤,但这些指令步骤通常不会像超流水线架构那样交错。

很多doodads

今天的所有高性能产品至少具有64位外部数据总线,片上浮点单元(FPU),一个或多个ALU,片上高速缓存,存储器管理单元(MMU)以及转换旁视缓冲区(TLB)将虚拟内存地址转换为物理内存地址。这些μP还具有存储缓冲区的优势,这使得流水线可以无延迟地继续执行,并最大限度地减少与使用外部缓存的数据填充片上缓存相关的延迟。硬件的设计考虑了软件程序员的风俗习惯。检测指令流中的条件或无条件分支语句的分支预测单元试图预测哪条指令和数据应放在管道中。准确的预测不会产生处理延迟,而不准确的预测可能会导致管道刷新。

此外,这些设备提供多处理功能,可实现总线仲裁,缓存一致性协议和总线侦听。这里提到的所有μP都运行Microsoft的Windows NT和其他流行的操作系统,例如Unix。为了与x86兼容计算机的流行软件的广泛基础保持二进制兼容,大多数μP依靠仿真技术的突破,让RISC计算机运行x86软件,其性能水平可与66-MHz Intel486DX2μP相媲美。

MIPS技术R4400是超流水线架构的一个很好的例子。 R4400于1992年10月推出,接受外部75 MHz时钟,并在内部将时钟乘以2,以驱动150 MHz 8级流水线,每个CPU周期执行两条指令。 R4400的三个版本包括具有片上高速缓存的版本,这些高速缓存不需要外部二级高速缓存(R4400PC和R4400-SC)用于成本敏感的应用,而高端版本(R4400MC)用于包含on的多处理系统-chip二级缓存控制器。片上指令和数据高速缓存各为16 KB,外部二级高速缓存有128位数据总线。

R4400是真正的64位架构,提供64位FPU,ALU,整数寄存器和系统总线的位数据路径。整数单元可以执行背靠背ALU或加载/存储操作,而不受调度程序的任何问题限制。该芯片可执行32位和64位应用程序。虚拟地址空间可以是32位或64位宽,48入口片上TLB转换为36位物理地址空间。芯片的字节排序数据格式可以配置为大端或小端。

您可以使用第三方芯片组将芯片的64位多路复用地址和数据主机总线连接到标准系统总线 - 派对供应商。 NEC和东芝制造的三个ARC-set ASIC将R4400主机总线转换为i386兼容系统总线,以便与标准PC外设芯片进行通信。 ASIC还提供到视频内存的64位数据路径和到主内存的128位数据路径。

64位架构可扩展

Alpha系列的第一个成员Digital Equipment Corp的21064μP是另一个真正的64位架构。该架构具有64位虚拟地址空间,片内寄存器,整数和浮点数均为64位宽。 32项TLB将64位虚拟地址转换为34位物理地址,单独的8 KB片上指令和数据高速缓存为7级整数流水线和10级浮点流水线提供数据。 Alpha的超标量和超流水线架构的第一个实现可以在每个时钟周期向四个独立的执行单元发出两条指令。数字声称Alpha架构可扩展,每个周期可实现10条指令。

21064接受单个ECL兼容时钟输入,内部除以2,运行速度为150或200 MHz。该芯片采用3.3V电源供电,但所有I/O端口均兼容TTL。虽然Alpha内部运行的CPU时钟速率是输入时钟频率的一半,但芯片进一步划分CPU时钟,以便在18.75和75 MHz之间的可选总线速度下与其外部128位主机总线通信。四个或六个ASIC芯片组充当Alpha主机总线和外围组件互连(PCI)总线之间的桥梁。芯片组还为8到256 MB的系统DRAM和系统逻辑提供错误检查和纠正(ECC),以控制外部辅助50-MHz缓存系统,Digital调用Bcache。

最新版本Alpha(21066)于1993年9月推出,它将ASIC芯片组集成到μP芯片上。因此,$ 385(5000)21066提供了与外部Bcache,DRAM内存和PCI总线的直接连接,无需外部系统逻辑。为了节省引脚数,21066将其存储器总线限制为64位。该芯片还通过集成片上PPL乘法器简化了设计,该乘法器可以将输入时钟乘以2和9之间,以生成其内部166 MHz时钟。此外,Alpha架构实现了一层软件,它位于用户的应用软件和系统硬件之间。机器码编写的软件称为PALcode(特权架构库代码),它实现了低级硬件支持功能,这些功能通常由操作系统(如VAX)中的微码提供。通过提供TLB未完成例程,上下文切换,中断确认和异常调度等功能,PALcode使Alpha的架构独立于操作系统。

越来越多的SPARCμP是由于SPARC International的开放标准政策。该联盟的200多名成员正在为SPARC International开放式规范设计μP或计算机系统。高性能版本8规范的一个μP实现是SuperSPARC,它由Sun Microsystems Computer Corp和Texas Instruments共同开发。 TI制造该器件。 32位超标量μP具有指令获取和发出逻辑,其为三个独立的ALU,FPU和单独的加载/存储单元预取和调度指令。每个时钟周期可以发出多达三条指令。检查三个指令的数据依赖性和资源冲突,以确定执行的执行次数。指令始终按顺序发出。

40,60或60 MHz SuperSPARC可与两个主机总线接口,2级Mbus或Vbus一起运行。您可以通过驱动其中一个μP引脚激活来选择主机总线。 40-MHz leve-2l Mbus是64位数据和36位地址多路复用同步总线。 SuperSPARC可以以比Mbus更高的时钟速率运行,与Mbus时序要求异步运行。 Mbus支持少量多处理器的MESI协议,并使用兼容TTL的电压电平与标准CMOS器件兼容。

为了实现更高性能,Vbus支持TI外部高速缓存控制器,并且2 MB外部缓存SRAM。高速缓存控制器与主机侧的高速缓存SRAM和Vbus以及系统侧的Mbus或Xbus连接。 Xbus最多支持四个外部总线观察器,可与多个系统总线一起使用以增加可用带宽。 Cray Research在其最近发布的S-MP超级服务器系统上修改了Xbus以支持多达64个SPARCμP。

SuperSPARC架构使用Wabi(Windows应用程序二进制接口)在Unix平台上运行Windows 3.1软件的PC应用程序。 Wabi由Sun Microsystems子公司Sun Select开发。模拟器将x86指令转换为相关的RISC指令,执行它们,并向Windows应用程序返回适当的值。

赛普拉斯Ross Technology子公司的HyperSPARC是版本8开放标准的另一个实现性能SPARCμPs。 HyperSPARC是使用磁带自动绑定(TAB)在Mbus模块上实现的芯片组。每个模块包含一个或两个CY7C620 CPU:CY7C625高速缓存控制器,MMU和标签单元;和两个或四个CY7C627缓存数据单元,分别用于128或256千字节的二级缓存。 55或66 MHz超标量CPU具有四个执行单元,每个时钟周期读取两条指令,如果没有数据依赖性,可以单独执行。与SuperSPARC一样,HyperSPARC架构与现有SPARC软件100%二进制兼容,但提供比上一代SPARCμP更高的性能。

PowerPC 601是RISCμP系列中的第一个Apple,IBM和摩托罗拉计划开发。第一个实现是32位超标量μP,每个时钟周期可以发出多达三条指令,三条独立执行流水线中的每一条都有一条指令。 8阶段指令队列预取来自32k字节统一高速缓存的指令,并且可以向执行单元发出无序指令以提高性能。指令队列的低四个阶段试图始终保持管道填充,而队列的上半部分就像一个指令缓冲区。

当指令队列中的较低阶段遇到分支指令时,分支处理单元(BPU)将指令拉出队列以解决它。单元上方的指令在队列中向下移动以取代被移除的分支 - 一种称为分支折叠的技术。分支折叠可以将流量控制开销减少到零,因为执行过程就好像分支从不存在一样。 BPU可以在一个时钟周期内解码和执行分支指令。如果采用分支,则BPU从缓存中的新目标地址请求指令,该指令在气泡发生之前填充指令队列。

PowerPC 601实现静态分支预测,其中编译器给出提示关于是否应该采取分支。指令操作码中的单个位提供提示。编译器总是预测后向分支,例如在程序循环中使用的分支,而不是前向分支。当分支指令遇到数据依赖性时,BPU等待分支条件代码变得可用。同时,μP不是停止指令队列,而是获取预期分支的指令。如果预测正确,则程序流程继续。否则必须刷新指令队列。

PowerPC 601使用基于Motorola的MC88110RISCμP同步总线的外部主机总线 - 尽管它不兼容插件。该总线具有64位数据和32位地址路径,并具有用于多处理功能的总线仲裁和高速缓存一致性功能。目前,如果要将PowerPC 601设计到系统中,则必须将其与μP的MC88110总线连接。摩托罗拉正在与第三方芯片组供应商谈判开发芯片组,这些芯片组将充当MC88110主机总线和PCI总线之间的桥梁。

从技术上讲,PentiumμP不是RISC处理器,因为它实现了现在标准的复杂x86指令集。然而,32位PentiumμP在66 MHz工作时达到了基准数据,远高于第一代CISCμP。原因是Pentium借用了RISC架构中使用的许多思想。超标量Pentium包含三个管道执行单元,两个整数和一个浮点。 μP可以在一个时钟周期内发出两个整数指令或一个浮点指令。

Pentium的8 KB数据和指令缓存是用于共享存储器多处理器系统的回写缓存。数据高速缓存支持MESI(修改的,独占的,共享的,无效的)协议,该协议通过总线监听来维护高速缓存一致性。此外,Pentium使用动态分支预测方案来猜测分支语句将采用哪种方式。分支目标缓冲区会记住每个分支的目标地址和每个分支的方向,并根据分支的历史记录动态预测未来的分支。动态预测方案比PowerPC 601中的静态预测方案需要更少的编译器支持。

英特尔提供82430 PCI芯片组来开发用于PentiumμP的台式PC。芯片组由82434LX高速缓存和主存储器控制器以及82433LX本地总线加速器组成,该加速器管理主机总线和PCI总线之间的协议。 PCI总线允许多个总线主控器与Pentium CPU传输同时传输数据。该芯片组支持多达512千字节的外部二级缓存SRAM。然而,66 MHz系统中组件之间的时钟偏差要求非常严格。

所有这些高速时钟和数据线都在抖动,获得高性能的μP以便在印刷电路板上有效运行有时可能是一件苦差事。 MicroModule Systems提供了一种在多芯片模块(MCM)上放置高速设计关键区域的模具的方法。该公司拥有自己的洁净室设施,致力于为MCM上的多个裸片制造受控阻抗布局。 MCM近年来名声不好,因为低产量已经产生了过高成本的设备。然而,MicroModule Systems董事长Bill Robinette Jr认为,经过全面测试的“已知良好”芯片和用于Mentor Graphics开发的MCM的CAD程序可以将开发受控阻抗MCM的增值成本保持在最低水平。 。

-

CISC

+关注

关注

1文章

31浏览量

20105 -

PCB打样

+关注

关注

17文章

2982浏览量

23683 -

华强PCB

+关注

关注

8文章

1831浏览量

29333 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44715

发布评论请先 登录

单片机的一些特殊功能寄存器

电源管理特殊功能寄存器PCON介绍

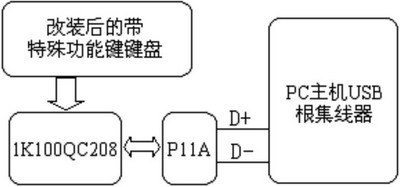

USB键盘特殊功能键的实现

第二章(1) 初识P0,P1并口 数据类型,常量定义方法,特殊功能寄存器定义

高性能μP中的特殊功能介绍

高性能μP中的特殊功能介绍

评论