产量对设计余量的依赖性如图1所示。低于一定水平,产量注定为0,因为发生的物理现象,可能只有在设计阶段之后变得明显,在现实生活中,设备会损害大部分路径。增加裕量将使设计对这些现象更加稳健,但也会增加设计成本,在芯片的面积和功耗方面,以及完成设计所需的设计工作。超过一定水平,设计根本不可能。

设计规模。深亚微米技术的巨大芯片意味着存在大量实例和大量时序路径关闭。这反过来导致在收益率曲线的下降拐点之上定义设计余量(见图1),以便获得可接受的产量损失,保持非常接近当前技术和设计复杂性可实现的最佳效果。此外,不需要接近设计成本开始快速增加的区域,以避免在设计时间,面积和功耗方面对性能的任何危害。

从数学角度讲,设计师应尽量减少Yield/ProductCost的功能。

图1:优化设计余量

由于这些原因,设计余量必须捕获设计中总体时序路径的正确统计数据。更准确地说,它们不应该被缝合到最坏的情况路径(导致设计成本太高),也不应该被更宽容的(导致设计不够健壮)。它们应该捕获大多数路径,同时排除最特殊的情况。应该清楚的是,图1中的曲线曲线(以及最佳设计余量)取决于设计风格和设计选项/选择。因此,当面对一项全新的技术时,应该尽快在流程中引入任何可能直接影响利润的改进,因为,正如所看到的,即使早期定义的利润率,如果被高估,也会注入损失。性能。而这些损伤很难在以后删除或由于过度设计而导致资源浪费。

系统的复杂性。系统复杂性通常在分层实例的数量,层次级别,时钟组的数量,模式的数量等方面增加。这提出了在每个层次级别交叉处定义时序余量以在最大性能的每个设计阶段保持一致性的挑战,同时避免在某个阶段陷入困境的问题,因为在前几个阶段低估了一些余量。此外,出于同样的原因,必须从设计的最开始插入来自更高级别或不同级别的层级的效果的适当估计。

工作环境。在复杂的芯片设计中,每项任务所需的高水平专业化倾向于使工作流程设计和分割,因为每个人都面临艰巨的任务,充满技术障碍,并且可能忘记与其他人保持沟通。球队。为了补偿并使设计过程有利可图和可预测,整个设计组织必须标准化设计余量并使用先进的工具和方法。计算,传播和验证这些设计余量的工具的中心分布也是必要的。

要避免的经常陷阱是设计团队(可能是第三方)使用不同的边距在块开发上单独工作,导致当宏被插入顶层以进行最终时序检查时出现时序违规。因此,需要为多个修复程序打开相同宏的设计,这可能会耗费大量时间和精力。

任何可能的设计定制都可以减少不确定性,只要它可以嵌入到设计社区采用的现有流程和工具集中。

现在我们将讨论所有设计周期中时序余量的定义,使用和管理。为简单起见,我们不会处理错误路径的正交问题。

-

SoC设计

+关注

关注

1文章

148浏览量

18774 -

PCB打样

+关注

关注

17文章

2968浏览量

21704 -

华强PCB

+关注

关注

8文章

1831浏览量

27759 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43041

发布评论请先 登录

相关推荐

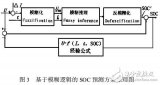

SoC设计中的功耗管理问题

SoC系统级芯片

NEC MCU在马达方面的应用

电动汽车的电池SOC管理

Xilinx Zynq SOC的动态电源管理功能的展示

SOC电源管理系统

什么是SOC?SOC做什么?

如何解决高校宿舍用电浪费及管理方面的问题?

SoC设计余量的定义和管理方面的问题

SoC设计余量的定义和管理方面的问题

评论