与几年前相比,这些SoC中的模拟/混合信号(AMS)内容和交互要多得多。为了避免错误和重新旋转,有必要实现模拟IP和子系统的良好参数覆盖,以便不会遗漏角落情况。

因此,精心制作的预硅片AMS验证混合信号SoC中的模拟子系统是必需的,但是这种模拟可以非常长时间运行,即使在没有完整SoC的情况下也是如此。基于命令行的SoC AMS仿真(其中设计采用RTL和SPICE)是普遍的。随着SoC中模拟和混合信号组件的集成度和复杂性的增加,在实际的时间限制内实现这种详尽的仿真和越来越多的验证测试用例变得越来越不可行。

当前方法

当前方法如图1所示:

图。 1传统方法

是的,有一种回归技术。但所有这些都是目前的手工努力。事实上,我们可以说它们容易出现人为错误。此外,还有许多工具可用于最终生成可分析的图形输出。这种方法(见上面的图1)非常繁琐,既不是用户友好的,也是手动干预使其很容易出错。这通常会限制验证范围。

同样在当前的方法中,后期运行数据分析必须通过不同的图形绘制和后分析工具分别处理,这使得它成为一项繁琐的任务。

建议的方法论

为了克服所有这些困难,肯定需要自动回归以及一些可以接受参数化的技术输入然后自动触发并行设置。一个这样的电源启用工具是Cadence的ADE-XL。

自动回归- 我们遵循的自动回归方法基于以下几点:

在Cadence的Virtuoso中定义参数化混合信号测试平台。

使用ADE-XL使用单个按钮在指定的参数范围内启动回归:Go!

模拟后综合结果分析

利用ADE-XL ViVA的内部功能及其与自定义脚本的兼容性来分析结果摘要,只产生图形输出。这使它成为单点解决方案。

目前,业界部署了Cadence的ADE-XL的参数化和扫描功能,以便彻底地运行不同的角落。我们提出了一个新颖的想法(见图2),从AMS验证角度灌输ADE-XL的类似技能。

结果

ADC子系统是混合信号SoC中非常重要的部分,因此需要在AMS环境中进行广泛的验证。从需要验证的时间和详尽性的角度来看,这是一个问题。线性检查和噪声灵敏度是两个这样的关注领域。

我们深入研究这两个例子来看看&感觉上述方法。

通过ADE-XL的ADC噪声灵敏度

如图3所示,噪声灵敏度验证方法的第一阶段是从A-IP的每个端口获得部分噪声传递函数(p-NTF)到功能输出。这是通过在功能操作模式下执行A-IP的瞬态分析,同时在不同频率下在一个输入端口上注入噪声来完成的。输入噪声频率范围应涵盖整个可能的噪声源。在SAR-ADC的情况下,输出频谱限制在奈奎斯特频率FN(Fs/2,其中Fs是采样率)的采样系统中,选择输入噪声频率,使得在折回时,它们代表不同的谱线在0Hz到FN的范围内。为确保小信号假设有效,噪声幅度应保持足够低,使得与A-IP操作的大信号偏置点相比,总噪声包络看起来很小。对于具有K端口的A-IP(包括一个功能输出端口),需要K-1瞬态分析来获得所有p-NTF。

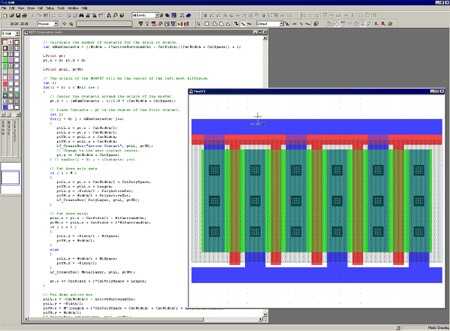

图3获得A-IP的p-NTF(左);图4(a)参数化设置可视化(右)

如图4(b& c)所示,我们创建了一个完全参数化的设置,其中输入作为端口和要扫描的频率,可以通过ADE -XL单击按钮来触发。在这里,我们提供一个自定义参数来扫描频率和端口,然后设置运行一个详尽的排列运行所有模拟。下面的图5显示了灵敏度的最终结果。

图。 4(b)ADE-XL噪声灵敏度参数化方法的实现

图。 4(c)ADE-XL的运行窗口显示并行运行。

图。 5通过并行回归技术获得的不同端口的噪声灵敏度结果

使用ADE-XL进行ADC线性检查

ADC线性度意味着计算INL (积分非线性)/DNL(差分非线性)ADC。通常要有16个命中/代码和12位ADC,理想情况下我们需要4096 * 16 = 65536 us的斜坡时间来实现结果(假设总转换时间为1μs)。这将导致大量仿真时间,因为平均而言,28nm ADC SoC仿真需要大约48小时才能运行1000μs。因此,此设置大约需要1个月的运行时间。

图6通过ADE-XL进行线性检查的参数化TB。突出显示的部分表示参数化。

图7运行窗口显示广义参数和并行运行的矢量值被触发。

如图6所示,我们通过提供所需命中数和需要运行的并行运行数来参数化通用测试平台。一个合理的模拟时间。然后,ADE-XL自动生成具有不同起始和终止斜坡点的所有并行设置(如图7所示)。这使得设置更加节省时间并且更加普遍。

结论

文章讨论了一些困难混合信号验证工程师面对AMS验证,以及如何通过Cadence的ADE-XL&它的创新融合,我们提出了一个实用的解决方案。我们通过这种新的定制方法,进行混合信号验证的一体化单点自动回归验证解决方案。这种方法为自动化指定了大量工作,并且有助于在没有太多用户参与的情况下对新设计进行新的回归/详尽测试。此外,由于其总结的结论表和内置的图绘制功能,推断数据也变得容易。使用这些工具和我们提出的方法有助于我们实现四倍的生产率提升,并缩短设置验证台所需的手动时间。

-

soc

+关注

关注

38文章

4297浏览量

220977 -

PCB打样

+关注

关注

17文章

2971浏览量

22218 -

华强PCB

+关注

关注

8文章

1831浏览量

28335 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43620

发布评论请先 登录

相关推荐

一种基于混合信号技术的汽车电子单芯片设计

混合SOC验证的挑战与方法介绍

混合信号 SOC 产品用户指南

DFT和BIST在SoC设计中的应用

混合信号SoC助力模拟IP发展

混合信号示波器解决方案

Actel的SmartFusion混合信号FPGA开发评估方

混合信号SoC在应用中的设计开发和使用正在增加

混合信号SoC在应用中的设计开发和使用正在增加

评论