电力传输网络(PDN)是SOC中最重要的组件之一,因为它为设计中的所有组件供电。随着设计复杂性的增加,分区方法越来越受欢迎,而功率门控有助于降低不断增长的功耗。通过这些方法,设计变得更加高效,但是它们在PDN的设计方面引入了额外的问题和挑战。

电网设计

使用的金属在电网中,主要取决于设计的功率要求和技术节点中使用的金属选项。更多的金属选择成本更高,但它创造了比较少金属选项设计更强大的设计。电网中的金属用量(宽度,间距和金属堆叠)由电力需求定义。如果我们有更多的功率要求,那么在这种情况下我们必须使用更宽的金属条纹用于网格。

应选择金属宽度,以免浪费路由轨道。有时,DRC规则也在决定电网金属宽度方面发挥作用。让我们看一下下面给出的DRC间距样本表。

DRC间距规则取决于金属宽度和宽度。也是在金属的平行运行长度上。间隔表下方显示间距如何随所用金属宽度而变化。如果我们采用W4μm的M4功率条宽度,则在这种情况下,与下一个宽度为w1μm的M4信号路径(M4的最小金属宽度)的间隔必须为“s3”。选择M4宽度“w2”来照顾宽金属规则,这样我们就不会浪费附近的布线轨道。我们假设特定技术节点的路由网格为“x”μm,这可能因技术而异。

电网设计和模拟集成的挑战

1。分区设计中的电源门控

对设计进行分区有助于将设计分解为更小的层次结构,这些层次结构可以单独以更有效的方式处理。此外,对这些模块中的一些进行电源门控可以显着降低设计的总功率。但是对模块进行电源控制会导致电网连续性中断。因此,电源门控分区的最大缺点之一是核心网格面临的IR丢弃问题。本讨论专门针对基于引线键合的封装(QFP,QFN,BGA等)。

我们可以最大限度地减少跌落的方法之一是使网格更强大。这需要定量地完成,因为它有自己的拥塞限制和模具面积的显着增加。

第二种方法可以是通过电源门控模块为核心电源提供馈通路径,以便核心网格保持连续。

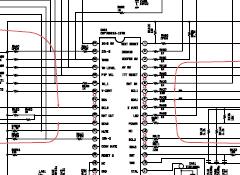

图1:电源门控分区设计中的传统电网

图2:引入馈通路径分区以维持核心网格连续性

2。分区和顶部之间的网格对齐(非功率门控分区)

分区和网格之间的核心网格对齐可能是一个棘手的迭代业务,特别是当大量的块是参与其中。对于所有块和顶部,始终建议对于金属条纹具有共同的设定距离,宽度和间距。如果遵循这一点,则最终可以以几微米的移动为代价来实现对准,同时将块放置在芯片顶部上。

芯片顶部和块级之间通常存在金属共享。在这些情况下的对齐可以通过复制块LEF中的块内的网格来实现,使得顶部的网格可以在这里和那里以几微米的移动容易地连接到这些块销。从一开始就始终建议在这方面采取干净的方法。

图3:顶部反映的块电源引脚。

图4:顶部电网连接到块电源引脚

3。电源门控设计

低功耗模式是一种在不使用时通过关闭逻辑某些部分的电源来降低芯片总功耗的功能。电源开关通常用于为电源门控模块提供电源。即使使用电源开关增加了集成的额外复杂性,包括芯片面积的影响,但在设计性能方面,它们是最好的。

与电源开关相关的一个问题是它的位置方面电源和电源门控模块。我们将在下面讨论设计中使用电源开关的一些例子。

CASE1:当通过控制芯片内部的电源开关来完成电源门控时。板载源始终为ON。

图5:源镇流器始终开启时使用电源开关

在上面的图5中,我们已经示出了如何在A点使用电源开关对可切换P1域进行电源门控。因此,A点的电压控制整个芯片的电压降。因此,开关A需要尽可能靠近电源放置。需要通过保持垫和点A之间的下降尽可能忽略来在A点建立整个网格。然而,这种方法容易在开关上产生电压降,因此需要根据电流要求,开关提供的电阻和所用开关的大小来使用合适的开关。

CASE2:当通过关闭电路板电平来完成电源门控时。

图6:使用电源开关镇流器用于电源门控

在上图中,电路板上的镇流器被关闭以供电门电源域P1。低功率域P2(始终为开)连接到非常靠近电源板的电源开关,以创建并联电网。

案例3:仅使用内部镇流器时

图7:仅为内部镇流器使用电源开关

开关尽可能靠近内部稳压器,以便为可切换电源供电域P1。

4。记忆方向

这是一种极为罕见的情况,与影响IR掉落和芯片功能的内存方向有关,但如果不加以处理,则可能非常关键。

我们在NPI中的记忆常常有不同的方向,在给定技术中,取决于存储器的允许取向,在水平和垂直方向上具有存储器电源引脚。

当从顶部金属掉到存储器引脚时,“addStripe”命令仅通过正交存储器引脚丢弃。因此,当顶部金属栅极和存储器引脚在同一方向时,没有过孔添加到存储器引脚。如果没有捕获,这可能会非常危险。

图8:存储器电源引脚与电网正交

图9:与电网方向相同的存储器电源引脚

-

PCB打样

+关注

关注

17文章

2968浏览量

21651 -

华强PCB

+关注

关注

8文章

1831浏览量

27719 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

42978

发布评论请先 登录

相关推荐

【送书福利】不懂PDN谈何电源完整性?请收下这本PDN设计指导硬核书

PDN 电源分配网络设计步骤 PDN layout步骤

PDN设计的目的

Altium Designer PDN Analyze简介

NEC FS2186PDN chassis彩电电路图

PCB制造:PDN设计指南

PDN设计

利用Altium Designer自带PDN Analyzer对电源平面进行PDN实例仿真分析,超经典!

PDN 元件对阻抗的影响

震旦ad330pdn

震旦ad330pdn

评论