要管理随机故障,首先需要了解产品故障模式并估算故障率。这涉及根据适当的功能安全标准有效地进行危害分析和风险评估。开发人员必须确定适合其系统的安全功能和风险降低级别(SIL/ASIL)。然后,基于SIL/ASIL级别,开发人员需要定义相应的架构有效性集和随机硬件故障度量。还需要有适当的安全机制,也称为诊断,直到每个安全功能达到所需指标所衡量的风险降低为止。

让我们更详细地研究以下内容:

故障模式和故障率

功能安全架构指标和随机硬件故障率指标

降低故障率的安全机制

故障模式和故障率

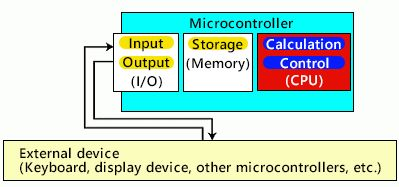

作为代表性案例,请考虑现代汽车和工业产品通常具有电子可编程系统控制它们。这些系统通常称为电子控制单元(ECU),它们由MCU和输入/输出电路组成。因此,了解半导体和MCU故障模式及其故障率将有助于估计产品故障率。

影响MCU的主要故障模式有三种:

永久性封装失效,例如封装与印刷电路板(PCB)之间的热膨胀引起的封装磨损

永久性硅片失效,如开放的金属线,金属短路,晶体管结泄漏,逻辑门固定故障以及由于操作磨损引起的其他问题

瞬态硅故障,例如辐射引起的SRAM位翻转

半导体故障率通常报告为时间失效(FIT),其中一个FIT是1E9或10亿个工作小时中的一个故障,或平均故障间隔时间(MTBF),其中MTBF = 1/FIT。

IEC/TR 62380提供了一种数学模型,可根据使用条件估算永久性包装失效率。该模型还允许基于元件的复杂性和诸如温度和电源开/关小时等的使用条件来估计硅永久FIT率。

此外,大多数半导体供应商发布其产品的IC组件永久硅故障率,作为FIT或MTBF中的可靠性数据提供。这些数据是使用有限数量的样本从高温操作寿命可靠性研究中计算出来的。

没有行业标准化的瞬态故障率估算方法。理想情况下,用于进行估算的数据应来自使用适当工艺技术的测试芯片的实际实验。例如,为Hercules TMS570和RM MCU提供的德州仪器硅瞬态故障率基于从洛斯阿拉莫斯国家实验室的过程测试芯片收集的数据,并使用JEDEC JESD89A测试标准。由于MCU的硅瞬态故障率可能比硅永久性故障率高一到三个数量级,具体取决于配置,强大的数据有助于最大限度地降低低估整体故障率的风险。

需求了解故障模式和速率意味着要求其产品符合功能安全标准的系统开发人员应该寻找具有相应支持文档的MCU。这包括描述安全概念的安全手册,随机故障管理的安全架构,假设列表以及MCU模块内置的安全机制列表。根据系统使用条件定制永久封装故障,硅永久性故障和硅瞬态故障的MCU随机故障率估算工具也很有帮助

功能安全架构指标和随机硬件故障率指标

系统和子系统开发人员进行危害分析和风险评估,以评估功能安全终端产品系统应用所需的风险降低水平。评估结果是一个安全目标,例如IEC 61508中描述的安全完整性等级(SIL)1至4的分类或ISO 262626中的汽车安全完整性等级(ASIL)A至D.(注:适用于半导体元件,可达到的最高SIL等级为SIL 3; SIL 4仅适用于系统本身,而不适用于进入系统的元件。)

标准定义了评估建筑安全覆盖范围的指标减少各种类型故障风险和发生故障概率的机制,然后使用这些指标来衡量安全目标的实现程度。 SPFM(单点故障度量),LFM(潜在故障度量)和SFF(安全故障分数)是显示故障率降低的架构有效性的比率度量。 PMHF(随机硬件故障的概率度量)和PFH(每小时故障概率)是显示总体风险降低水平的概率度量。

这些指标的应用示例如下所示。表1显示了单点故障度量(SPFM),潜在故障度量(LFM)和随机硬件故障(PMHF)的概率度量的ASIL要求。

表2显示了硬件容错(HFT)= 0时SFF的IEC 61508 SIL(B类)要求(即单个故障将导致系统停止运行)和每小时失败概率(PFH)。

降低故障率的安全机制

根据MCU故障模式和估计的故障率以及SIL或ASIL风险降低要求,最终产品系统和子系统开发人员必须遵循各种程序,以确保已达到功能安全随机故障率指标的目标。他们必须应用适当的安全机制来帮助检测各种故障,并在检测到故障时对故障做出反应。为确定故障模式,故障率和诊断范围,他们使用故障模式影响和诊断分析(FMEDA)方法。

安全关键功能需要在应用期间实时监控MCU操作。开发人员应设置系统,以便在检测到故障时,系统可以修复故障或MCU进入“安全状态”。在任何一种情况下,系统都会最大限度地降低人身伤害和/或健康损害的潜在风险。人员。

以下是一些诊断示例。图2显示了纠错电路(ECC)。单错误纠正,双错误检测(SECDED)ECC电路可以允许在运行时校正单个SRAM位翻转并检测双位翻转。

下面的图3显示了一个锁步CPU。运行相同程序代码和输出比较的Lockstep CPU可以检测到CPU故障。

MCU由许多模块组成,如CPU,SRAM,Flash,电源,时钟,ADC,定时器,SPI,CAN等。对于TI的Hercules TMS570等针对功能安全的MCU,MCU供应商的安全手册中提供了按模块列出的安全机制。

系统和子系统开发人员需要计算每个定义的允许故障率安全功能。每个安全功能可以使用不同的MCU资源,这就是为什么最好根据MCU资源的使用方式来计算故障率。有能力选择或取消选择故障率计算的安全机制是有帮助的。每个MCU模块显示诊断覆盖率(DC)和故障率指标的能力也很有帮助。

一旦计算出每个安全功能的MCU故障率,开发人员就可以使用这些数字来估算产品级故障率。

为了帮助开发人员,MCU可以预先通过IEC 61508和ISO 26262认证并且通常附带文档,数据和FMEDA工具。这种支持可以帮助最终产品系统开发人员了解安全架构,安全机制和假设,并估计随机硬件故障率。例如,TI的Hercules TMS570和RM MCU经过独立第三方认证,符合IEC 61508要求,最高可达SIL3(MCU可达到的最高SIL等级),满足ISO 26262要求,符合ASIL D.这些MCU的安全文档包括可用于一般下载的安全手册(无需NDA)和带有FMEDA工具的安全分析报告(根据NDA)。

-

微控制器

+关注

关注

48文章

7542浏览量

151320 -

PCB打样

+关注

关注

17文章

2968浏览量

21696 -

华强PCB

+关注

关注

8文章

1831浏览量

27749 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43035

发布评论请先 登录

相关推荐

微控制器监控器集成电路中的故障保护分析

AT32微控制器硬件设计指南及抗EMC设计要点

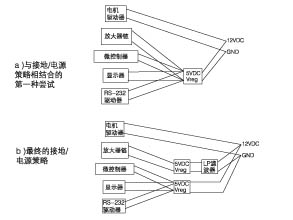

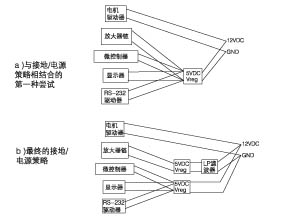

微控制器/模拟应用中电源、接地和噪声的管理

AT73C224 四信道功率管理单元,面向32位微控制器

微控制器/模拟应用中电源、接地和噪声的管理

微控制器省电管理方法

如何对微控制器进行省电管理

微控制器到底是什么?微控制器有怎么样的应用

什么是微控制器?如何编程微控制器?

将电源管理与高速微控制器结合使用

微控制器的随机故障的管理

微控制器的随机故障的管理

评论