设计人员总是在寻找减少不需要的功耗组件的方法,无论是通过以低功耗技术的方式设计设计,还是采用可以降低功耗的工艺。但是,其中一些解决方案的代价是性能,可靠性,芯片面积或其中的几个。最终,人们必须在功率,性能和成本之间达成妥协。下面的文章旨在讨论其中的一些技巧。这些技术分为建筑技术和基于过程的技术。

架构功耗降低技术:在RTL级别,可以采取几个步骤来降低器件的总功耗。通常,基于RTL的技术最小化设备的动态功耗,然而,使用诸如功率门控之类的技术,还可以降低芯片的一部分的泄漏功率。各种常用的技术有:

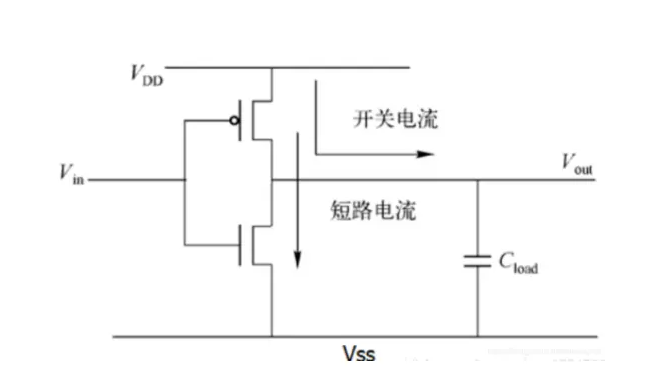

1.1。时钟门控:这种技术是一种非常流行的动态功耗降低技术。动态功耗是瞬态功耗(P 瞬态)和容性负载功率(P cap )消耗的总和。 P transient 表示当设备改变逻辑状态时消耗的功率量,即“0”比特到“1”比特,反之亦然。顾名思义,电容负载功耗代表用于为负载电容充电的功率。总动态功率如下:

P dynamic = P cap + P transient =(C L + C)V dd 2 f N 3

其中C L 是负载电容,C是芯片的内部电容,f是工作频率,N是切换的位数。由于动态功耗与MOS单元的切换直接相关,因此在不需要时选通时钟有助于降低动态电流。这种技术有助于保持设计状态,同时仅限制瞬态电流。设计人员经常使用AND/NOR门来为时钟门控,但是,基于锁存器的时钟门控是最受青睐的技术,因为它还可以节省设计的危险,否则会带来额外的功耗,这是动态功耗所固有的。

1.2。可变频率/频率岛:在大芯片中,并非所有模块都需要以尽可能高的频率进行时钟控制,以达到所需的性能水平。可能存在很少的块本身工作缓慢(例如,慢速通信块,如I 2 C,UART等),因此,可以以比核心/处理器之类的块更慢的时钟计时。高频时钟,实现最大吞吐量。因此,通过向不同的块提供不同的频率时钟,可以减少局部动态消耗。

图1:频率岛

1.3。电源门控:可能存在某些低功耗模式下可能不需要芯片某些模块运行的应用如睡眠,深度睡眠,待机模式等,只需要设备的一部分即可运行。在这种情况下,关闭非功能块是有意义的,这样设备就不必为未使用的块供电。这不仅有助于降低动态消耗,而且还为这种电源门控块节省了泄漏功率。然而,在处理这种技术时,设计必须确保来自电源门控模块的信号在低功率工作时不会影响功能模块。为此,隔离块放置在路径中,这样就不会发生功能损坏,如图2所示。请注意,从always-ON域到其他电源域的信号不需要隔离信号。因为他们永远不应该是非确定性的。

图2:电源门控

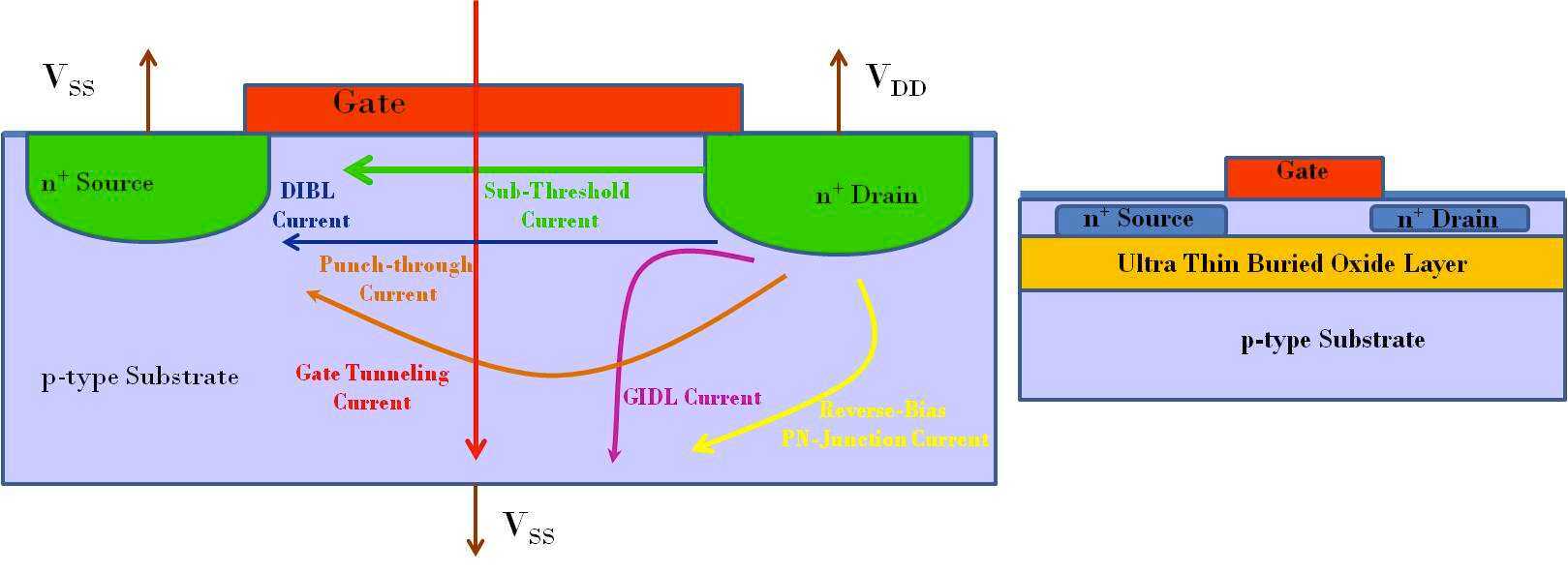

基于过程的电源减少技术:有很多功耗组件并不是所有组件都可以单独使用建筑技术。使用基于工艺的技术可以最有效地控制由于漏极引起的势垒降低,栅极引发的漏极泄漏,亚阈值泄漏等影响而导致的功耗。以下是一些最常用的基于过程的技术:

2.1多阈值电压CMOS单元:许多MOS特性受阈值电压的控制。细胞。亚阈值电流是栅极电压低于阈值电压时源极和漏极之间的电流。该电流近似值的数学表达式为:

可以看出,当阈值电压V T 增加了。因此,可以放置更高的V T 细胞以减少该组分。然而,正如我们在上面的传播延迟中所看到的,增加V T 对操作频率具有负面影响。因此,设计人员必须采用一种策略来混合较低的V T 和较高的V T 单元,以减少漏电流,同时保持所需的工作频率。为了实现这种策略,高V T 单元被用作休眠晶体管,当块应该处于待机模式时,它将电源选通到更低的V T 设计。当器件处于工作模式时,这些睡眠晶体管导通,此睡眠晶体管下游的低V T 模块可以获得电源并照常工作。这有助于减少待机模式下的电流。或者,根据时序关键路径与非时序关键路径对各种数据路径进行分类。定时关键路径可以使用较低V T 的单元(称为LVT(较低V T )单元)来实现,以便可以在更短的时间内实现相同的操作与用高V T 细胞(也简称为HVT细胞)实施的路径相比。即使芯片处于运行模式,这种混合使用方法也可以平衡漏电流。

另一种解决方案是根据应用程序要求动态更改单元格的V T 。这可以通过使用控制电路改变阱/体偏置电压来实现。这需要更复杂的MOS制造,因为它需要双阱或三阱制造技术。这通常称为可变阈值CMOS(VTCMOS)。然而,应该注意的是,降低V T 也会影响芯片的可靠性,因为即使更低的电压摆幅也会导致逻辑以错误的方式开始工作。这些电压摆动可能由于各种过程或环境变化而产生。因此,在降低细胞的V T 时必须非常谨慎,以免损害最终应用的神圣性。

2.2Mutli V DD 技术:从上面的等式可以看出,器件电压V DD <之间存在二次关系/sub>和动态功耗。因此,可以通过降低电源电压来显着降低动态电压。然而,电压降低也有其缺点。细胞的传播延迟如下:

从上面的等式可以看出,V DD 的减少增加了细胞的延迟。结果,当降低电源电压时,电池的工作频率降低。因此,必须在电压供应和相关性能之间保持平衡。

图3:电压岛 - 多V DD 操作

该挑战的解决方案可以是在设计中创建电压岛,其中可以使用较低电源电压为低性能慢速外设供电,并且可以使用更高电压为性能关键模块供电。但是,设计必须确保将适当的电压电平转换器放置在那些通过电压域通信的信号上。

该技术还可以降低器件中的栅极感应漏极泄漏效应和相关的功耗。

2.3动态电压和频率调节:电压岛技术,也称为静态电压调节,在操作器件时几乎没有限制。该技术不适应应用需求,并且一旦设计就不能改变对块的电压供应。然而,动态电压调节技术使设计者和客户摆脱了这些限制。该技术利用调节器,该调节器可被编程以根据需要提供电压电平。因此,各种块可以获得可配置的电压,并且客户/用户可以根据应用设置改变电压设置。这有助于动态节省电力。还使用了各种解决方案,其中设计释放了软件以改变电压缩放。设计本身可以检测器件中的电流负载要求,并相应地进行电压调整。该技术以更自适应的方式帮助降低功耗。

相同的电压调整也可以通过动态频率调整进行调整,其中可以根据需要通过软件更改块的频率。因此,在较低的V DD 上运行的块可以由较慢的时钟计时,同时保持性能和功能要求。该技术有助于降低器件的动态功耗和漏电功耗。

图4:差分电压和频率调节

2.4绝缘体上完全耗尽的硅(FDSOI):这是另一种有助于减少泄漏电流的各种成分的技术较低技术节点的威胁。使用这种技术可以非常有效地控制漏电元件,如GIDL,反向偏置电流和栅极隧道电流。在这种技术中,MOS位于超薄氧化膜上,使细胞与身体其他部分隔离。在该氧化膜的顶部,沉积非常薄的硅层,其用作沟道。由于其薄,可以在该层中建立通道而无需任何额外的掺杂。因此,它被称为完全耗尽的SOI。

图5:FDSOI单元(左)和CMOS单元中的各种漏电流(右)

在另一种技术中,在栅极下方的耗尽区中沉积小的中性区域。这里,沟道厚度不必像FDSOI中所要求的那么薄。这被称为部分耗尽的SOI(PDSOI)。然而,与FDSOI相比,PDSOI倾向于具有更高的V T (因此操作更慢)和更大的栅极效应(因此,更大的漏电流)。因此,由于对V T 的更好控制和急剧减少的漏电流,FDSOI是小工艺节点(通常低于90nm)的首选。

-

低功耗

+关注

关注

10文章

2401浏览量

103692 -

PCB打样

+关注

关注

17文章

2968浏览量

21704 -

华强PCB

+关注

关注

8文章

1831浏览量

27757 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43041

发布评论请先 登录

相关推荐

降低FPGA功耗的设计技术

微处理器的低功耗芯片设计技术详解

怎么降低动态功耗?

实现降低FPGA设计的动态功耗的解决方案

浅析CMOS集成电路的动态功耗

通过动态开启/关闭负载来降低功耗的参考设计

动态电压与频率调节在降低功耗中的作用

cmos动态功耗公式,cmos动态功耗和哪些电路参数有关

非常流行的动态功耗降低技术介绍

非常流行的动态功耗降低技术介绍

评论