由于集成了多核,密集时钟树,增加的AMS(模拟和混合信号),复杂的功率和功能,汽车SoC在设计上变得越来越复杂。复位管理,创新的ADAS/动力总成子系统,各种接口和其他高度可配置的模块。在整个开发周期中,在IP/SoC级别上执行各种事前硅测试场景,目的是揭示设备中的系统级集成问题。这些观察结果将导致某些设计/文档更改,从而产生更强大的客户解决方案。

但是,当某些序列和事件组合在设备上发生时,可能仍会遇到一些极端情况问题从未在设备测试中进行过操作。以便及早发现系统级问题:

时钟同步问题

实现有限状态的回归机器(FSM)

严格的低功耗模式进入/退出

主从互连(交叉开关)周围的性能方面

非法寄存器访问时的系统行为

现在让我们逐一讨论这些领域中的每一个,并说明压力测试中发现的问题。

时钟同步问题

密集时钟树在SoC中实现,具有许多可配置的时钟源,用于驱动内核和外设。此外,这些时钟源具有相关的分频器以允许进一步的可配置性。大多数情况下,由于资源/时间/计算限制,系统和外设时钟之间的所有可能的时钟同步问题都无法被验证工具捕获。这种即兴变成了后硅验证过程中关注的重要领域。

验证工程师应在其代码中实现随机化,以便在外设和内核进行通信时改变时钟源和分频器。这可以帮助捕获一些组合,其中交叉条和外设时钟的不同时钟频率导致功能故障,然后可以正确记录/实施以避免客户应用程序中出现问题。

对已实施的FSM进行回归

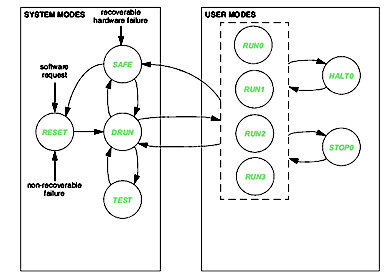

必须彻底验证每个在内部实施FSM的模块(参见图1),以确保所有模块的正确状态转换。所需的事件并确保不仅系统不会因所有有效模式状态转换而出现故障,而且系统应该能够为所有无效模式转换正确恢复。

图1,在SoC中的1 FSM实现

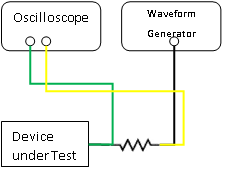

在后硅片期间覆盖这些转换更具挑战性。复位生成模块是一个关键模块,它控制来自各种源/事件的复位断言的系统行为。必须在RGM上开发验证测试,以观察外部复位信号在器件上的周期性断言的影响,以及器件是否每次使用不同的配置都能完全复位。 RGM验证设置的简化说明如下所示:

图。 2 RGM压力验证设置

此类练习可能有助于捕捉RGM的外部复位捕获和边沿检测电路之间可能的竞争条件,这可能导致设备卡在复位状态。

类似地,随机验证将设备从一种操作模式切换到另一种具有不同外围状态的操作模式可以捕获某些灾难性问题。例如,如果在目标模式下未启用PLL的时钟源,则尝试切换到需要外围设备的PLL时钟的目标模式将失败。时钟源依赖性只是导致模式转换失败的因素之一。

严格的低功耗模式进入/退出

设备从低功耗模式成功进入和退出是另一个重要的设计方面,需要对各种系统参数进行全面检查,如状态外围设备,闪光灯,低功率时备用ram。如果闪光灯在低功率状态期间处于睡眠/正常状态,则从低功率模式唤醒时间总是在规格中,而在闪光灯配置为断电时可能不在规格范围内。对唤醒中断的广泛检查甚至可以找到可能导致设备不退出低功耗模式的所有设备配置。低功耗模式下的当前数字是此类测试中的另一个关注领域。

横梁周围的性能方面

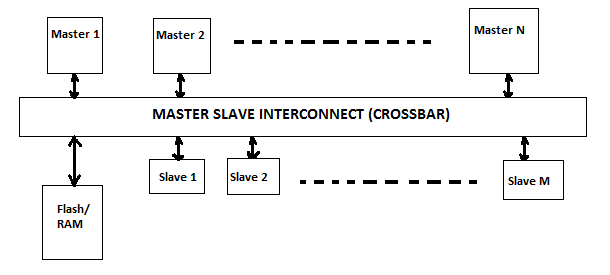

Master-从互连是任何SoC的重要组成部分,它仲裁多个主设备到多个从设备的通信,并通过控制优先级来控制执行流程。下图显示了一个高度简化的横杆版本。

图3.主从互连的简化图

SoC的系统性能是高度依赖于Crossbar实施。此处的任何限制都会严重影响客户的应用程序。在后硅验证期间,应测试不同主设备的各种优先级配置方案,以确保发现交叉开关限制。在多个主设备同时访问来自相同或不同系统存储器组的指令和数据的情况下,可能存在主要饥饿的情况。

非法寄存器访问时的系统行为

通常,设备文档指出,如果在系统级别启用,则对保留/未实现位置的访问可能会生成总线错误并导致异常。但是,访问保留位置的随机验证可能会发现系统行为,这可能会有很大不同,并可能导致设备挂起。某些保留位置可能不会产生总线错误,因为IP设计人员可能不认为存储器孔是保留的。某些位置可能会生成异常,即使没有在系统级别启用它们。无论这些非统一的系统行为是什么,都需要对其进行适当的记录,以便客户在其应用程序中具有正确的实现来处理所有行为。了解此类行为也可用于在未来的IP/SoC设计中实现统一的系统行为。

-

soc

+关注

关注

40文章

4628浏览量

230216 -

PCB打样

+关注

关注

17文章

2982浏览量

23683 -

华强PCB

+关注

关注

8文章

1831浏览量

29333 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44715

发布评论请先 登录

电池的使用在各个领域

宝马慕尼黑工厂正在使用人工智能应用来对工厂的各个领域进行测试

PCB板应力应该如何测试

PCB应力测试仪

离线语音识别模块深入到各个领域当中

发送模块在各个领域的应用

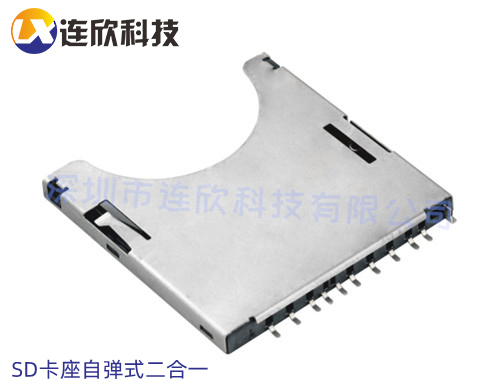

SD卡座自弹式在各个领域的使用特点

汽车SoC上硅后应力测试的各个领域知识解析

汽车SoC上硅后应力测试的各个领域知识解析

评论