同步复位和异步复位都是状态机的常用复位机制,图1中的复位电路结合了各自的优点。同步复位具有时钟和复位信号之间同步的优点,这可以防止时钟和复位信号之间发生竞争条件。但是,同步复位不允许状态机工作在直流时钟,因为在发生时钟事件之前不会发生复位。与此同时,未初始化的I/O端口可能会遇到严重的信号争用。

异步复位的优点是允许状态机运行至直流时钟。此操作是可能的,因为当复位信号独立于时钟发生时,异步复位立即初始化状态机。不幸的是,异步复位可能导致复位信号和时钟之间的竞争条件。竞争条件可能会导致问题,包括亚稳态或错误状态初始化。

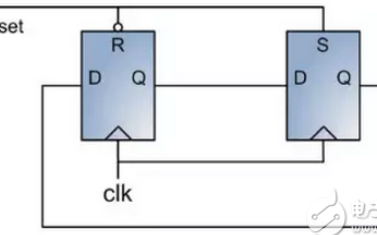

复位电路在检测到异步复位信号后立即置位复位信号。但是,该电路还使复位释放与时钟同步。该电路使用该同步异步复位信号来驱动使用触发器和异步复位输入的状态机。

复位电路由两个背靠背D触发器组成,可同步异步复位信号。此外,异步复位会使D触发器输出立即变为低电平。图1还显示了电路Verilog描述的相应信号名称(清单1),您可以立即将其合并到设计或仿真中。使用Altera Max + PlusII的清单1中的Verilog代码的仿真波形。观察到当系统断言输入复位信号irst_n时,电路立即断言输出复位信号(orst_n)。另请注意,复位释放与两个周期内的时钟同步。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

PCB打样

+关注

关注

17文章

2982浏览量

23683 -

华强PCB

+关注

关注

8文章

1831浏览量

29333 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44715

发布评论请先 登录

相关推荐

热点推荐

Xilinx FPGA异步复位同步释放—同步后的复位该当作同步复位还是异步复位?

针对异步复位、同步释放,一直没搞明白在使用同步化以后的复位信号时,到底是使用同步

发表于 06-21 09:59

•2408次阅读

Xilinx FPGA的同步复位和异步复位

对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和

发表于 07-13 09:31

•7730次阅读

FPGA同步复位和异步复位

FPGA(Field-Programmable Gate Array,现场可编程门阵列)中的复位操作是设计过程中不可或缺的一环,它负责将电路恢复到初始状态,以确保系统的正确启动和稳定运行。在FPGA设计中,复位方式主要分为

同步复位和异步复位电路简介

同步复位和异步复位电路简介

评论