微处理器提供商Sandcraft使用FormIT提供芯片设计,FormIT是Sapphire Design Automation的一种新型物理设计工具,提供电气分析,放置和优化。 Sandcraft的CAD总监Salah Gasti在此描述了FormIT如何帮助Sandcraft实现更好的布局并提高路线前时序估计的准确性。但是,Gasti希望在路由领域看到一些额外的功能。 Sapphire的FormIT用于包含随机逻辑的20%的设计;其他80%使用自定义布局方法完成。

Sapphire还提供了噪声和功耗分析的配套工具,本示例中未使用这些工具。

EEdesign:您使用Sapphire的FormIT进行了哪些设计?

Gasti:这是我们最新的处理器,64位Mips处理器,具有多种扩展功能。它有1000万到1500万个晶体管。我们在随机逻辑部分使用了经过综合的工具。

EEdesign:你以前的工具流程是什么,有什么问题?

Gasti:我们使用Synopsys [Design Compiler],使用布局布线工具 - 我不想识别供应商。我们有小块。平均值就像8-K门。但它们过度约束,速度非常非常重要。我们遇到的一个大问题是我们的综合和路线后时间估计之间的差异。差异有时超过三分之一。我们需要有更好的贴装工具,所以我们得到了Sapphire。

EEdesign:您对FormIT有哪些改进?

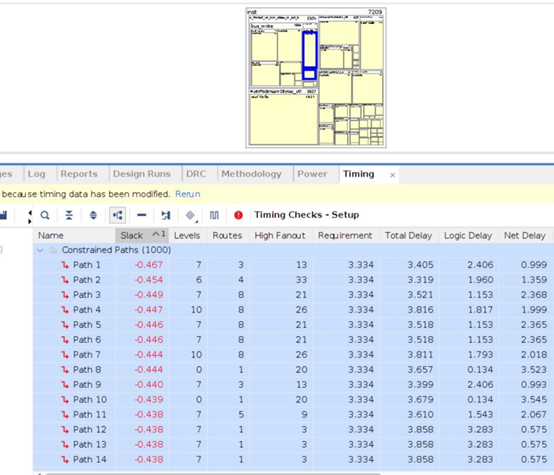

Gasti :我们80%的时间都获得了更好的结果。他们有放置优化,我们可以升级和缩小[缓冲],这也允许时序收敛。他们没有逻辑重组 - 我相信他们正在努力。但每次我将Sapphire的结果与具有逻辑重组的工具进行比较时,Sapphire仍然会给出更好的结果。

在前一代产品中,合成产品和我们的产品之间可能存在三分之一的时间差异。当经过蓝宝石时,这种差异降到了10%。现在我们不需要改变线负载模型中的任何内容。

EEdesign:你使用了哪些FormIT功能?

加斯蒂:他们还没有路由。他们所拥有的是能够进行放置,进行优化放置以及进行一些自定义优化的可能性。例如,您可以说,“我希望您只优化10条最差路径。”如果您遇到拥塞问题,或者有太多单元格非常紧的块,只需优化10条最差路径就可以让您接近目标。

它们也有很好的时序分析工具,所以你可以看到芯片的表现。路由后可以进行反向注释。此外,他们有能力修复保持时间。他们可以创建时钟树,我们使用它来为我们的扫描链插入时钟树缓冲区。

EEdesign:FormIT如何适合您的设计流程?

Gasti:我们在合成后使用它。放置完成后,我们进入路由器 - 我们不会重做[Sapphire]放置。然后我们进入时序验证,LVS [布局与原理图]和提取。

EEdesign:FormIT是否加速了设计过程?

加斯蒂:是的。在此之前,我们合成,做了布局和布线,进行了就地优化,运行了ECO [工程变更单]并希望有时间收敛。现在我们有一个一步过程,可以让事情更快完成。

EEdesign:谁在你的工厂运行FormIT?逻辑设计师是否容易学习?

Gasti:我们运行它。它由逻辑设计师使用,而不是由布局人员使用。这很容易学习。

EEdesign:FormIT是否会生成易于路由的展示位置?

加斯蒂:在这个领域他们有点缺乏。我们要求他们做出改进,我们看到他们的第二代有所改进。有些街区在第一代遇到了一些拥堵问题。

EEdesign:您是否看过其他一些新的物理设计解决方案?蓝宝石如何比较?

Gasti:我们看过Avanti,Cadence,Sapphire和Monterey - 我们没有看[Synopsys]物理编译器。我相信蓝宝石对于我们正在进行的时间限制块更好。

EEdesign:您希望看到的任何缺点或区域有所改进吗?

加斯蒂:嗯,我确实相信一个缺点就是他们还没有做路由。问题是,放置可能没问题,但如果你没有全局路由器,你最终会遇到拥塞等问题。如果路由在他们手中,他们可以做很多安置并处理所有这些问题。另一件事是,如果你有路由,噪音分析真的会更准确。但是,我认为他们有一个相当强大的噪音分析工具。

-

时序关联

+关注

关注

0文章

2浏览量

5908 -

PCB打样

+关注

关注

17文章

2968浏览量

21713 -

华强PCB

+关注

关注

8文章

1831浏览量

27771 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43055

发布评论请先 登录

相关推荐

IIC总线时序启动时序

时钟IC改善通信基础设施时序信号链的性能-- AD9553

时序关联/质理检验方针助缩短开发周期

静态时序分析在高速 FPGA设计中的应用

Sapphire基于Web的噪声分析知识简介

从已布线设计中提取模块用于评估时序收敛就绪状态

英特尔发布了关于Sapphire Rapids的简短更新

SAPPHIRE SF NX 简介

Sandcraft改善了与Sapphire的FormIT的时序关联

Sandcraft改善了与Sapphire的FormIT的时序关联

评论