SAN JOSE - Circuit Semantics Inc.推出了一种自动功能提取工具,可让设计人员转换硬知识产权(IP设计成门级Verilog模型,然后通过逻辑综合工具将其转换为新设计。

该工具有望以指数方式加速IP库建设工作。缺点是它可能被误用于反向工程核心。

来自Circuit Semantics的DynaModel工具生成全功能的Verilog仿真模型,从全定制和硬核知识产权模块中抽象出来,以支持在新设计中重用传统IC布局,公司营销总监Arnie Becker说道。 。

Becker表示,DynaModel的目标是系统和半导体公司,这些公司拥有大型传统硬核库,希望在下一代设计中重用代码。

“如果你看看像意法半导体,摩托罗拉和英飞凌这样的公司,他们希望重用原有的IP,将它们放在他们的存储库中并有一些方法来迁移它们,”Becker说。 “这将使他们能够做到这一点。”

该工具本质上是Circuit Semantics的DynaCell和DynaCore表征工具的更高容量版本。 Becker表示,该工具迄今已用于500,000晶体管设计和模块,该公司并未意识到物理容量限制。他说,当前32位配置的工具确实需要大量内存。但该公司正在考虑将该工具移植到64位,这将增加速度并减轻内存需求。

不同的设备

Becker说该工具与流程迁移工具的不同之处在于DynaModel生成门级模型,而流程迁移工具将物理设计从物理域中的一个流程几何转换为另一个流程几何。

工程师为该工具提供Spice网表和配置文件。 DynaModel读入Spice网表,对块进行分区,然后为每个分区提取函数。

该工具然后生成一个门级功能模型,具有单位延迟时序支持,Verilog网表以及.lib和TLF文件。未来版本将在模型中嵌入时序。

在设置DynaModel期间,Becker说,用户将所有顺序元素的结构识别为DynaModel,并提供Verilog映射文件,用于将该顺序元素表示给综合工具。

Becker说这个映射文件可以是顺序元素的简单HDL描述,也可以像在该块中映射的技术中表示的门级网表一样复杂。他说,如果映射文件是HDL描述,由DynaCore生成的最终Verilog模型将成为独立于技术的“软IP”模型。

在提取功能模型后,工程师可以使用逻辑综合工具将设计映射到新技术中。 Becker表示,Circuit Semantics意识到该工具也可能被滥用,实际上是对IP供应商的硬核进行逆向工程 - 也就是说,如果该供应商为客户提供Spice源。

他说IP供应商担心人们可能滥用这个工具,所以如果有人想非法使用它,Circuit Semantics鼓励IP供应商使用加密。

将针对性能优化的全定制设计提供给自动ASIC合成流程通常会导致设计变慢。 Becker表示,为了解决这个问题,该公司计划宣布与Prolific和Ultima技术合作,根据优化的Spice网表创建流程,重新布局设计以保持完全自定义性能。

-

合成模型

+关注

关注

0文章

2浏览量

5813 -

PCB打样

+关注

关注

17文章

2968浏览量

21710 -

华强PCB

+关注

关注

8文章

1831浏览量

27762 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43051

发布评论请先 登录

相关推荐

NLPIR平台提供快捷简便的语义分析工具

EIQ onnx模型转换为tf-lite失败怎么解决?

将Pytorch模型转换为DeepViewRT模型时出错怎么解决?

将ONNX模型转换为中间表示(IR)后,精度下降了怎么解决?

基于行为特征的语义工作流修正算法

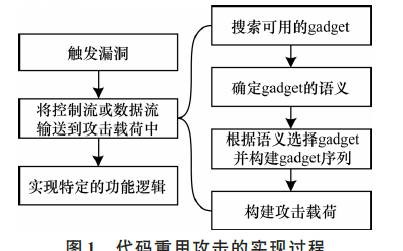

工具SemExpr可实现gadget搜索与语义分析

电路语义工具将硬IP转换为可合成模型

电路语义工具将硬IP转换为可合成模型

评论