应用材料公司今天为其Mirra Mesa化学机械平面化(CMP)推出了两种新的铜工艺它表示支持全系列双大马士革芯片集成方案。

Mirra Mesa工艺与Applied的Endura屏障/种子和Electra机电电镀系统集成,作为捆绑的一部分 - Applied正在追求的模块策略(见4月5日的故事)。应用材料公司CMP产品组副总裁兼总经理克里斯史密斯说:“这套设备让客户有机会购买预先集成的互连解决方案,帮助他们快速扩大工厂的铜制造量。”

首次快速去除铜材料后,客户可以选择非选择性或选择性工艺来抛光阻隔薄膜,这取决于他们的双大马士革整合策略,该公司表示。非选择性工艺采用新的成本效益方法去除阻挡膜,以及未加盖的介电材料,如氧化物,氟化硅酸盐玻璃(FSG)和黑钻石膜。

选择性CMP工艺旨在平坦化并保留用于封顶低k电介质应用的顶部介电层。这两种解决方案都可以简化工艺流程,无需额外的电介质抛光步骤,从而降低制造成本。

“铜CMP是芯片制造商面临的最关键挑战之一,”史密斯说。 “将我们的下一代铜工艺与Mirra Mesa系统的多板结构,先进的抛光头技术以及我们新的FullScan端点技术相结合,为体积铜生产创造了一种高生产率的抛光工具。”

FullScan端点技术可精确识别整个晶圆上的薄膜去除点。结合工艺顺序,这可以最大限度地减少铜布线结构的凹陷和腐蚀,创造出创建多层互连所需的平面表面形貌,Smith解释道。

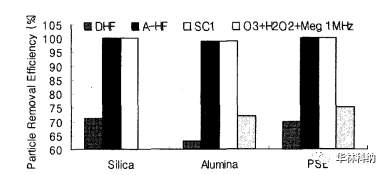

系统的铜工艺已经过特性测试和测试缺陷水平。该系统的Mesa集成式CMP后清洗站采用超声波清洗技术和双面刷洗,有助于抵抗腐蚀,去除晶圆两侧的颗粒和浆料残留物,包括非常小的凹陷特征和难以倾斜的区域。

-

晶圆

+关注

关注

52文章

4922浏览量

128041 -

PCB打样

+关注

关注

17文章

2968浏览量

21721 -

华强PCB

+关注

关注

8文章

1831浏览量

27779 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43061

发布评论请先 登录

相关推荐

什么是晶圆级封装?

LABVIEW 如何把 “加 减” 图片和数值输入控件,捆绑在一起做控件使用。

光敏电阻串在一起或者并在一起

为什么无法测试与STM32CubeID捆绑在一起的通用ARM工具链呢

如何让ESP32C3与OpenOCD捆绑在一起?

如何将UID码与M031 LDROM和APROM固态软件捆绑在一起

传苹果要将AirPods与新款iPhone一起销售

DHF在氧化后CMP清洗工艺中的应用

晶圆模块捆绑在一起的新型铜CMP工艺

晶圆模块捆绑在一起的新型铜CMP工艺

评论