“毫米波雷达”

无论是炫酷的谷歌Project Soli手势识别应用,还是特斯拉车型中的防撞探测雷达方案,英飞凌种类丰富的毫米波雷达产品都能一一应对,完美覆盖当下热门的24GHz、60GHz以及77GHz雷达应用,如工业、汽车、可穿戴设备等。点击图片即可详细了解

英飞凌毫米波雷达产品传送门

二

在过去的2017年里,各类智能音箱产品层出不穷,智能音箱正处于AI行业的风口。而D类音频放大器,正是为音箱产品提供好音质的核心。英飞凌致力于提供一整套全面的分立和集成IC产品组合,从而简化高效率D类放大器的设计。

戳图片get到好音质的核心——D类音频放大器!

D类音频放大器的优势莫非就是高音甜、中音准、低音沉……

好声音,为英飞凌高效率D类音频功率放大器“转身”

三

“智能路灯”

智能路灯的作用可不仅仅是照明,它还能用作电动汽车的充电桩,以及空气质量和交通规则的测量工具。这样一个使用了英飞凌众多高能效元器件的智能路灯,已经成为了智慧城市的一个全能型节点。这可是全球最先进的智能路灯之一哦,点击图片看设计套路

智能路灯设计传送门

四

“无线充电”

现在说起无线充电,粉丝们或许想到苹果iPhone X等智能手机的推出,引领了无线充电的风潮。但古语有曰:兵马未动,粮草先行。早在2017年伊始,小编可就交出了“粮草级方案”,为大家准备了相关题材的文章哦,赶紧戳图片了解《无线充电设计的武功秘籍》

无线充电秘籍传送门

更有电磁感应式与磁共振式无线充电的详细剖析!

无线充电这么火,英飞凌专家和您品一品

再赏无线充电:磁共振式带来更好用户体验

五

“AI白皮书”

AlphaGo大战柯洁是2017年AI界的标志性大事件。但你可能不知道,对弈的每场棋局需要消耗约30,000度电能,如此能耗显然无法商用。这份英飞凌低功耗AI白皮书,为你解读先进的电源控制技术和开关技术,在高功率AI应用中创造出最高效的一流电源解决方案。

戳上图淘《低功耗AI白皮书》

六

“环保发电机”

想象一下,当你希望在远离家门的地方,比如春游、露营时享受下依赖电力的娱乐活动,便携式环保发电机是不是就立马成为了你和朋友们开party的神器呢?如果要找这一类发电机的方案,记得要认准“英飞凌inside”哦,点击图片了解

便携式环保发电机方案传送门

更有爆款方案讲解能效与成本的那些事儿。

想将便携式发电机项目提升至新水准?试试这套兼顾能效与成本的“爆款”方案!

七

“4地巡演”

2017年夏季,英飞凌中国在北上厦深四地举办了轰动电源界的“极智能效 尽享随芯”电源管理与射频巡回研讨会。这一次全国巡演汇聚了不同区域近5700名工程师参与,与众多特邀行业技术大牛,带来了一场行业技术研讨盛会。想看返场Encore的筒子们记得戳图

看全国巡演返场Encore点这里!

八

“热播视频”

英飞凌电源管理与射频在线技术社区已经正式上线了“热播视频”版块。这里是电源管理与射频工程师的知识课堂,英飞凌专家将用完整视频的方案,为筒子们诠释Infineon-inside的高效方案,并已全部汇总为中文讲解。

工程界都在追的热播剧集在这里

九

“辅助电源”

辅助电源哪家强?小编遥指英飞凌。辅助电源应用十分广泛,以家电辅助电源为例,其在于为家电智能化提供稳定的直流电压和电流。英飞凌最新推出的第五代CoolSET产品,就有帮助实现在不同负载条件下提高器件效率、加速器件启动速度等等好处。

十

“圣诞漫画”

《圣诞老人送礼记》漫画在2017年圣诞节的前夕正式上线,这是咱们账号首次推出的故事情节漫画。利用英飞凌先进半导体元器件、打造提高生活品质的科技产品,帮助圣诞老人顺利送达礼物。如果喜爱这一漫画,请在评论中为它打Call!

-

电源管理

+关注

关注

115文章

6185浏览量

144647 -

便携式

+关注

关注

0文章

328浏览量

29834 -

无线充电

+关注

关注

1294文章

3278浏览量

316761

发布评论请先 登录

相关推荐

大臂展、大负载、具身智能……大族机器人2024年度关键词回顾

回顾2024年度润和软件与openEuler的精彩瞬间

中国信通院魏亮:2024人工智能产业十大关键词解读

Qorvo在射频和电源管理领域的最新进展

浅析2024年半导体行业的两大关键词

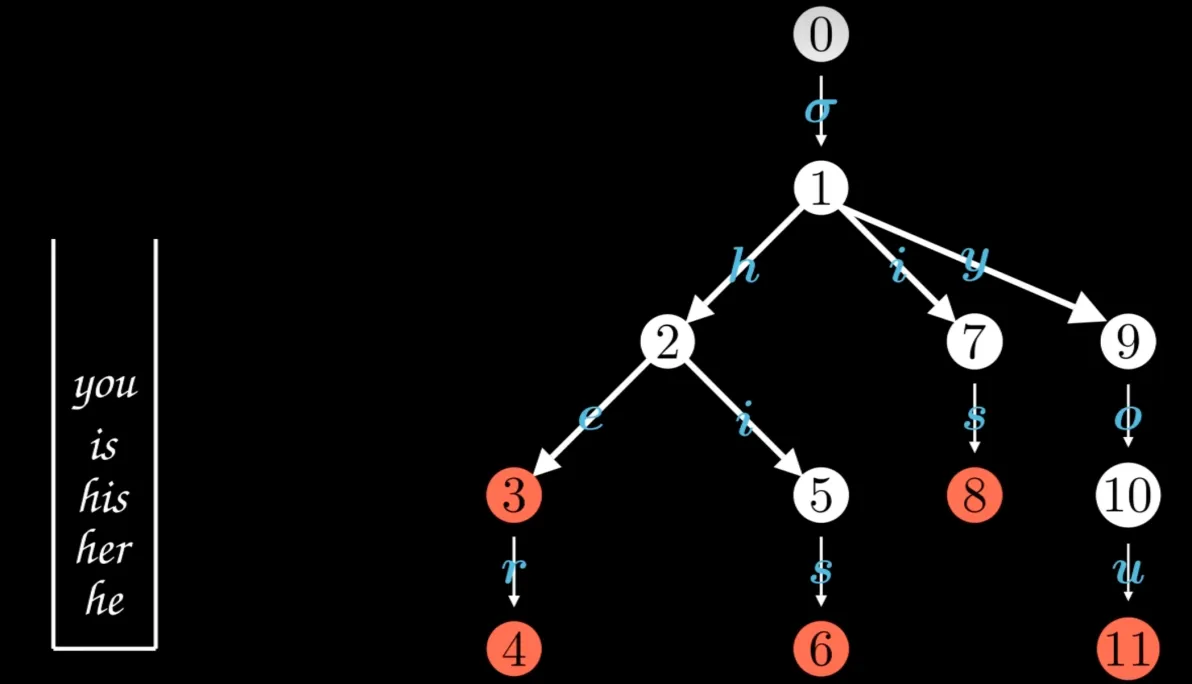

探索AC自动机:多关键词搜索的原理与应用案例

什么是射频电源?它有哪些应用?

中国信通院发布“2024云计算十大关键词”

浅谈交直流混合微电网能量管理系统关键技术

集创北方iML8986荣获AspenCore“年度最佳电源管理IC”

微软Edge浏览器将引入PDF阅读器,实现关键词自动生成功能

深开鸿用三个关键词,为你解读《2023 OpenHarmony 年度运营报告》

回顾电源管理与射频应用的年度关键词

回顾电源管理与射频应用的年度关键词

评论