管理高速PCB中的损耗

到目前为止,大多数数字系统工程师都知道,当信号达到足够高的频率时,他们需要担心PCB走线和其他导线的损耗。信号。在20世纪90年代大多数设计中典型的较低频率(高达约200 MHz),损失是无关紧要的,或者是很少需要很少注意的微小影响。其他信号完整性问题,如反射,总延迟和串扰,则更为重要。分析工具可以通过假设“无损”传输线给出准确的答案,这些传输线可以快速模拟并且易于表征。

但是随着设计频率增加到300-400 MHz范围,特别是引入了超高速千兆位-per-secondserial信号,丢失突然变得不可忽视。接收器IC上的示波器波形显示出严重的信号衰减,振幅显着衰减,边缘明显变圆和延迟。模拟器被迫通过添加有损传输线算法来响应。

尽管如此,许多设计师仍然不确定何时损失非常重要,原因是什么,如何衡量,以及如何最大限度地减少损失。本文将探讨所有这些问题。

信号丢失的根源

首先,“损失”究竟是什么意思?

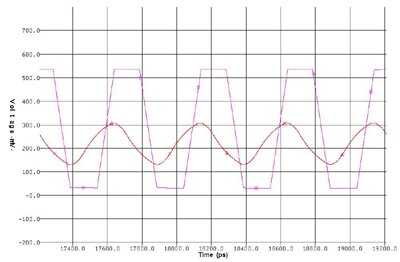

图1使答案非常图形化。它显示了一个时钟信号驱动36英寸带状线PCB走线,埋在典型的FR-4介电材料中。注意信号在远端(红色波形)看起来与在跟踪的驱动端(紫色)有多么截然不同?它的振幅严重衰减,其上升/下降时间严重延长。实际上,当信号通过迹线时,信号看起来几乎像正弦波。

为什么信号在跟踪端看起来很差?显然,它在传播时失去了很多能量;单独的幅度减小表明了这一点。但请注意,其高频成分似乎特别受到重创。输入信号的尖锐边缘(由高频内容产生)几乎完全消失在输出中。但为什么呢?

图1 ??在典型的FR-4电介质中,TDR信号驱动36英寸带状线PCB迹线。注意当驱动器信号(紫色)到达迹线的远端(红色)时严重的幅度和边沿时间退化。

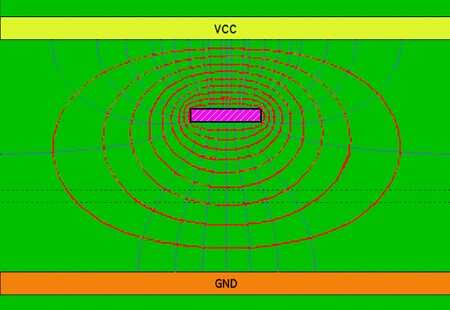

我们的信号经历的一些损失是由于导体中的能量进食机制,以及电介质中的另一种效应。导体的罪魁祸首就是阻力;在FR-4中,责任落在“介电损耗”上,它直接从信号场中窃取能量。介电材料中的电场分布如图2所示。

图2 - 图1 PCB的横截面图,显示了信号传输时导体,两个平面,电介质和电磁场线指挥。电场线为蓝色;红色磁性。

任何电气设计人员都希望PCB走线具有一定的电阻。可能令人惊讶的是,高频电阻远大于直流电阻。原因是“趋肤效应”,即高频电流聚集到导体边缘的趋势,而不是流过整个可用的横截面。高频信号看到的电阻远大于预期的电阻,并且它与频率的平方根成比例地增加。

介电损耗与所有电介质都含有极化分子的事实有关在EM场的存在下移动。高频场非常快速地振荡,当极性分子与场同步移动时,它们开始加热介电材料。热量只有一个可能的来源 - 信号本身的能量。事实证明,介电损耗随着频率的增加而无情地增加,并且与信号频率成正比。

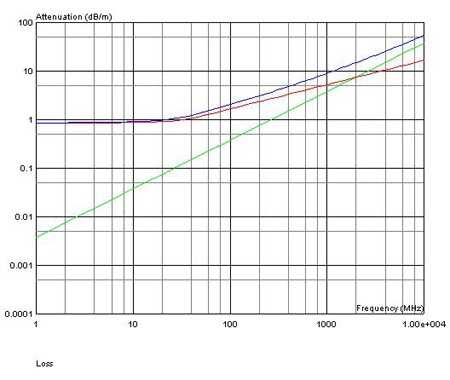

在前面的段落中埋藏是一个不祥的事实。皮肤电阻随频率的平方根而变化,但介电损耗直接缩放 - 这意味着在足够高的频率下,介电损耗的衰减应该超过皮肤损耗的衰减。

图3说明了这正是发生的事情。该图显示,对于我们一直在讨论的同一导体,电阻损耗(红色)和介电损耗(绿色)。注意介电损耗如何在高频下超过电阻损耗。这意味着对于超高速信号传输,总衰减越来越多地由所使用的介电材料决定。

图3 - 对于图1的导体,电阻(红色)和介电损耗(绿色)与频率(对数刻度)的关系图。请注意,在低频时,电阻损耗占主导地位,但在高频时,介电损耗会超过电阻。

这就是旧的FR-4成为一个大问题的地方。 FR-4基本上是一种低成本,历史悠久,混合玻璃纤维和胶水的混合物;除了其损耗特性和严格的过程控制外,所选择的材料。然而(主要是出于成本原因),数字设计师仍在顽固地试图通过它推动高频信号。如前面的数字所示,随着数据率越来越高,这将变得非常困难 - 并且最终是不可能的。

在旁观者的眼中

与图1中的信号看起来一样糟糕,它在现代高速系统中的行为甚至比人们预期的还要糟糕。只有当我们以特殊的方式观察信号时才会变得明显 - 眼图 - 这些日子在非常高速的信号传输中是必不可少的。

多年来,数字设计依赖于稳定的饮食习惯。众所周知的技术;宽并行总线,同步时钟,简单的建立和保持型定时和轨到轨切换。但随着对更快系统的追求推进,最终旧策略变得紧张;信号之间的串扰变得越来越难以避免,偏差控制变得困难,时间裕度变得不可能紧张。

最后,大约五六年前推出了一种新的信号传递方式,这些信号提供了一些缓解,首先是形式的LVDS(低压差动摆动)。这些器件引入了两个关键变化:较低的信号摆幅电压(即使降低了噪声容限)允许较慢的摆率;和差分信号,大大减少了串扰和辐射发射,并允许更窄,更快的数据路径。

过去两年看到LVDS型信号的爆炸性杠杆化进入了一场全面的革命 - 引言高速串行总线,可将数百MHz范围内的数据速率(和信号频率)推至1 GHz以上。突然间,广泛的并行总线和全球时钟(在某些情况下,任何类型的显式时钟)已成为通过; “in”是超快速,非常窄,全差分,低电压摆动标准,如PCI Express,RapidIO和XAUI。

这将我们带回眼图。在新的高速串行世界中,数据速率如此之高(为了补偿较窄的数据路径,每个“通道”必须承载更多流量),各个位之间的时间通常几乎不比上升/下降时间长得多携带比特的信号。丢失突然成为一个大问题,因为信号上升/下降时间的任何增加都会导致整个比特流失败。更糟糕的是,误差幅度很小,称为符号间干扰(ISI)的现象占主导地位。

ISI基本上意味着数据速率相对于信号的上升时间而言是如此之高,以至于给定位的确切形状和时间取决于先前的位历史。这可能是因为驱动器IC本身不能保证位之间的完全规则定时(“抖动”的形式),或者因为反射和其他效应比位间隔更慢地消失,或者由于电压的微小变化由于位历史而产生的级别。例如,1的长序列会导致平均电压电平向上漂移。通常,所有这些影响同时适用。

在信号完整性分析的“经典”时代,有可能专注于信号的单个上升沿或下降沿来判断其“良好” - 是否响起,打捞,需要终止等等。但是在高速串行信令中,在进行任何绑定判断之前,必须按顺序分析多个比特。更糟糕的是,从来都不清楚什么位历史(什么序列,多长时间)会产生最坏情况的行为。唯一的办法是用一个长的随机比特序列来驱动一个被测试的数据路径,并希望任何病理行为都变得明显。

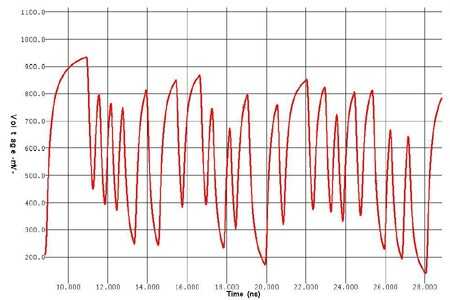

图4显示了这种模拟的一部分。迹线有意长,以包含健康剂量的高频损耗,其表现为信号衰减和降低的边缘时间,其长度与位间隔相似。符号间干扰很容易看出;特别是电压电平明显取决于先前位的历史。然而,分析具有这种形式结果的数据路径充其量是乏味的。想象一下,滚动数百甚至数千位,试图想象何时会发生某种情况会混淆接收器IC。

图4 - 高速串行数据路径仿真的一部分,用PRBS(伪随机比特序列)驱动,以便运用尽可能多的内部 - 符号干扰尽可能。请注意每个位的形状和位置与先前位历史记录的明确依赖关系。

输入眼图,这是一种将长模拟结果压缩成如图4所示的简单技术单一,易于理解和解读的图片。从概念上讲,眼图很容易创建;只需按照与位时间相关的规则间隔对图4的波形进行切割,将每个切碎的段放在前一段的顶部,然后查看一个重叠堆中的所有数据。图5显示了此过程的结果,与图4中显示的数据完全相同。

图5 - 与以下相同的模拟图4,但数据覆盖在眼图中。请注意数据中间的小开口 - 一个近乎闭合的眼睛,这对这条信号路径造成了灾难。解释眼图比在标准模拟输出中滚动长序列更快更确定。一目了然,眼睛的“开放性”告诉我们数据流是否可以接受。

图5中的眼睛基本上是一场灾难。在不知道特定信令技术的细节的情况下,接收器IC很难恢复由驱动器发送的所有(或可能是任何)数据。接收到的位在时间和电压方面明显漂移。

如果他们没有,这张照片看起来很像“眼睛”;由高低信号状态形成的上部和下部“盖子”中间的宽开口。不幸的是,这里的眼睛几乎是闭着的。这是一个严重麻烦的数据路径 - 眼图使其一目了然。

睁大眼睛?

信号在图5中,在以下条件下产生:40英寸迹线,4密耳迹线宽度,标准FR-4电介质,具有“损耗角正切”(广泛使用的介电损耗测量)0.02。在本节中,让我们看看减少损耗如何改善信号质量以及眼图如何使我们获得的改进立即明显变得明显。

之前,我们注意到丢失的一个组成部分是由于导体本身,以皮肤抵抗的形式。因此,如果我们能够诱导高频信号的电流流过更大的金属横截面,那么对信号的阻抗就会减小,损失就会减少。

我们知道,高频电流往往会挤在导体的边缘,靠近周边。因此,如果我们增加导体的周长,我们应该减少损失。增加轨迹横截面周长的最简单方法是扩大轨迹。从布线密度的角度来看,4密耳的走线宽度是很好的,但不是最小化损耗的理想选择。让我们尝试将迹线宽度从4密耳增加到8密耳。当然,我们也会增加电介质厚度,以保持50欧姆的特性阻抗。

图6显示了两个产生的眼图,一个在另一个之上(红色表示4密耳的迹线,黄色为8密耳)。有趣的是,这个简单的改变?更宽的走线宽度??确实减少了损耗并提高了信号质量,正如8密耳宽的迹线更开阔的眼睛所示。

图6 ??与图5中的模拟相同,使用4密耳宽的迹线(红眼图)运行一次,使用8密耳(黄色)运行一次。更宽的迹线具有更少的皮肤效应损失,因此更好的信号质量,如更开放的眼睛所示。

让我们进行另一项改变,我们知道这将进一步减少信号损失。我们已经攻击了皮肤抵抗力;现在让我们去介电损耗。降低介电损耗的最简单方法是将材料从图4-6中使用的相对有损的FR-4改变为具有更好性能的材料。事实证明,这种电介质存在,尽管它们的成本并不像FR-4那么低或广泛使用。在这些更好的材料中,损耗角正切可低至FR-4的十分之一;让我们尝试一个名为GML3000的损耗角正切为0.004。

图7显示了前后效果。果然,信号质量再次提高;低损耗的眼睛(紫色)比其伴侣打开得更宽。不幸的是,用这种外来电介质制造的PCB比用FR-4制造的PCB更昂贵?正如我们不得不降低布线密度以降低皮肤电阻(更宽的走线),现在我们面临更高的制造成本,因为我们试图降低介电损耗。

图7 ??与图6中更好的眼睛相同的模拟,使用典型的FR-4电介质(损耗角正切= 0.02;黄眼图)运行一次,使用低损耗电介质运行一次(损耗角正切= 0.004;紫色)。低损耗材料对眼图开度有了实质性的改善,但会导致PCB成本更高。

结论

<我们已经探索了信号丢失的概念,描述了导致它的原因,展示了它对高速信号的影响是如何测量的,并且看到了一些如何最小化它的例子。显然,在高速系统中,损耗是一个日益严重的问题,特别是在高速串行信号的新世界中。

随着数据速率增加到信号上升/下降时间与位间隔相同的程度,眼图是判断数据流是否受损失严重影响的重要工具,接收器IC不再能够可靠地恢复数据。眼图也可以立即明确是否最大限度地减少损失的尝试实际上提高了信号质量,以及增加了多少。

Steve Kaufer是MentorGraphics高速工具工程总监。他在Innoveda和PADS Software担任过类似的职位,而加入PADS的priorto是HyperLynx的联合创始人,HyperLynx是信号完整性软件的早期供应商。他拥有硬件和软件工程方面的经验,并拥有西雅图大学的电子工程和物理学位。可以通过steve_kaufer@mentor.com与他联系。

Eric Bogatin在麻省理工学院获得物理学学士学位,在亚利桑那大学获得物理学硕士和博士学位。 1980年在图森工作。20多年来,他一直积极参与信号完整性和互连设计领域。他曾在AT&amp; T贝尔实验室,Raychem公司,Sun Microsystems和Ansoft工作多年。最近,他将他的咨询公司Bogatin Enterprises与GigaTest Labs合并,担任首席技术官,并教授信号完整性短期课程。他已就此主题撰写了3本书和100多篇论文。可以通过eric@gigatest.com与他联系.www.gigatest.com

-

pcb

+关注

关注

4322文章

23128浏览量

398612 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43089

发布评论请先 登录

相关推荐

高速PCB设计指南

高速信号传输链路的损耗和均衡

管理高速PCB的损耗有多大

管理高速PCB的损耗有多大

评论