在我们刚一开始接触到51单片机的时候对P0口必须加上上拉电阻,否则P0就是高阻态。

对这个问题可能感到疑惑,为什么是高阻态?加上拉电阻?今天针对这一概念进行简单讲解。

高阻态

高阻态这是一个数字电路里常见的术语,指的是电路的一种输出状态,既不是高电平也不是低电平。

如果高阻态再输入下一级电路的话,对下级电路无任何影响,和没接一样,如果用万用表测的话有可能是高电平也有可能是低电平,随它后面接的东西定。

高阻态的实质

电路分析时高阻态可做开路理解,你可以把它看作输出(输入)电阻非常大。

它的极限可以认为悬空,也就是说理论上高阻态不是悬空,它是对地或对电源电阻极大的状态。而实际应用上与引脚的悬空几乎是一样的。

高阻态的意义

当门电路的输出上拉管导通而下拉管截止时,输出为高电平,反之就是低电平。

如果当上拉管和下拉管都截止时,输出端就相当于浮空(没有电流流动),其电平随外部电平高低而定,即该门电路放弃对输出端电路的控制 。

典型应用

在总线连接的结构上。总线上挂有多个设备,设备与总线以高阻的形式连接。这样在设备不占用总线时自动释放总线,以方便其他设备获得总线的使用权。

大部分单片机I/O使用时都可以设置为高阻输入。高阻输入可以认为输入电阻是无穷大的,认为I/O对前级影响极小,而且不产生电流(不衰减),而且在一定程度上也增加了芯片的抗电压冲击能力。

高阻态常用表示方法:高阻态常用字母 Z 表示。

在一个系统中或在一个整体中,我们往往定义了一些参考点,就像我们常常说的海平面,在单片中也是如此,我们无论说是高电平还是低电平都是相对来说的。明确了这一点对这一问题可能容易理解。

单片机中的高阻态

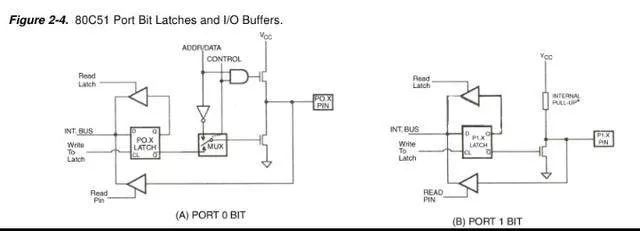

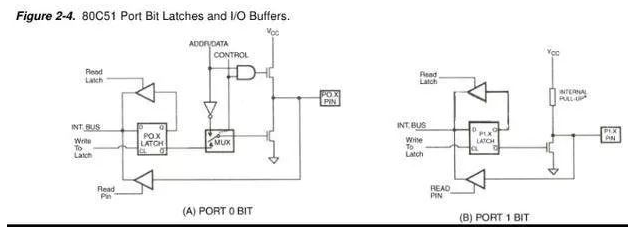

在51单片机,没有连接上拉电阻的P0口相比有上拉电阻的P1口在I/O口引脚和电源之间相连是通过一对推挽状态的FET来实现的,51具体结构如下图。

组成推挽结构,从理论上讲是可以通过调配管子的参数轻松实现输出大电流,提高带载能力,两个管子根据通断状态有四种不同的组合,上下管导通相当于把电源短路了,这种情况下在实际电路中绝对不能出现。

从逻辑电路上来讲,上管开-下管关开时IO与VCC直接相连,IO输出低电平0,这种结构下如果没有外接上拉电阻,输出0就是开漏状态(低阻态),因为I/O引脚是通过一个管子接地的,并不是使用导线直接连接,而一般的MOS在导通状态也会有mΩ极的导通电阻。

到这里就很清楚了,无论是低阻态还是高阻态都是相对来说的,把下管子置于截止状态就可以把GND和I/O口隔离达到开路的状态,这时候推挽一对管子是截止状态,忽略读取逻辑的话I/O口引脚相当于与单片机内部电路开路,考虑到实际MOS截止时会有少许漏电流,就称作“高阻态”。

由于管子PN节带来的结电容的影响,有的资料也会称作“浮空”,通过I/O口给电容充电需要一定的时间,那么IO引脚处的对地的真实电压和水面浮标随波飘动类似了,电压的大小不仅与外界输入有关还和时间有关,在高频情况下这种现象是不能忽略的。

总之一句话高阻态是一个相对概念。在使用的时候我们只要按照要求去做,让我们加上拉我们就加上,都是有一定道理的。

-

电阻

+关注

关注

86文章

5535浏览量

172355 -

单片机

+关注

关注

6039文章

44586浏览量

636715

原文标题:单片机中的高阻态就应该这样理解!

文章出处:【微信号:mcuworld,微信公众号:嵌入式资讯精选】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

单片机中的高阻态

单片机中的高阻态

评论