噪声是模拟电路设计的一个核心问题,它会直接影响能从测量中提取的信息量,以及获得所需信息的经济成本。遗憾的是,关于噪声有许多混淆和误导信息,可能导致性能不佳、高成本的过度设计或资源使用效率低下。

误区一:降低电路中的电阻值总是能改善噪声性能

噪声电压随着电阻值提高而增加,二者之间的关系已广为人知,可以用约翰逊噪声等式来描述:

erms:均方根电压噪声。

k:玻尔兹曼常数。

T:温度(单位为K)。

R:电阻值,B为带宽。

这让许多工程师得出结论:为了降低噪声,应当降低电阻值。虽然这常常是正确的,但不应就此认定它是普遍真理,因为在有些例子中,较大的电阻反而能够改善噪声性能。

在大多数情况下,测量电流的方法是让它通过一个电阻,然后测量所得到的电压。根据欧姆定律V= I×R,产生的电压与电阻值成正比,但正如上式所示,电阻的约翰逊噪声与电阻值的平方根成正比。由于这个关系,电阻值每提高一倍,信噪比可提高3dB。在产生的电压过大或功耗过高之前,此趋势一直是正确的。

误区二:所有噪声源的噪声频谱密度可以相加;带宽可以在最后计算时加以考虑

将多个噪声源的噪声频谱密度(

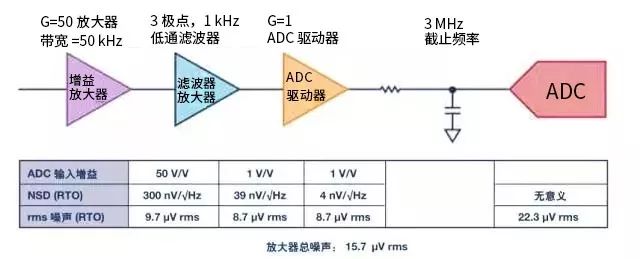

图1:使用rms噪声而不是频谱密度进行噪声计算的理由

图1显示了过采样系统中的情况。从噪声频谱密度看,系统总噪声似乎以增益放大器为主,但一旦考虑带宽,各级贡献的rms噪声其实非常相近。

误区三:手工计算时必须包括每一个噪声源

设计时有人可能忍不住要考虑每一个噪声源,但设计工程师的时间是宝贵的,这样做在大型设计中会非常耗时。全面的噪声计算最好留给仿真软件去做。

不过,设计人员如何简化设计过程需要的手工噪声计算呢?答案是忽略低于某一阈值的不重要噪声源。如果一个噪声源是主要噪声源(或任何其他折合到同一点的噪声源)的1/5 erms,其对总噪声的贡献将小于2%,可以合理地予以忽略。设计人员常会争论应当把该阈值选在哪里,但无论是 1/3、1/5还是1/10(分别使总噪声增加5%、2%和0.5%),在设计达到足以进行全面仿真或计算的程度之前,没必要担心低于该阈值的较小噪声源。

模数转换器(ADC)数据手册可能建议利用噪声为ADC 1/10左右的低噪声ADC驱动放大器来驱动模拟输入。但是,这并非总是最佳选择。在一个系统中,从系统角度权衡ADC驱动器噪声常常是值得的。

首先,如果系统中ADC驱动器之前的噪声源远大于ADC驱动器噪声,那么选择超低噪声ADC驱动器不会给系统带来任何好处。换言之,ADC驱动器应与系统其余部分相称。

其次,即使在只有一个ADC和一个驱动放大器的简单情况下,权衡噪声并确定其对系统的影响仍是有利的。通过具体数值可以更清楚地了解其中的理由。

考虑一个系统采用16位ADC,其SNR值相当于100 µV rms噪声,用作ADC驱动器的放大器具有µV rms噪声。按和方根加总这些噪声源,得到总噪声为100.5 rms,非常接近ADC单独的噪声。可以考虑下面两个让放大器ADC更为平衡的方案,以及它们对系统性能的影响:

如果用类似的18位ADC代替16位ADC,前者的额定SNR相当于40 µV rms噪声,则总噪声变为41 µV rms。

或者,如果保留16位ADC,但用更低功耗的放大器代替上述驱动器,该放大器贡献30 µV rms噪声,则噪声变为104 µV rms。

就系统性能而言,以上两种方案可能是比原始组合更好的选择。关键是要权衡利弊以及其对系统整体的影响。

误区五:直流耦合电路中必须始终考虑1/f噪声

1/f噪声对超低频率电路是一大威胁,然而,许多直流电路的噪声是以白噪声源为主,1/f噪声对总噪声无贡献,因而不用计算1/f噪声。

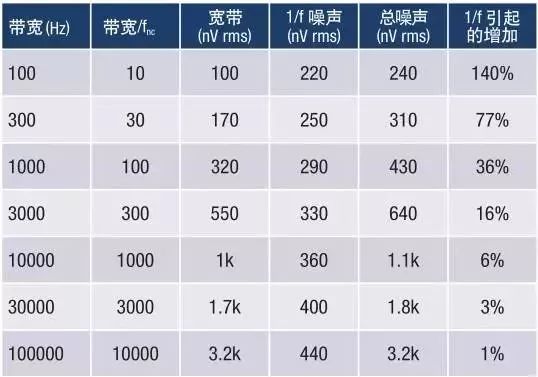

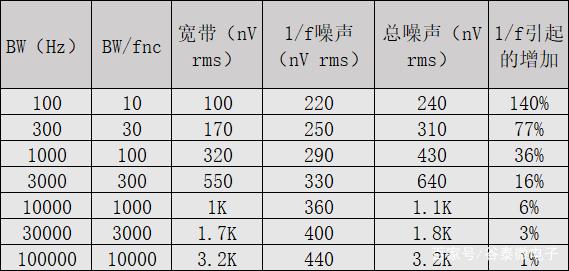

为了弄清这种效应,以一个放大器(其1/f噪声转折频率fnc为10 Hz)为例。对于各种带宽,计算10秒采集时间内包含和不含1/f噪声两种情况下的电路噪声,以确定不考虑1/f噪声的影响。其中宽带噪声为:

当带宽为fnc的100倍时,宽带噪声开始占主导地位;

当带宽超过fnc的1000倍时,1/f噪声微不足道。

现代双极性放大器可以具有比10 Hz低很多的噪声转折频率,零漂移放大器则几乎完全消除了1/f噪声。

图2:1/f 噪声影响与电路带宽的关系示例

误区六:因为1/f噪声随着频率降低而提高,所以直流电路具有无限大噪声

虽然直流对电路分析是一个有用的概念,但真实情况是,如果认为直流是工作在0 Hz,那么实际上并不存在这样的事情。随着频率越来越低,趋近0 Hz,周期会越来越长,趋近无限大。这意味着存在一个可以观测的最低频率,哪怕电路在理论上是直流响应。该最低频率取决于采集时长或孔径时间,也就是观测器件输出的时长。如果一名工程师开启器件并观测输出100秒,则其能够观测到的最低频率伪像将是0.01 Hz。这还意味着,此时可以观测到的最低频率噪声也是0.01 Hz。

现在通过一个数值例子来展开说明,考虑一个DC至1 kHz电路,连续监控其输出。如果在前100秒观测到电路中一定量的1/f噪声,从0.01 Hz至1 kHz(5个十倍频程的频率),则在30年(约1nHz,12个十倍频程)中观测到的噪声量可计算为:

或者说比前100秒观测到的噪声多55%。这种增加几乎没有任何意义,即使考虑最差情况——1/f噪声持续增加到1 nHz(目前尚无测量证据)——也是如此。

理论上,如果没有明确定义孔径时间,1/f噪声可以计算到一个等于电路寿命倒数的频率。实践中,电路在如此长时间内的偏差以老化效应和长期漂移为主,而不是1/f噪声。许多工程师为直流电路的噪声计算设定0.01或1 mHz之类的最低频率,以使计算切合实际。

-

噪声

+关注

关注

13文章

1130浏览量

47601 -

模拟设计

+关注

关注

1文章

55浏览量

18510

原文标题:模拟设计中噪声分析的11个误区(一)

文章出处:【微信号:Mouser-Community,微信公众号:贸泽电子设计圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

模拟设计中噪声分析误区

模拟噪声分析容易陷入哪些误区?

模拟设计中的噪声误区

详细解析关于模拟设计中噪声分析的11个的容易错误的地方。

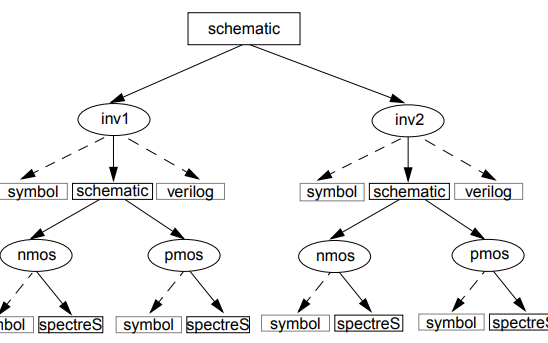

Cadence教程之如何使用VieloSo模拟设计环境进行设计

模拟噪声分析经常会出现那些误区

模拟设计中噪声分析的11个误区资料下载

模拟设计中噪声分析的误区及注意事项

模拟设计中噪声分析的误区

模拟设计中噪声分析的6大误区

模拟设计中噪声分析的6大误区

评论