概念:

Power/Ground Gating是集成电路中通过关掉那些不使用的模块的电源或者地来降低电路漏电功耗的低功耗设计方法。该方法能降低电路在空闲状态下的静态功耗,还能测试Iddq。

理论:

在电路中的某些模块进入休眠或者空闲模式时,我们可以使用之前讲过的Clock Gating技术来降低它们的动态功耗,但是无法降低它们的静态功耗。而Power/Ground Gating技术可以在它们休眠的时候完全关掉它们的电源从而消除它们的静态功耗。

理想情况下,Power gating可以完全消除电路的静态功耗,可实际电路中Power gating只能完全关掉dynamic的power消耗,而leakage却只会减少,不会消失,因为power gating技术仍需要加入一些Always On的Cell(比如switching cell、isolate cell和retention cell,它们都是一直开启的,它们的电源不能被关断,会带来leakage)。

如下图所示为采用了Power gating的电路动态功耗与静态功耗在active模式以及sleep模式下功耗的变化曲线。

Power gating中用到的几种Cell

接下来将对几种Cell分别介绍。

由于内容非常多,非常详细,所以本推文先介绍第一个--Power Switching Cell。

Power Switching Cell

Power Gating或者Ground Gating相应Switching Cell的选取:

Power Gating -> Header -> PMOS

Ground Gating -> Footer -> NMOS

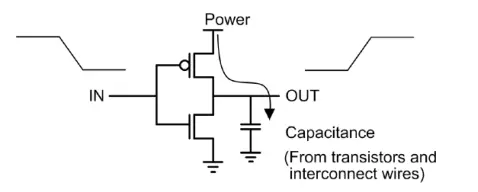

由于Power Switching Cell是Always On Cell,因此为了降低它上面的功耗,一般采用高阈值MOS管实现。下面的图中MOS管上面黑线加粗表示高阈值器件。

下面给出两种方案各自的特点,优缺点以及两种门控方案在SLEEP模式下哪种功耗更低。

下图是Power Gating方案:

特点:

用PMOS实现的Header,用来控制电源的接通与否。

优点:

比Footer实现的Ground Gating功耗更低,因为Header下方的PMOS(在实际电路中会有很多)体端接Virtual VDD,在SLEEP模式下约为0V,不存在PN节反偏注入电流。

缺点:

PMOS驱动能力弱,与Footer相比需要占用更大的面积。

注意:该缺点在先进工艺下已经不存在,由于锗硅工艺的引入,PMOS可能比NMOS驱动还要强一些。由于该缺点已经不存在,因此先进工艺下更多采用Header,也就是Power Gating。

Ground Gating方案:

特点:

用NMOS实现的Footer,用来控制GND的接通与否。

优点:

在之前的老工艺中,相同尺寸的NMOS驱动能力比PMOS要强,因此与Header相比采用Footer的Ground Gating更省面积。

但是在先进工艺中,该优点也逐渐丧失了,原因前面已经解释过了。

缺点:

在SLEEP模式下,漏电功耗比较大。

因为如下:Footer上方的NMOS(在实际电路中会有很多)体端是P衬底,在单阱工艺下只能接GND,在SLEEP模式下NMOS源漏两端的电位都差不多是VDD,此时NMOS存在很大的PN节反偏注入电流。

Power Switching Cell的启动与关闭

Power Switching Cell的个数、分布以及启动、关闭上都有讲究。

这对IR-drop、Timing、漏电流、启动及关闭的速度等都有影响。

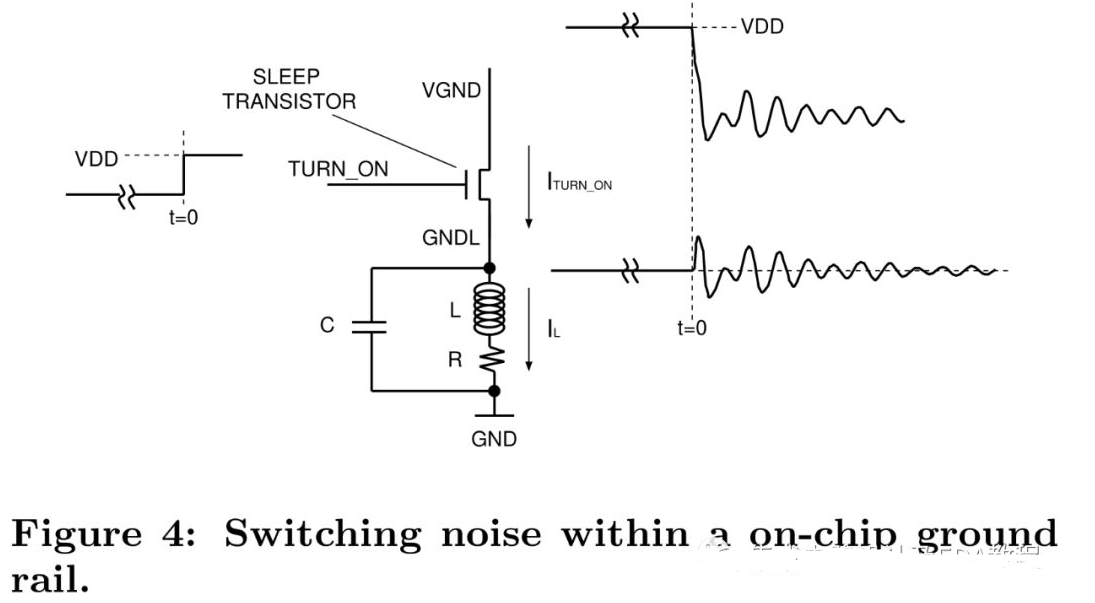

另外,所有的Header或者Footer也不能同时一起打开或者关闭,因为这样在电源或者地上会有很大的开关噪声,如下图所示:

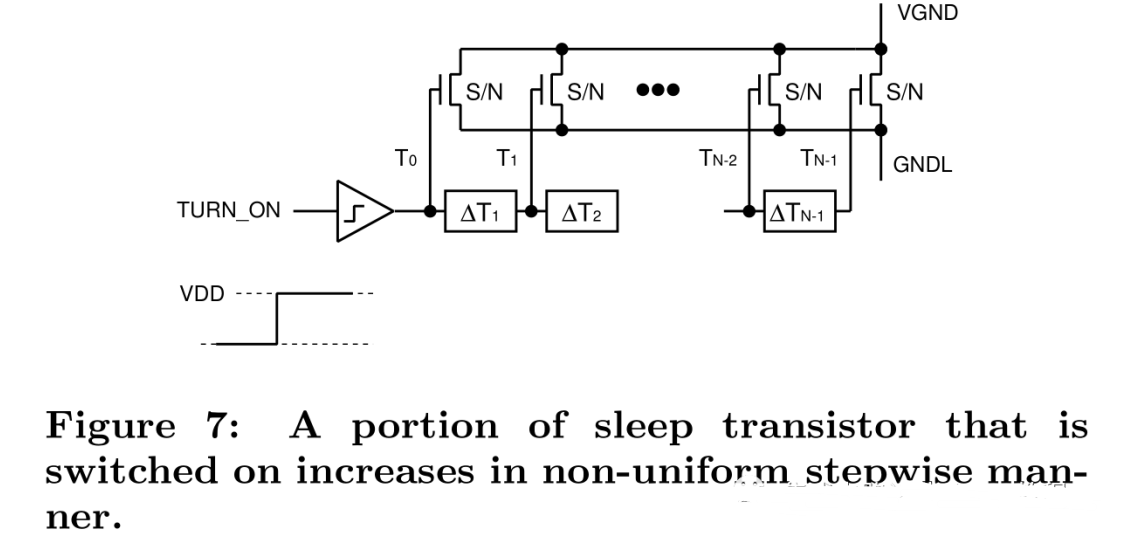

为了避免这种现象,目前的集成电路设计中广泛采用如下图所示的Daisy Chain结构,多个Footer或者Header之间插入Buffer,每隔一段时间开启/关闭一组,再隔一段时间开启/关闭另外一组……直到最后所有的Switching Cell开启/关闭为止。

Power Switching Cell的种类与分布

前面我们根据Power或者Ground Gating来将Switching Cell分为两种:Header和Footer。

另外,我们还可以根据Switching Cell控制Cell的形式将它分为两种:Coarse Grain Power Switch Cell和Fine Grain Power Switch Cell。

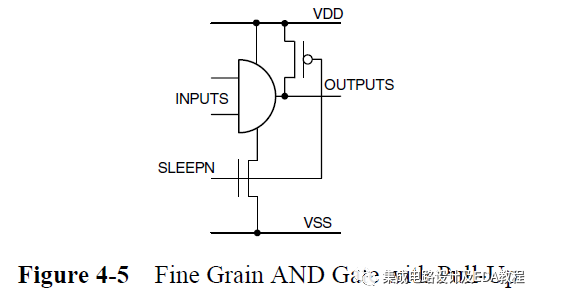

后者是专门在一些逻辑单元内设计的电源控制逻辑,控制简单,但是面积比较大,如下图所示:

而前者是分立的Switching Cell,可以在版图中控制它们的分布,设计复杂度大一点,但是面积开销比较小,现在广泛采用这种形式。

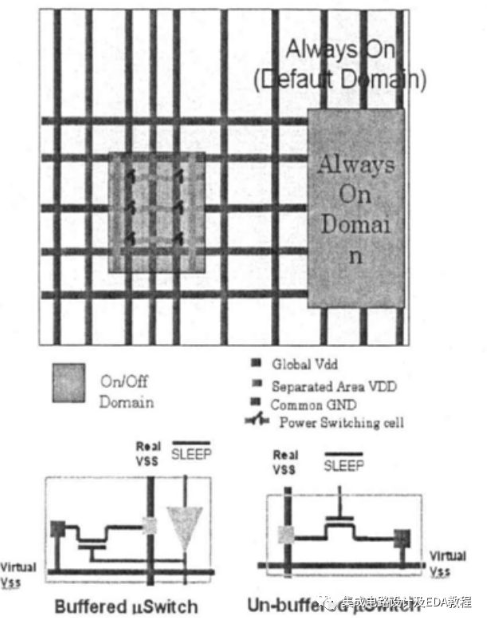

根据前面讲述的内容,Power Switching Cell在物理版图中的分布有一定的要求。

有列状分布:

还有环状分布:

考虑到前面讲的Daisy Chain结构以及IR-drop等因素,目前广泛采用列状排布。

Power Switching Cell的lib描述

前面讲到,Power Switching Cell有两种,分别为Coarse Grain Power Switch Cell和Fine Grain Power Switch Cell。

下面是一个Coarse Grain Power Switch Cell的Liberty格式描述:

library(《coarse_grain_library_name》) { #library 描述开始

…

lu_table _template ( template_name ) #电压状态template描述,dc_current组中会使用

variable_1 : input_voltage;

variable_2 : output_voltage;

index_1 ( 《float》, … );

index_2 ( 《float》, … );

}

…

cell(《cell_name》) { #某个Power Switching Cell描述开始

switch_cell_type : coarse_grain; #Switching Cell类型是coarse_grain,暂时只支持该类型

…

pg_pin ( 《VDD/VSS pin name》 ) { #声明电源和地的pg_pin格式

pg_type : primary_power | primary_ground; #他们是主电源和主地

direction : input ; #方向是输入

…

}

/* Virtual power and ground pins use “switch_function” to describe the logic to

shut off the attached design partition */

pg_pin ( 《virtual VDD/VSS pin name》) { #声明内部电源和地,这就是输出电源/地的端口

pg_type : internal_power | internal_ground;

direction: output; #方向是输出

…

switch_function : “《function_string》”; #定义开断控制功能,例如SLEEP

pg_function : “《function_string》”; #内部电源或地功能与输入的pg_pin一致,对于header switch来说就是premary_power的Pin Name,对于Footer Switch来说就是primary_ground的Pin Name

}

dc_current ( 《dc_current_name》 ) { #定义不同条件下输出Pin的稳定电流值,EDA工具利用该数据计算IR Drop,并进行Switch的优化。

related_switch_pin : 《input_pin_name》; #定义控制开断的Pin

related_pg_pin : 《VDD pin name》; #定义可以被控制开断的电源Pin,如果是Footer Switch则是地Pin

related_internal_pg_pin : 《Virtual VDD》; #定义不会被关闭的内部电源Pin,Footer Switch则是地Pin

values(”《float》, …”); #定义不同状态下的该Cell输出的电流值

}

pin (SLEEP) { #Pin SLEEP定义开始,SLEEP只是举例

direction : input;

switch_pin : true; #表示该输入Pin是switch pin,控制电源/地的开断

…

/* The acknowledge output pin uses “function” to represent the propagated switching signal

*/

pin(《acknowledge_output_pin_name》) { #定义应答输出Pin开始,完成开断后,与switch pin状态一致,有的Switch Cell可能没有该pin

…

function : “《function_string》”; #功能定义,应该与SLEEP状态一致

power_down_function : “function_string”; #定义关断后电源状态,如对于Header switch来说可以是!VDD+VSS,而Footer Switch来说可以是!VSS+VDD

direction : output;

…

} /* end pin group */

} /* end cell group */

Fine Grain Power Switch Cell的Liberty格式描述:

cell(《cell_name》) { #Fine Grain Power Switch Cell都是某个Cell内的一部分,不单独出现

is_macro_cell : true; #定义是不是macro cell

switch_cell_type : coarse_grain | fine_grain; #多数设置为fine_grain

pg_pin ( 《power/ground pin name》 ) { #定义电源信号,primary_是可以断开的,backup_是不会断开的。

pg_type : primary_power | primary_ground | backup_power | backup_ground;

direction: input | inout | output;

…

}

/* This is a special pg pin that uses “switch_function” to describe the logic to shut

off the attached design partition */

pg_pin ( 《internal power/ground pin name》) { #定义内部电源/地

direction: internal | input | output | inout;

pg_type : internal_power | internal_ground;

switch_function : “《function_string》”;

pg_function : “《function_string》”;

…

}

pin (《input_pin_name》) {

direction : input | inout;

switch_pin : true | false; #如果是switch pin就是true

…

}

…

pin(《output_pin_name》) {s

direction : output | inout;

power_down_function : 《function_string》;

…

} /* end pin group */

} /* end cell group */

-

集成电路

+关注

关注

5387文章

11519浏览量

361555 -

静态功耗

+关注

关注

0文章

17浏览量

8941 -

PMOS

+关注

关注

4文章

245浏览量

29546 -

低功耗设计

+关注

关注

0文章

80浏览量

16157

发布评论请先 登录

相关推荐

如何实现EEPROM的低功耗模式

低功耗SOC芯片的优势

物联网系统中TCP低功耗产品长连接状态下降低功耗功能的实现方案

栅极驱动芯片选型低功耗原因

一款4644芯片低功耗设计思路解析

OPA454如何降低功耗?

有没有降低ESp8266功耗的方法?

国产蓝牙模组 | 低功耗蓝牙应用

上拉电阻如何实现低功耗设计

OTP低功耗语音芯片的工作原理与产品特性

stm32g070怎么调试才能降低功耗?

如何降低LoRa模块的功耗以延长电池寿命?

低功耗蓝牙技术的特点 低功耗蓝牙如何实现低功耗?

低功耗设计的几个误区分享

一文读懂低功耗蓝牙的应用

降低电路漏电功耗的低功耗设计方法

降低电路漏电功耗的低功耗设计方法

评论