3D NAND闪存高密度技术正变得越来越激进。3D NAND闪存密度和容量的提高主要通过增加垂直方向上堆叠的存储器单元的数量来实现。通过这种三维堆叠技术和多值存储技术(用于在一个存储单元中存储多个比特位的技术),实现了具有极大存储容量的硅芯片。

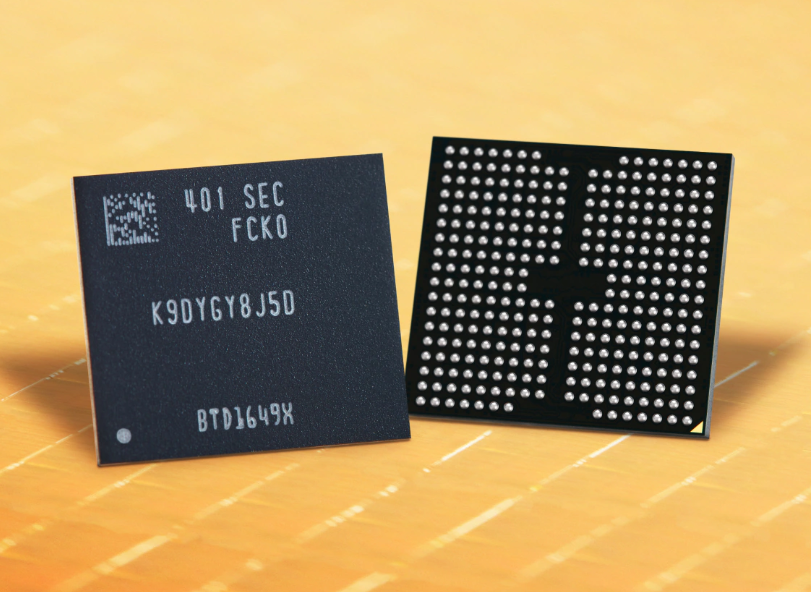

目前,最先进的3D NAND闪存可在单个硅片上容纳高达1Tbit或1.33Tbit的数据。

譬如,英特尔(Intel)和美光科技(Micron)的开发联盟和三星电子各自将制造技术与64层堆栈和QLC(四层单元)技术相结合,该技术将4位数据存储在一个存储单元中。因此,实现了1Tbit存储容量。

东芝存储和西部数据公司(Western Digital)通过将QLC技术与制造技术相结合,堆叠了96层,开发出具有1.33 Tbit的高容量硅芯片。1.33 Tbit是目前世界上最大的半导体存储器存储容量。

还开发了128层堆叠的3D NAND闪存。2019年6月,SK海力士将128层制造技术与TLC(三层单元)技术相结合,将3位数据存储在一个存储单元中,从而实现每个硅片的3D存储容量。采用TLC堆叠方式使得3D闪存具有更高的存储容量。

在过去的20年中,内存容量增加了1,000倍

回顾过去,传统的2D NAND闪存主要通过小型化将其存储容量扩展到128Gbit。MLC技术和TLC技术用于多级存储。

3D NAND闪存技术的实际应用始于128Gbit,256Gbit或更高的存储容量成为3D NAND技术的主导地位。多级存储系统已通过TLC技术和QLC技术投入实际应用。

自2001年以来,NAND闪存的存储密度(每硅片存储容量)一直以每年1.41倍的速度增长。这相当于三年内存储容量增加了四倍。令人惊讶的是,这种高速度持续了19年。

然而,现在人们都在关注3D NAND闪存的未来,半导体存储研发界已经听说过。主要有两个问题。

一个是堆叠层数量的增加来提高容量,这种方式将在不久的未来减缓或达到极限。另一个是多级存储技术将通过QLC方法达到极限,并且每个存储器单元的位数不能增加。

三星正式提到超过300个3D NAND闪存

然而,8月6日,主要的NAND供应商宣布了一系列路线图和技术来克服这些问题。

存储制造商三星电子于6月6日宣布,它将开始批量生产配备256Gbit 3D NAND闪存的SSD,在单个堆栈中有136层内存通孔。136层内存通孔是有史以来最大的层数。除了源极线和伪字线之外,存储器单元串中的字线层的数量似乎是110到120。

值得一提的是,通过堆叠三个136层的单个堆叠,可以堆叠超过300个存储器单元。三星表达如此乐观的看法是很不寻常的。

300层的开发日期尚未公布,但研究已经开始。

堆叠字线数量的路线图

东芝内存已经提到了过去通过存储器通孔技术堆叠字线数量的可能性。2017年5月,IMW表示可以用200层实现2Tbit/die。截至2017年5月,3D NAND闪存技术字线堆栈的最大数量为64。

然而,在2018年8月,闪存行业盛会“闪存峰会(FMS)”中,SK海力士表示200层级是一个传递点,最终可以实现500层级。

2019年8月6日,SK海力士在FMS国际闪存会议上公布了其闪存路线图,预计2020年推出176层的闪存,2025年500层,2030年800+层。800层原则上是可以实现8Tbit/die的层数。单个裸片就是1TB。

图1:SK海力士NAND产品发展路线图

多级存储器最终达到5bit/cell

在当天的FMS会上,让人惊讶的是,东芝存储也宣布了两项基本技术来提高3D NAND闪存的存储密度。

图2:通过东芝存储的QLC(4位/单元)技术分配阈值电压。

一种是多值存储技术。该公司宣布将开发“PLC技术”,将5位数据存储在一个存储单元中。这听起来是一个令在场听众超级震惊的消息。

图3:东芝存储公司推出的PLC(5位/单元)技术的阈值电压分布。

传统的多级存储系统通常是QLC(四级单元)技术,其将4位数据存储在一个存储器单元中。在QLC技术中,在一个存储器单元中写入15级的阈值电压。相邻阈值电压之间的差异很小并且调整非常困难。因此,QLC技术被认为是多级存储的限制。

然而,东芝存储已经打破了这种信念。他们已经展示了当在一个存储器单元中写入31个阈值电压时的实验结果。东芝联合开发合作伙伴Western Digital也展示了一个包含5位/单元的多级内存。顺便说一句,将QLC更改为PLC会使内存密度增加25%。

图4:Western Digital的多级存储方法解释幻灯片。

双倍内存密度的终极方法

另一种技术是通过将存储器单元的字线分成两半来将每个存储器通孔的存储器单元数量加倍。尽管很难制造,但存在原则上存储密度加倍的优势。

东芝存储展示了电荷陷阱(CT)单元和浮栅(FG)单元的横截面观察图像,其中字线被分成两半。

图5:通过将存储器单元字线分成两半来将存储器密度加倍。左边是概念。右边是原型单元结构和横截面观察图像。

3D NAND闪存主要供应商开发的意愿似乎根本没有削弱。毫无疑问,超高层,多值存储和存储器单元划分是极其困难的技术。不过,可以说这个行业别无选择,只能去做。

-

存储

+关注

关注

13文章

4367浏览量

86259 -

内存

+关注

关注

8文章

3071浏览量

74414 -

3D NAND闪存

+关注

关注

0文章

5浏览量

4751

发布评论请先 登录

相关推荐

预期提前,铠侠再次加速,3D NAND准备冲击1000层

腾讯混元3D AI创作引擎正式发布

光学系统的3D可视化

3D打印技术,推动手板打样从概念到成品的高效转化

【半导体存储】关于NAND Flash的一些小知识

裸眼3D笔记本电脑——先进的光场裸眼3D技术

铠侠瞄准2027年:挑战1000层堆叠的3D NAND闪存新高度

SK海力士5层堆叠3D DRAM制造良率已达56.1%

三星已成功开发16层3D DRAM芯片

3D NAND闪存来到290层,400层+不远了

3D NAND开发竞争加剧 “5bit/cell”技术也出现了

3D NAND开发竞争加剧 “5bit/cell”技术也出现了

评论