随着系统设计公司应对当今经济环境的考验,他们面临着寻找提高产品开发和制造流程效率的双重挑战,同时管理这些产品日益复杂的问题。这些业务因素促使人们需要更高效地在印刷电路板(PCB)上实现高密度,高引脚数的FPGA,ASIC和IC以及新的工作流程方法,使公司能够满足上市时间和设计性能目标当我们考虑FPGA密度和性能的最新进展推动FPGA设计开始呈指数式增长时,对更高效流程的需求尤为重要。 FPGA正在越来越多的应用中出现,推动了对FPGA和PCB设计工具集成的需求。

例如,PCB可能包含多个高引脚数(1,500至2,000)FPGA,这些FPGA与PCB同时设计,以满足积极的上市时间目标。 FPGA封装中的引脚输出变化必须不断反映到PCB原理图和布局设计数据库中。用于PCB的高速信号完整性分析工具必须能够访问I/O驱动器和接收器的验证模型。为完成或满足高速时序而布线PCB可能还需要对FPGA进行引脚输出更改。

这种双轨设计过程的一个主要例子是为单个PCB设计多个FPGA。 FPGA的设计可能包括EDA供应商和FPGA供应商提供的工具。 PCB的设计将包括来自EDA供应商的工具,不一定与FPGA工具供应商相同。

第一个问题是简单地将FPGA布局布线工具的结果反映到原理图和PCB布局工具中。对于1,500+引脚FPGA,如果手动完成,此过程可能需要一周时间。大型FPGA需要一个过程,在该过程中,符号在功能上被分解(断裂),以便适合甚至最大的原理图表。随着FPGA设计过程的继续,引脚输出发生变化(通常为4-6次),如果没有完全自动化的FPGA工具到PCB原理图符号和几何过程,设计时间表将会丢失。

不幸的是, FPGA的设计不仅仅在FPGA设计者的控制之下。当FPGA放置并布线在PCB上时,互连网络的定时和延迟调整可能需要更改FPGA的引脚分配。利用可了解FPGA引脚交换和驱动器规则的PCB设计系统,可以在PCB环境中进行这些引脚更改,然后自动反射回FPGA工具。如果PCB工具没有FPGA规则,这可能会成为一个非常迭代且耗时的过程。

为了确保正常的性能,必须执行高速验证,其中包括PCB。由于FPGA上现在常见的千兆位速度,FPGA供应商提供的设计套件必须包含准确的IBIS,Spice或VHDL-AMS模型。利用这些模型和可在GHz范围内进行分析的PCB验证工具,可以验证设计的信号完整性和性能。

底线是电子公司需要紧密,双向集成FPGA工具及其PCB设计工具以及EDA和FPGA供应商之间的密切合作。通过这种整合与合作,可以实现上市时间和性能目标。如果没有它,系统设计的日益复杂化将使这一过程停滞不前,并最终限制或消除电子公司的利润。

-

FPGA

+关注

关注

1629文章

21750浏览量

604073 -

pcb

+关注

关注

4320文章

23113浏览量

398386 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43080

发布评论请先 登录

相关推荐

Verilog vhdl fpga

IOy系列BACnet/IP远程IO模块如何与智能楼宇系统进行集成和协同工作?

浅谈如何克服FPGA I/O引脚分配挑战

# FPGA 编程如何工作?

从无到有,PCB工厂的神奇设备之旅!

FPGA输入的时钟信号必须是方波么?正弦波会有影响么?

不同工作环境温度对电感性能有何影响?

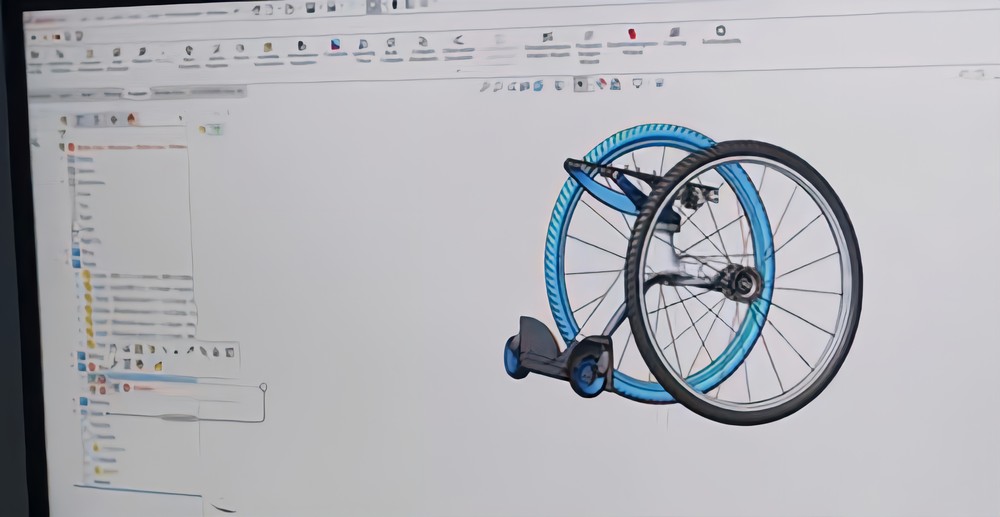

SOLIDWORKS 2024:智能工作、协同工作

FPGA,PCB工具为什么必须协同工作

FPGA,PCB工具为什么必须协同工作

评论