编者注:以下内容源于Lee Ritchey撰写的第一次正确的高速PCB和系统设计实用手册第38章。该书由Ritchey的培训和咨询公司Speeding Edge出版。

本章介绍封装寄生电感对高速逻辑电路性能的影响。具体地说,在这种情况下涉及的封装寄生是进出IC封装的电源路径中的不需要的电感。随着逻辑速度的提高以及数据和地址总线变得越来越宽,这些切换事件中涉及的电流瞬变所产生的噪声尖峰已经成为失败的主要原因。

Vcc和接地反弹是IC芯片上Vcc和接地导轨相对于PCB平面上各自电平的变化。这种类型的不需要的瞬态通常是单端逻辑驱动器对传输线充电和放电的结果。图38.1说明了创建Vcc和接地反弹的方式。

图38.1 ??显示Vcc和接地反弹的典型单端传输线

图38.1的左侧显示了为传输线的寄生电容充电所需的电流的电流路径以及负载的寄生电容。传输线从逻辑0切换到1.图38.1的右侧显示了当逻辑线从逻辑1切换到0时与寄生电容放电相关的电流路径。这些瞬态电流是同步开关噪声(SSN)。图中所示的电感包括将IC电源引线连接到电源层的过孔电感。

请注意,IC芯片的Vcc端子相对于PCB电源上的Vcc驱动为负极在逻辑0到1转换期间的平面。 IC的所有端子同时被驱动为负(这是Vcc反弹)。结果是,所有静音输出和输入都会出现此电压尖峰。如果尖峰足够大,则可能导致逻辑故障。在从逻辑1到0的转换期间,IC的接地轨在PCB电源平面上相对于地驱动为正(这是接地反弹)。这个尖峰也出现在所有线路上,并且可能导致逻辑故障。

公式38.1可用于计算由逻辑状态变化引起的电压瞬变幅度。

公式38.1 ??用于计算电感器间电压降的公式

其中:VL =电感器两端的电压降,L是Henrys电感器的电感,di =电流变化幅度,单位为安培, dt =进行当前更改所需的时间。

请注意,只有当通过它们的电流发生变化时,或者更准确地说,当通过它们的电磁场发生变化时,电感才会出现电压降。

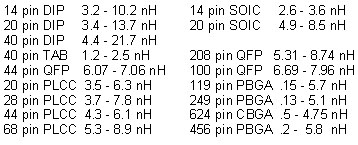

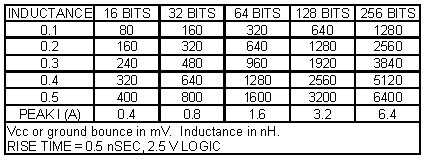

表38.1列出了某些典型IC的引线电感包。电感广泛传播的原因是大多数封装中的引线长度差别很大。

表38.1 ??各种IC封装的典型引线电感

为了了解常见IC封装中可能出现的Vcc和接地反弹幅度,可以进行简单的计算。例如,将使用20引脚DIP(双列直插封装)。该封装上的电源引脚位于拐角处,每个电源引脚的电感为13.7纳亨。在这种情况下,ΔI是当逻辑状态从0变为1时,单个输出为50 mA,而5V HCMOS部件的增量时间为2 ns。使用等式38.1中的这些值导致电压尖峰为342 mV。

想象一下当总线的所有8位同时从0变为1时会发生什么。电压尖峰为2.74伏。接下来,上升时间变为1 ns。峰值为5.48伏。正是这种切换瞬态驱动了从DIP到PLCC封装的变化。试图提高逻辑速度,同时保留在经过验证的真实包中的公司发现他们的产品无法正常工作。应该注意的是,这个问题与封装有关,并且不能通过在PCB上采取的动作来解决。

Vcc和接地反弹(SSN)是由IC封装的电源路径中的电感过大引起的。不能对PCB采取任何措施来解决此问题。更换为具有较低封装引线电感的IC封装是必要的。

以上讨论也适用于业界常用的QFP封装。电感不如DIP封装高。但是,数据总线的宽度比8位宽得多。 SSN的失败表现为偶尔的失败。原因是当所有数据位从一个逻辑状态同时改变到另一个逻辑状态时,发生最坏情况的噪声尖峰。这在2 n 次中仅发生一次,其中N是总线中的数据位数。目前处于制造或设计阶段的许多“片状”系统都没有从这个原因中解脱出来。

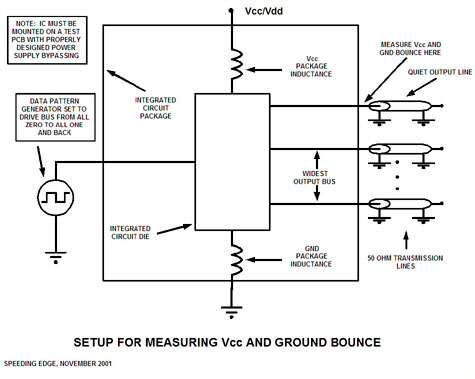

如果不了解这种现象在起作用,就会导致设计永远不稳定。由于这种潜在的故障机制,在使用之前必须检查每个被认为是单端逻辑总线驱动器的部件,以确保SSN不会导致故障。图38.2说明了用于测量最坏情况SSN的测试设置。

图38.2 ??用于测量最坏情况Vcc和接地反弹的测试设置

为了测量最坏情况Vcc和接地反弹,有必要用最逼真的方法加载最宽总线的所有输出可以同时切换的负载集。通常通过在每个输出端连接一个大电容(例如60 pF)来测试IC输出,并观察上升和下降时间。这不是一个现实的负载。它使输出“过载”并导致上升或下降时间比输出驱动传输线时实际发生的时间慢。此外,电容器充电或放电所需的电流尖峰比实际使用中的电流尖峰大得多。实际负载是50欧姆的传输线,因为这是通常预期驱动的部件。

在图38.2中,所有输出都“加载”了50欧姆的传输线。测量探头连接到一个输出,该输出由与将要切换的数据线相同的内部电源和接地总线供电。 IC安装在具有电源平面结构的PCB上,该电源平面结构能够提供将所有数据线从0切换到1所需的充电电流,而不会下垂。

为了观察Vcc反弹,IC采用信号模式驱动,使所有数据线同时从0切换到1。在发生这种情况时,与此事件相关的Vcc弹跳将出现在安静的线路上,几乎没有衰减。 Vcc反弹波形来自该电流波形的上升沿。

为了观察接地反弹,IC采用信号模式驱动,使所有数据线同时从1切换到0。在发生这种情况时,与此事件相关的地面反弹将出现在安静的线路上,没有衰减。

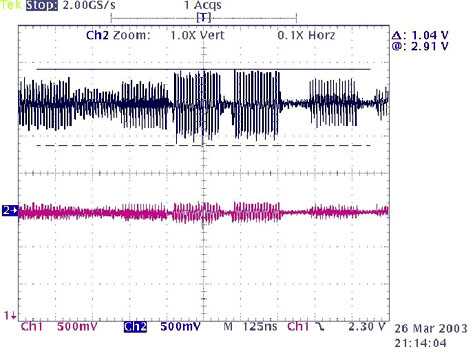

图38.3中的波形以这种方式在实际IC上测量。在这种情况下,被切换的数据总线是64位宽,Vcc是2.5伏。顶部曲线是Vcc和地面反弹的组合。 Vcc以上的偏移是地面反弹,Vcc以下的偏移是Vcc反弹。通过将所有数据线从0切换到1然后多次切换1到0来产生这组波形。

请注意,偏移幅度大致相同,为500 mV。由此可以推断,Vcc和接地路径中的电感大约相同。可以粗略地了解这种电感有多大。这可以通过使用公式38.1来实现。

每个输出的峰值电流为2.5V/100欧姆或25 mA。总电流为64 x 25 mA或1.6A。得到的电压为0.5 V.增量时间为2 ns。电感计算为约.625 nH。这种电感是IC封装引线的电感和通向PCB的通孔的组合,用于接入电源和接地层。

从早期的电源讨论来看,已经确定需要电流执行此切换功能是从PCB内置的平面电容中提取的。如果此电容不够大,每次数据线从0切换到1时,Vcc上都会出现纹波。这在图38.1的左上角显示为“v”形倾角。

图38.3中的下部波形是Vcc上的纹波,对应于这些开关事件。在此示例中,设计到PCB中以支持此事件的平面电容为24 nF。产生的纹波约为150 mV。对于2.5V逻辑,这接近可接受的极限。减少这种纹波的唯一方法是重新设计PCB叠层以增加更多的平面电容。分立电容具有太大的电感来解决这个问题。

图38.3 ??具有Vcc噪声的64位数据总线上的实际Vcc和接地反弹

除了设计PCB叠层以产生足够的平面电容以提供开关瞬态外,最小化电感也很重要到达飞机所需的过孔。因此,支持最大数据总线的平面对应该是元件下方的第一个平面对。

图38.3中的波形是此特定设计的上电复位线。每次该数据总线的所有成员从0切换到1时,系统都会经历上电复位周期。这将在内存访问期间发生。结果是一个无法装运的系统,无法通过在PCB上采取任何措施来修复。唯一的补救措施是重新设计IC封装。这种设计通常被称为硅谷墓碑。

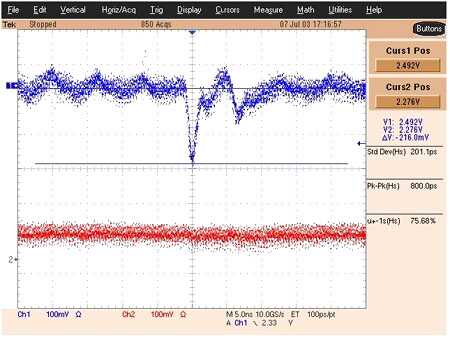

图38.4 ??具有Vcc噪声的80位数据总线上的实际Vcc反弹

图38.4是来自另一个IC的Vcc反弹波形,其中80位数据总线同时从0切换到1。还显示了Vcc上的噪音。应该注意的是,与该切换事件相关的Vcc噪声很小,很难看到。这是因为支持此切换事件的平面电容为140 nF或图38.3中的7倍。

图38.4中的Vcc反弹来自2.5V DDR数据总线。可以使用公式38.1计算引起该噪声的有效电感。在这种情况下,每行的ΔI也是25mA。总Δ增量为2A。 ΔV为216 mV。 ΔT为1.15 ns。由此,等效L为0.497nH。同样,这是封装电感和连接到电源层的过孔电感的组合。

图38.4中的示例具有1.16 ns的相对较慢的上升时间。该示例中的组件能够产生小于0.5ns的上升时间。如果性能频谱快速侧的这些部件中的一个安装在同一电路中,则Vcc反弹将是所示的两倍,即532 mV。这远远超过了该电路的噪声容限。重新设计封装以降低寄生电感是解决此问题的最可靠方法。

如果重新设计IC封装不是一个选择,还有其他可能的解决方案吗?在某些情况下有。噪声问题的根源是许多输出同时切换。有时可以错开输出的时钟,使得只有一部分可以同时切换。这通常称为多相时钟。另一种选择可能是将输出分配到几个Vcc和地线上。这可以通过市场上的一些FPGA实现。

此等式中的一个参数是信号边沿的上升时间。有可能减慢边缘。

当然,最佳解决方案是选择电源和接地导轨中具有极低电感的封装的元件。表38.2显示了各种2.5V宽数据总线为0.5 nSEC边沿产生的Vcc或接地反弹量与电源路径中总电感的函数关系。

表38.2 ?? Vcc和接地反弹与封装电感,2.5V CMOS,0.5 ns边缘

随着边沿变得更快,数据总线变得更宽,IC封装的设计必须非常小心地完成应避免使用Vcc和接地反弹。

在设计中包含供应商无法展示Vcc和地面反弹数的部件是不明智的。

必须检查每个用于驱动宽数据总线的IC,以确保封装电感足够低,以产生可接受的低Vcc和接地反弹。

Vcc和地面反弹已成为主要来源大多数新设计中的间歇性故障。这些故障可追溯到较差的IC封装设计。

如何确定新IC在包装之前的Vcc和接地反弹

通常,有必要选择仍在开发中的部件。没有真正要衡量的部分。可以在Spice建模软件包中对I/O和封装进行建模,并计算预期的Vcc和地面反弹。这是通过获得输出驱动器的Spice模型,将其与封装电源和接地路径的预测电感相结合,驱动适当阻抗的传输线并以最终电路中预期的最快上升和下降时间切换输出来完成的。 。

设计不良的BGA封装示例

通常,BGA封装具有比其他封装类型更好的Vcc和接地电感,例如QFP,PLCC和DIP。但是,情况并非如此。一些BGA封装被设计成使得从电源和接地触点到与PCB接触的球的引线或导线。当考虑BGA封装中的新元件时,必须检查封装布局以确保Vcc和接地路径具有低且相等的电感。

图38.5是两个具有此问题的双层BGA封装的照片。在两种情况下,管芯都通过触点安装在腔体中,触点直接穿过封装到BGA背面的球。这些是接地触点,电感非常低。在这两种情况下,Vcc引脚都是从管芯边缘到BGA封装边缘的迹线。痕迹。

图38.5 ??两种在Vcc引线中具有过高电感的BGA封装

确定可接受的Vcc和接地反弹量

通过分析来自其他源的噪声并将其与所使用的逻辑系列的噪声容限进行比较,可以计算出可以容忍的Vcc和接地反弹量。 Vcc和接地反弹可以消耗总噪声容限的一部分。用于执行此分析的方法将在后续章节中介绍。

Lee Ritchey是Speeding Edge的创始人兼总裁,该公司为高科技公司提供私人现场培训课程以及通过UC的课程伯克利的推广计划和行业会议。

-

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43089

发布评论请先 登录

相关推荐

HDMI模块的PCB设计

专业PCB设计,高速PCB设计,PCB设计外包, PCB Layout,PCB Design,PCB画板公司,PCB设计公司,迅安通科技公司介绍

pcb设计中如何设置坐标原点

PCB设计与PCB制板的紧密关系

PCB设计基本原则总结,工程师必看

PCB设计的EMC有哪些注意事项

PCB设计中的常见问题有哪些?

pcb设计

多层pcb设计如何过孔的原理

什么是PCB扇孔,PCB设计中对PCB扇孔有哪些要求

DC电源模块的 PCB设计和布局指南

良好的PCB设计是怎样被破坏的

良好的PCB设计是怎样被破坏的

评论