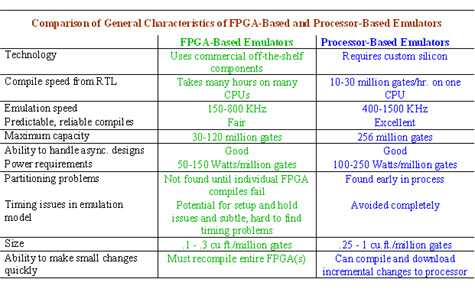

工程师更广泛地理解基于FPGA的仿真,因为工程师习惯于使用FPGA进行设计。对基于处理器的仿真器的理解不太了解,而且有大量错误信息的例子比比皆是。本文将尝试消除解释基于处理器的仿真如何工作以及如何将设计构造映射到其中的谜团,例如三态总线,复杂存储器和异步时钟。

早期基于处理器的仿真

在1990年代早期,IBM开创了基于处理器的仿真技术,这是他们早期工作的一个分支。基于硬件的仿真引擎。硬件技术由大量布尔处理器组成,这些处理器能够以非常高的速度相互共享数据。软件技术包括在许多处理器之间划分设计,并以正确的时间顺序和最佳方式调度各个布尔运算。

最初,性能无法与基于FPGA的仿真器匹配,但编译时间不到一小时,消除了困扰基于FPGA的仿真器的时序问题,使新技术对许多使用模型很有吸引力,特别是模拟加速。该技术的后代最终在仿真速度上超越了FPGA系统,同时保留了编译时间的巨大优势?并且没有一百台PC的农场用于编译。

软件技术的进步扩展了基于处理器的仿真器的应用,以处理具有任意数量时钟的异步设计。其他扩展支持设计中所有信号的100%可见性,从仿真运行开始的任何时间对所有信号的可见性,以及逻辑分析器触发事件的动态设置,无需重新编译。在基于FPGA的系统的仿真速度不断降低的同时,新一代基于处理器的系统不仅以惊人的速度提高了仿真速度,而且还证明了其容量可扩展到数亿个门。

基于处理器的仿真器架构

了解处理器的方式基于仿真器的工作原理,简要回顾一下逻辑仿真器的工作原理很有用。回想一下,计算机的ALU(算术逻辑单元)可以对变量执行基本的布尔运算,例如AND,OR,NOT,并且诸如“always @(posedge Clock)Q = D”之类的语言构造构成了a的基础。拖鞋。

在门(和透明锁存器)的情况下,模拟顺序很重要。信号通过门链示意性地“从左到右”竞争,或者在RTL源代码中“从上到下”。触发器(寄存器)打破门链以进行排序。

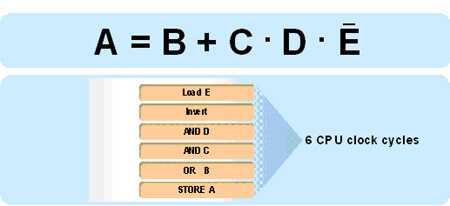

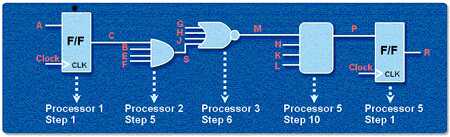

图1 ??逻辑模拟; CPU对信号执行布尔运算,寄存器

一种类型的模拟器,一个分级编译逻辑模拟器,以正确的顺序一次一个地执行布尔方程。 (时间延迟与功能逻辑仿真无关。)如果有两个ALU可用,您可以想象将设计分解为两个独立的逻辑链并将每个链分配给ALU,从而并行化并减少所需的时间,也许是一半。

基于处理器的仿真器具有数万到数十万个ALU,这些ALU可以有效地进行调度,以正确的顺序执行设计中的所有布尔方程。以下系列图纸说明了这一过程。对于此示例,我们假设模拟器中有一个4输入布尔基元。

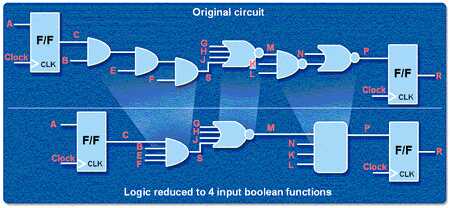

图2 ??步骤1:将布尔逻辑简化为四输入函数

将逻辑简化为四输入函数后的布尔方程组是:

IF(时钟上升) C = A

S = C& B& E& F

M = NOT(G + H + J + S)

P = NOT(N + NOT(M& K& L))

IF(时钟上升)R = P

此外,以下排序约束集适用:

必须首先评估触发器

必须在M之前计算S

M必须在P

之前计算

在计算S之前必须对主输入B,E和F进行采样

在计算M之前必须对主输入G,H和J进行采样

在计算P之前必须对主输入K,L和N进行采样

注意:在触发器之后的任何时间都可以对主输入A进行采样

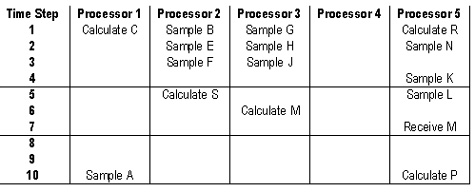

上面显示了一种可能的调度。这是出于说明目的而完成的,并且可能不是最有效的调度。

图3 ??调度逻辑的结果

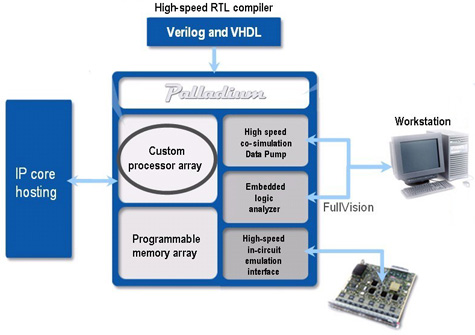

图4 ??基于处理器的仿真器架构

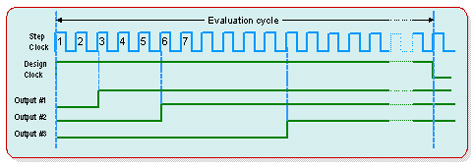

仿真周期包括运行所有处理器步骤以完成设计的完整建模。大型设计通常安排在125? 320步。如果设计可以使用1x时钟(稍后描述),则基于处理器的仿真器的仿真速度将在600KHz和1.5MHz之间。

在每个时间步骤中,每个处理器都能够执行任何4输入逻辑功能,使用任何处理器的任何先前计算结果和任何设计输入或存储器内容作为输入。处理器在集群中物理实现,在集群内快速通信。编译器优化处理器调度以最大化速度和容量。

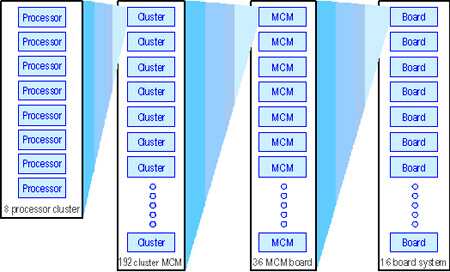

图5 ??处理器阵列架构示例

设计编译

RTL设计的编译完全自动化,并按以下顺序完成:

1)将RTL代码映射到原始单元,例如门和寄存器。

2)合成存储器。

3)展平设计的层次结构。

4)将布尔逻辑(门)减少为4 - 输入功能。

5)通过在最佳位置插入寄存器来中断设计中的异步循环。

6)为目标系统和任何硬IP分配外部连接。

7)设置任何需要的仪表逻辑(例如逻辑分析仪“视觉”)。

8)以统一的方式将所有设计输入和输出分配给处理器。

9)将设计中的每个单元分配给处理器。优先考虑将具有公共输入和/或输出的信元分配给相同的处理器或集群,并为每个处理器分配相同数量的信元。

10)将每个处理器的活动安排为连续的时间步长。目标是最小化最大时间步数。

编译器还必须考虑模拟加速连接,三态总线建模,内存建模,非均匀处理器连接,逻辑分析仪探测和触发等因素。

但编译器无需处理FPGA仿真器中高度可变的FPGA内部时序。因此,基于处理器的仿真编译速度更快,资源更少。尽管执行了布尔优化,编译器仍会维护所有最初指定的RT级网名,以便在调试中使用。这允许用户使用他们熟悉的信号名称进行调试。

三态总线建模

三态总线采用组合逻辑建模。当没有启用任何启用时,用户可以选择“上拉”,“下拉”或“保留状态”。在后一种情况下,当没有启用驱动器时,将锁存器插入设计中以保持总线的状态。在多个使能开启的情况下,对于上拉和保持状态逻辑0将“赢”并且对于下拉逻辑1将获胜。 (注意:这是使用断言的好地方。)

异步循环中断

由于仿真器不对门级硅时序建模,因此异步循环会自动中断编译期间的延迟触发器。编译器将自动中断异步循环而无需用户干预。

但是,通过允许用户指定应该发生循环中断的位置,可以提高性能,因为基于处理器的仿真器的性能与长组合路径的长度有关。通过插入延迟元件来打破错误路径或多时钟周期路径,如果这些路径是设计的关键路径,则可以提高性能。

长组合路径

仿真器的处理器使用特定深度的指令“堆栈”运行,例如160个字。这些是设计计算顺序的时间步骤。

有时,设计中可能会有一个非常长的组合路径,无法将其安排到可用的连续步骤数中。注意,这并不一定意味着逻辑路径具有更多“门级”,因为调度必须考虑许多时间序列约束。

在这种情况下,调度程序将通过使用未使用的处理器时间步骤在第二遍中调度剩余的布尔运算来完成路径。这也可能是因为尝试将太多的门挤入仿真器,但是,作为一个好处,它提供了用户权衡仿真速度与容量的关系。

基于处理器的仿真器中的时钟处理

如前所述,时钟是基于FPGA的仿真器不可靠性的主要来源之一。基于处理器的仿真器完全避免了这个问题,因为它们可以生成设计所需的所有时钟或接受外部生成的时钟。

让仿真器生成所需的所有设计时钟会更方便吗?它运行得更快。您可以指定每个时钟的频率,也可以让编译器从测试平台中提取此信息(如果有的话)。某些基于处理器的仿真器允许您从目标系统向仿真器提供外部时钟。在这种情况下,仿真器将其内部时钟与外部时钟同步。

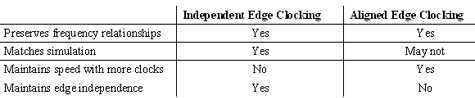

为了提供尽可能高的仿真速度,同时保持所需的异步精度,一些基于处理器的仿真器提供了两种处理异步设计时钟的方法:对齐边和独立边缘。

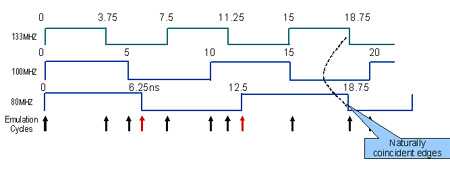

图6 ??时钟示例??三个异步时钟

独立边沿时钟

由于仿真器不对设计时序进行建模,而是功能等效,因此异步时钟边沿之间的精确时序无关紧要。只需要在“现实生活”中不同时的时钟边缘是独立模拟的。

通过独立的边沿时钟,基于处理器的仿真器为每个时钟的每个边沿调度仿真周期,除非边缘与已经调度的边缘自然共同发生。这与事件驱动的模拟器非常相似。

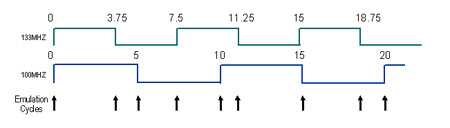

图7 ??两个异步时钟的独立边沿时钟

从两个时钟开始,133 MHz时钟从0到7.5,15.0等的高电平有时(以ns为单位)从高电平转换为高电平。在时间为5,15,25等时,100MHz时钟从低到高从低到高转换为高,低为5,15,25等。注意两者是任意同步的在时间= 0.

仿真周期#1:133 MHz时钟上升,100 MHz时钟上升(两者同时发生)。

仿真周期#2:133 MHz下降(时间= 3.75)。 100 MHz无效。

仿真周期#3:100 MHz下降(时间= 5.00)。 133 MHz无效。

仿真周期#4:133 MHz上升(时间= 7.5)。 100 MHz无效。

仿真周期#5:10 MHz上升(时间= 10)。 133 MHz无效。

仿真周期#6:133 MHz下降(时间= 11.25)。 100 MHz无效。

仿真周期#7:133 MHz上升,100 MHz下降(时间= 15ns ??两次转换)

图8 ??添加具有独立边沿时钟的第三个异步时钟

所以时间表如下:仿真周期#1:133 MHz时钟上升,100 MHz和80 MHz时钟上升(同时发生) 。仿真周期#2:133 MHz下降(时间= 3.75)80 MHz,100 MHz什么都不做。

仿真周期#3:100 MHz下降(时间= 5.00)80 MHz,133 MHz什么也不做。

仿真周期#4:80 MHz下降(时间= 6.25)100 MHz,133 MHz什么也不做。

仿真周期#5:133 MHz上升(时间= 7.5)80 MHz,100 MHz什么都不做。

仿真周期#6:100 MHz上升。 (时间= 10)80 MHz,100 MHz不执行任何操作。

仿真周期#7:133 MHz下降。 (时间= 11.25)80 MHz,100 MHz无效。

仿真周期#8:80 MHz上升。 (时间= 12.5)100 MHz,133 MHz什么都不做。

仿真周期#9:133 MHz上升,100 MHz下降(时间= 15ns ??两次转换)。

对齐边沿时钟

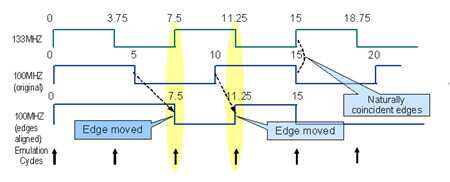

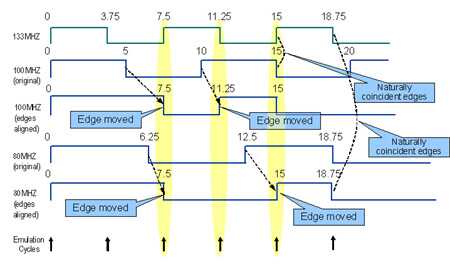

对齐边沿时钟基于以下事实:尽管设计中的许多时钟由于其频率而碰巧具有非重合边缘,但正确的电路操作并不依赖于边缘是独立的。在这种情况下,在保持适当的频率关系的同时,时钟边沿与最高频率时钟对齐,从而减少了所需的仿真周期数,并提高了仿真速度。

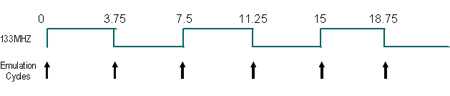

在对齐的边沿时钟中,我们首先为设计中最快时钟的每个边沿调度仿真周期。

图9 ??通过为最快时钟的每个边沿分配仿真周期开始对齐边沿时钟

然后,所有其他时钟相对于此时钟进行调度,较慢的时钟边沿与下一个预定仿真“对齐”周期。请注意,第二个(较慢)时钟没有添加额外的仿真周期。因此保持了仿真速度。另请注意,虽然边沿移动到跟随最快的时钟边沿,但仍保持频率关系,这对于正确的电路操作是必不可少的。

图10 ??添加第二个时钟对齐边缘到最快时钟

图11 ??通过将边缘与最快时钟对齐来添加其他时钟

对齐边缘时钟中的过采样和欠采样

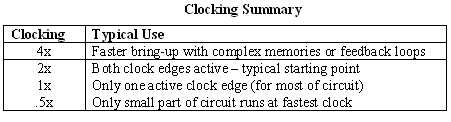

当在最快设计时钟的两个边沿存在仿真周期时,它被称为“2x”时钟(每个最快时钟周期两个仿真周期)。

1x时钟

有时在设计中只有最快设计时钟的一个边沿有效,或者一个边缘占主导地位,而另一个边沿占用最少量的电路。在这种称为“1x时钟”的情况下,每个设计时钟周期的单个仿真周期加倍?还是差不多?仿真速度。所需容量可能略有增加。

如果一个边缘不占优势,那么仍然可以应用这种技术,但所需容量的增加将会显着增加。请注意,只有使用最快时钟的电路和任何大于最快时钟速度一半的时钟才能满足所需容量的增加。

4x时钟?过采样

这可以快速启动包含复杂异步路径的设计。具有读 - 修改 - 写存储器或背靠背锁存器的设计可以通过最初使用4x时钟更快地进行仿真。

有时称为“过采样”,4x时钟为每个活动时钟边沿提供两个仿真周期(或更多)。当存在复杂的异步反馈循环时,这也会有所帮助。基于锁存器的设计可能需要过采样,因为编译器必须在锁存器的两个级别之间插入延迟。如果存在复杂的反馈路径,则可能无法始终将此延迟放在最佳位置。

.5x时钟

这种技术可在某些基于处理器的仿真器上使用,主要用于在最快的设计时钟运行少量逻辑时。在.5x时钟中,两个最快的设计时钟在一个仿真周期中进行仿真。这可以进一步提高仿真速度超过1倍时钟,但有一定的限制:只有最快设计时钟的一个边沿可能有效,此时钟不能有复杂的时钟门控,并且不能有太多的设计逻辑以此速度运行,因为它可以显着增加模拟设计所需的容量。

使用户可以灵活地在对齐边缘时钟或独立边缘之间切换时钟为各种设计风格提供高异步精度和最快的仿真速度。

基于处理器的仿真器中的内存建模

编译器将识别用可综合的Verilog和VHDL RTL代码编写的大多数内存并自动处理它们,包括:

多个读写端口

端口共享最小化面积/延迟

改变读/写依赖性

不同的写使能(边缘与电平灵敏度)

同步和异步样式

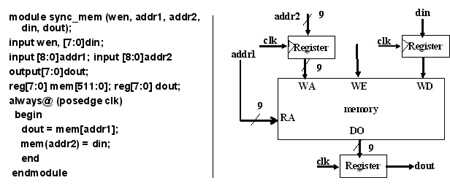

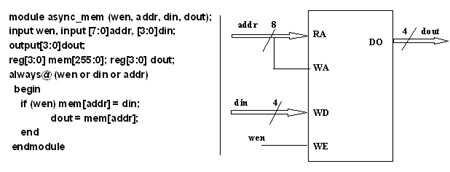

从用户的Verilog代码自动建模的两个存储器示例如下。

图12 ??示例:具有边沿敏感时钟的同步存储器是从用户的Verilog代码自动生成的

图13 ??示例:具有电平敏感写入启用的异步存储器是从用户的Verilog代码自动生成的。

如果必须手动构建异常存储器,用户将在仿真器的原始存储器单元周围写一个“包装器”以提供必要的回应。

在线仿真接口

输出时序控制

当与现实世界接口时有时需要控制输出信号的相对定时。 DRAM存储器接口就是这样一个例子??在断言写入使能之前,所有地址线必须稳定。

由于基于处理器的仿真器调度逻辑操作按顺序发生,因此很容易在仿真周期内对各个(或组)输出信号添加约束,以控制定时到非常相对于其他输出信号的高分辨率。然后,编译器在仿真周期的适当位置调度此输出计算。基于FPGA的仿真器无法实现这一点,因为它们无法控制设计时钟内的时序。

图14 ??基于处理器的仿真器可以高精度调整输出时序

输入时序控制

以类似的方式?并出于类似的原因??输入信号上的定时(“采样”)可由用户控制以满足特定情况。同样,基于处理器的仿真器可以简单地调度特定输入引脚,以便在仿真周期内的其他引脚之前或之后进行采样。使用基于FPGA的仿真器,用户必须通过增加某些信号的延迟来“调整”时序,包括一个大的保护频带,因为基于FPGA的仿真器无法控制不同逻辑路径上的绝对时序。对于基于FPGA的仿真器,这是一个命中注定的命题,可能因编译而异。

摘要结果

硬件加速器和仿真器提供比逻辑仿真器更高的验证性能,但需要额外的部署工作。在线仿真提供了最高的性能,通常比模拟器快10,000到100,000倍,但需要使用速度缓冲设备围绕它构建仿真环境。加速器和仿真器要求用户了解仿真和硅(仿真器和芯片)之间的差异:

仿真有12个或更多状态,硅只有两个状态。

模拟通常按顺序执行RTL语句,硅同时“执行”RTL。

模拟是高度交互的,硅不那么。

基于FPGA的仿真器使用商用FPGA,体积更小,功耗更低,而基于处理器的仿真器需要定制芯片设计并消耗更多功率。另一方面,基于处理器的仿真器在十分之一的工作站上编译设计速度快十倍?分钟与小时。几乎所有设计的仿真速度都更快,平均速度提高了2倍。

两种仿真器都证明了它们在设计中同样能够处理大量异步时钟而不会对性能产生影响。基于处理器的仿真器能够立即探测新信号并改变触发条件而无需缓慢的FPGA编译,这极大地提高了调试的交互性。由于用户大部分时间都在调试,因此基于处理器的仿真器每天可以提供比基于FPGA的仿真器更多的设计周转时间。这样可以缩短新产品的上市时间并提高产品质量。

Ray Turner是Cadence的Incisive Palladium加速器和在线仿真系统的高级产品线经理,该系统是Incisive功能验证平台的一部分。在加入Cadence之前,他曾担任P CAD产品的EDA营销经理7年。总体而言,Ray在EDA产品的产品管理方面拥有18年的经验。他还在电信,航空航天,ATE和微处理器行业拥有14年的硬件,软件和IC设计经验。

-

处理器

+关注

关注

68文章

19292浏览量

229910 -

FPGA

+关注

关注

1629文章

21743浏览量

603555 -

仿真器

+关注

关注

14文章

1018浏览量

83760

发布评论请先 登录

相关推荐

基于FPGA的仿真如何工作

基于FPGA的仿真如何工作

评论