由于LVDS是一种新技术, 因而在使用时LVDS和其他逻辑电路的接口设计就很重要,设计时,应注意以下几个问题:

(1)根据系统的工作电源配置情况和需要传输的数据电平,合理选用驱动器和接收器芯片,或者根据接口芯片的情况,对被传输的数据首先进行电平转换。

(2) 注意阻抗匹配。根据接收器输入端的情况确定是否需要外接100 Ω 电阻,同时要根据PCB的板材和参数合理设计驱动器的线输出阻抗,使其在90~107Ω 范围内。PCB传输线要尽可能地短,因为过长的线路,不但传输衰耗加大,降低了传输速率,而且阻抗也容易失配,并可能影响到信号的完整性。

(3) 根据数据传输速率和传输电缆长度的关系,确定合适的电缆长度以满足系统的要求。一般地采用LVDS方式传输数据,假定负载电阻为100Ω,当双绞线长度为10 m时,传输速率可达400Mb / s;当电缆长度增加为20 m时,速率降为100Mb / s;而当电缆长度为100 m时,速率只能达到10Mb / s左右。

(4)多数LVDS接口芯片的使能端在片内没有接上拉或下拉电阻。如果没有驱动信号输入,它们会不确定地被直接与地或VCC相连,有可能造成逻辑错误,所以除非有特别说明,接口芯片的使能输入端不要悬空。

4. 1 LVDS之间的连接

由于LVDS的芯片内输入端一般含有匹配阻抗,因此LVDS驱动器和LVDS接收器可以用一段连接线直接相连。

4. 2 LVPECL 到LVDS的互连

4. 2. 1 直流耦合

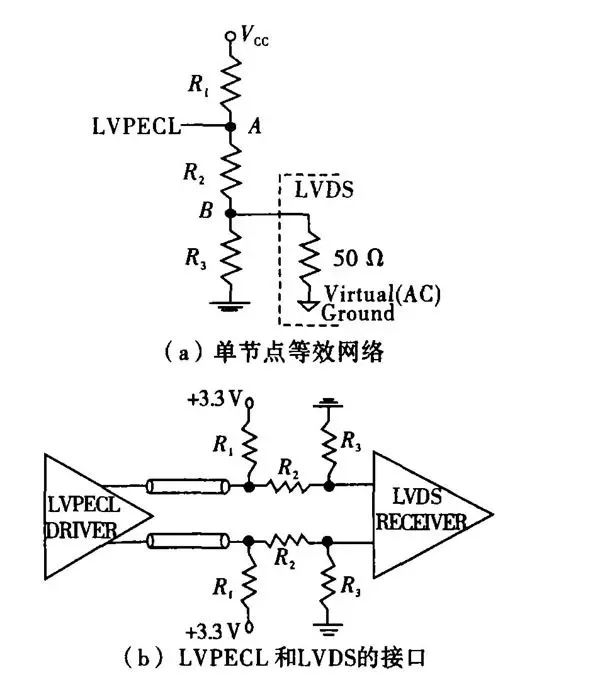

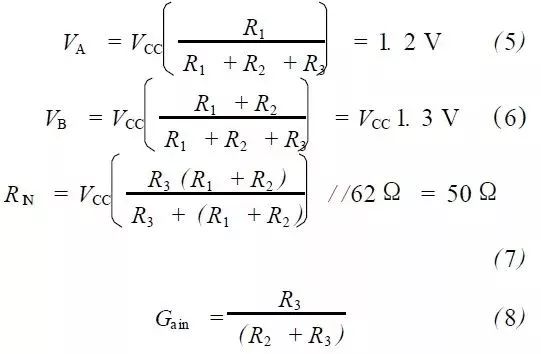

LVDS和LVPECL间的直流耦合要有一个转移网络,如图2所示。首先LVPECL 输出阻抗最佳是50Ω;另外, LVPECL 电路经过衰减网络的输出信号要在LVDS的输入范围内。下面的公式可以得到电阻的值。

图2 LVPECL 和LVDS间的直流耦合

把VCC = 3. 3 V代入(1)式,得R1 = 182Ω, R2= 47. 5Ω, R3 = 47. 5 Ω,另外VA = 1. 13 V, RAC =51. 5Ω, RDC = 62. 4Ω , Gain = 0. 337.若当使用该网络连接LVPECL 的输出端和LVDS的输入端时,那么测量的共模电压VA = 2. 1 V, VB =1. 06 V.假定LVPECL 的差分输出最小是930mV,那么LVDS输入端的最小电压就是313 mV,满足了LVDS 的输入条件。另一方面, 如果LVPECL的差分输出最大是1. 9 V,那么LVDS输入端的最大电压就是640 mV,同样满足LVDS的输入规范。

4. 2. 2 交流耦合

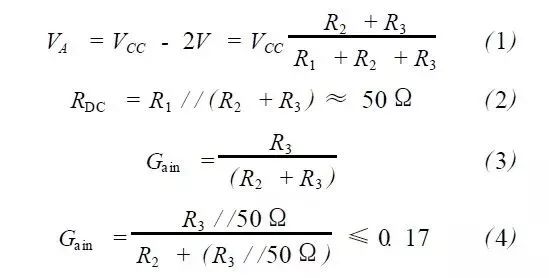

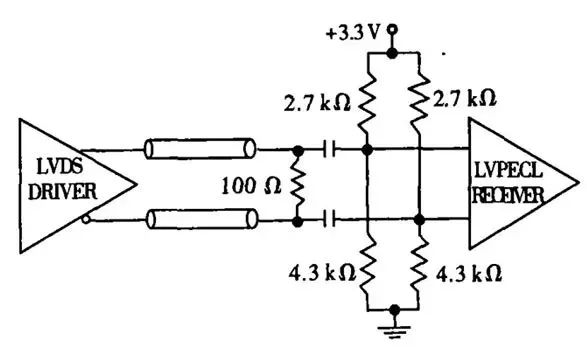

LVPECL 和LVDS间的交流耦合的电路如图3所示。

图3 LVPECL 和LVDS间的交流耦合电路

LVPECL输出通过直流偏置电阻R (142Ω~200Ω )接地。50 Ω 的串联电阻来减弱LVPECL的输出电压来满足LVDS的输入要求。在LVDS输入端每端接1个5. 0 kΩ的电阻到地用来减弱共模电压。

4. 3 LVDS到LVPECL的接口

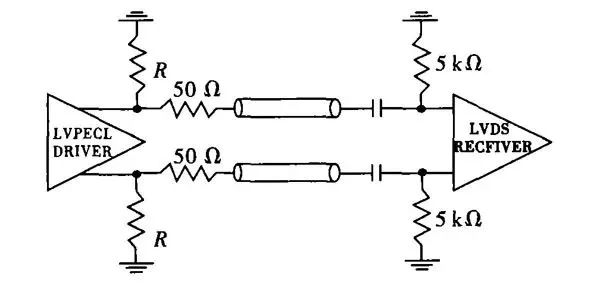

4. 3. 1 直流耦合

直流耦合的电路如图4所示。

图4 LVDS到LVPECL 的直流耦合。

这个电阻网络把LVDS直流输出电压从1. 2V变到LVPECL的输入(VCC - 1. 3 V) .这是因为LVDS的输出电压是参考地,而LVPECL 输入电压参考VCC ,这个网络可以使LVDS的输出不受电压变化的影响;另外考虑的就是功耗和速度的平衡。

如果R1、R2、R3 选择低电阻,那么这个网络的时间常数和LVPECL的寄生参数都很小,能够满足高速的要求;当然由于电阻小了,就有更大的电流流过这些电阻,那么总功耗就大了。这种情况下LVDS的参数可能会受到电压变化的影响。电阻值可以由下列等式求得:

代入VCC = 3. 3 V、R1 = 374Ω、R2 = 249Ω、R3= 402 Ω, 得到VA = 1. 2 V、VB = 2. 0 V、RIN =49Ω, Ga in = 0. 62.LVDS的差分输出的VP - P =500 mV,信号在LVPECL输入端变成310 mVP - P.

电压变化比PECL的输入标准小,但满足LVPECL的输入要求。

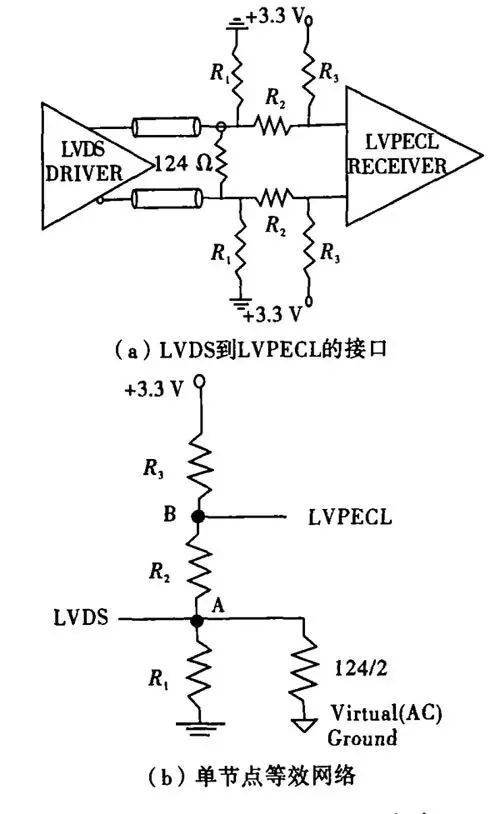

4. 3. 2 交流耦合

LVDS到LVPECL的交流耦合很简单,图5给出了例子,LVPECL的芯片是MAX3867它的片内没有端接电阻。

图5 LVDS到LVPECL的交流耦合。

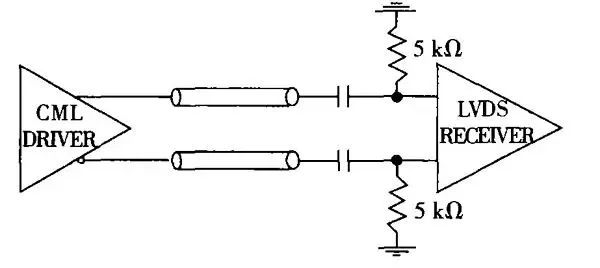

4. 4 CML和LVDS的接口

CML到LVDS的交流耦合如图6所示,要注意的一点就是CML 的输出信号漂移要在LVDS输入信号的要求范围内。

图6 CML到LVDS的交流耦合电路图。

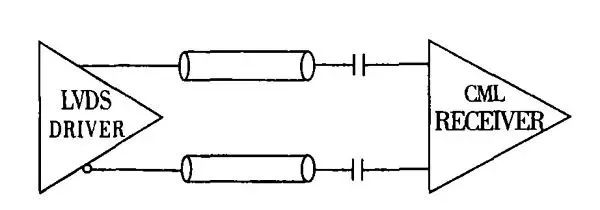

LVDS驱动器连接CML接收器的交流耦合方案如图7所示。

图7 LVDS到CML的交流耦合电路图。

-

逻辑电路

+关注

关注

13文章

503浏览量

44239 -

lvds

+关注

关注

2文章

1241浏览量

70207

原文标题:华为科普5G双模手机,一文看懂华为麒麟810

文章出处:【微信号:eda365wx,微信公众号:EDA365电子论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

逻辑电路芯片-组合逻辑电路芯片-时序逻辑电路芯片

同步时序逻辑电路

异步时序逻辑电路

组合逻辑电路和时序逻辑电路比较_组合逻辑电路和时序逻辑电路有什么区别

LVDS与其他几种逻辑电路的接口设计

LVDS与其他几种逻辑电路的接口设计

评论