很久之前遇到一个问题,就是一块电路板没有全部敷铜,只敷铜了一小部分,但是其它未敷铜的地方还是有GND连接。

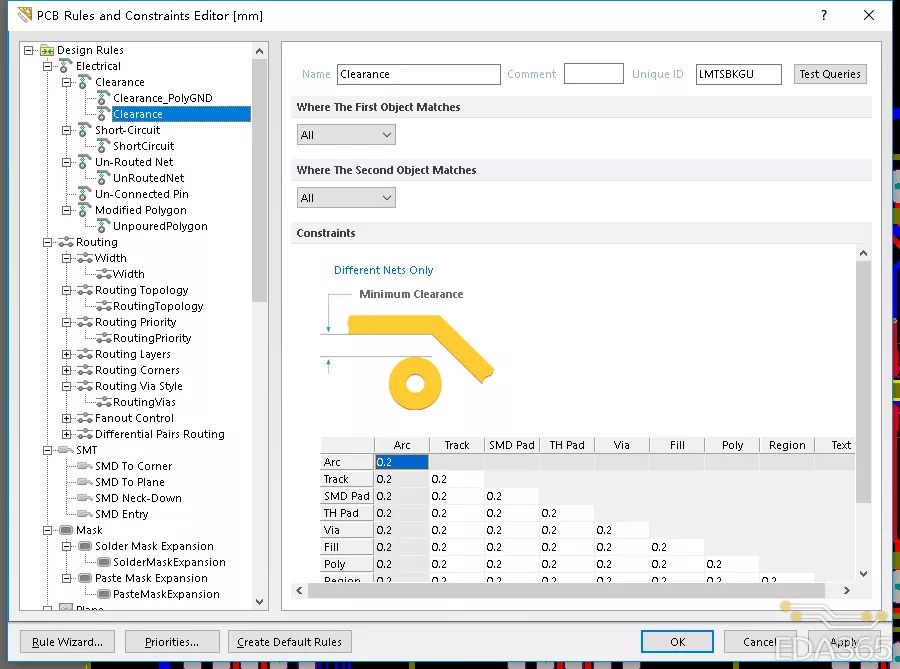

然后我直接用Track将未敷铜的Object连接到GND敷铜上去,但是重新敷铜之后发现敷铜与连线断开了,因为规则规定了Track与Poly的间距:

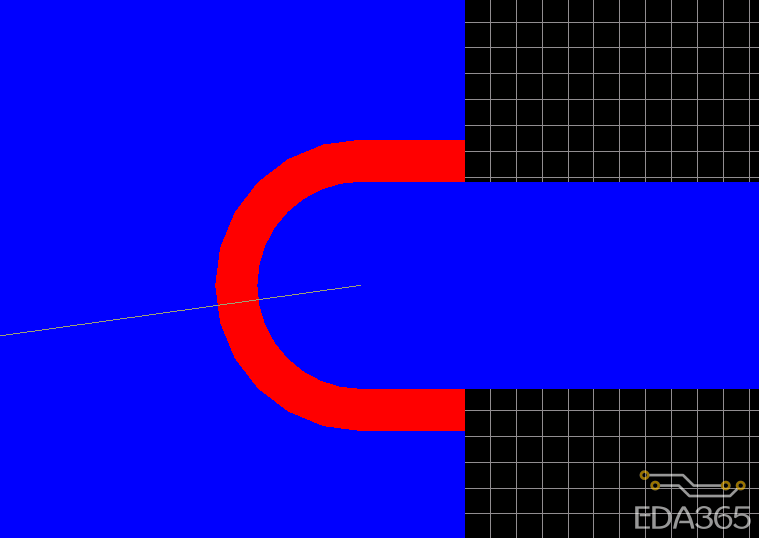

可以看到规则规定了Track与Poly的间距为0.2mm,所以Repour Polygon之后就会有下面的现象:

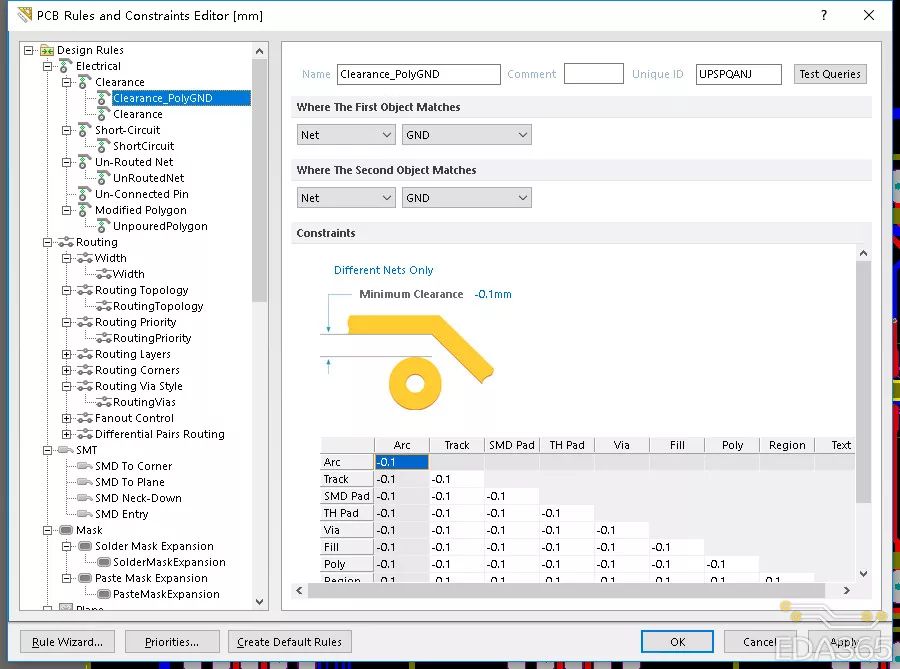

我们可以在Clearence下新建一个规则,取名叫Clearance_PolyGND,然后设置Where The First Object Mathces为Net-GND,Where The second object Matches也为Net-GND,意思就是这个规则所应用在的目标物体都选择为GND网络,然后设置Minimum Clearance为-0.1mm,如果设置为0mm的话,重新敷铜之后还有有点间隙,设置成负数之后重新敷铜就会完全连接,但是这个负数的绝对值不能太大,你可以试试。设置如下:

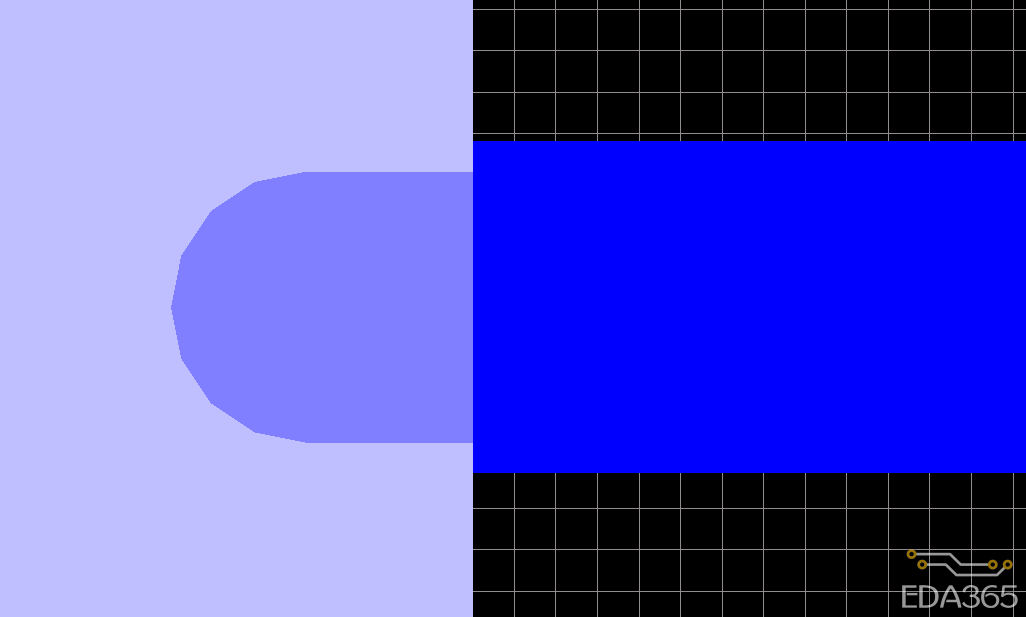

设置完之后重新敷铜:

可以看出来敷铜和右侧的Track完全连接在一起并且已经“伸进去”了一点,这“伸进去”的长度就是|-0.1|mm,是不是很神奇,原来AD的规则还能这样用!其实这是最简单的用法,AD的规则还能使用Query来查找匹配,和脚本一样,功能十分强大!!

-

AD

+关注

关注

27文章

868浏览量

150359 -

GND

+关注

关注

2文章

539浏览量

38731

原文标题:领福利啦!丨EDA365:电巢APP全国招募“体验官”

文章出处:【微信号:eda365wx,微信公众号:EDA365电子论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PADS9.5:Rules_1——Clearance

密集元件组成的PCB怎样设置规则DRC规则?

请问在哪里可以设置外设寄存器的user和privilege模式?设置的过程应该遵循怎样的规则?

差分对线距规则设置为6mil是因为在clearance中设置最小间隔为10mil就会报错吗?

铺铜和Clearance规则的优先级

【Altium小课专题 第114篇】不同元素之间的间距规则如何进行设置?

pcb覆铜规则设置

PCB设计的线宽线距与孔径规则设置注意事项

AD学习问题记录(二):pcb设计规则检查报错Silk To Solder Mask Clearance Constraint

怎样操作AD设置Clearance规则

怎样操作AD设置Clearance规则

评论