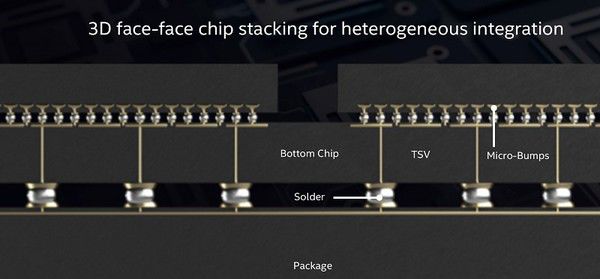

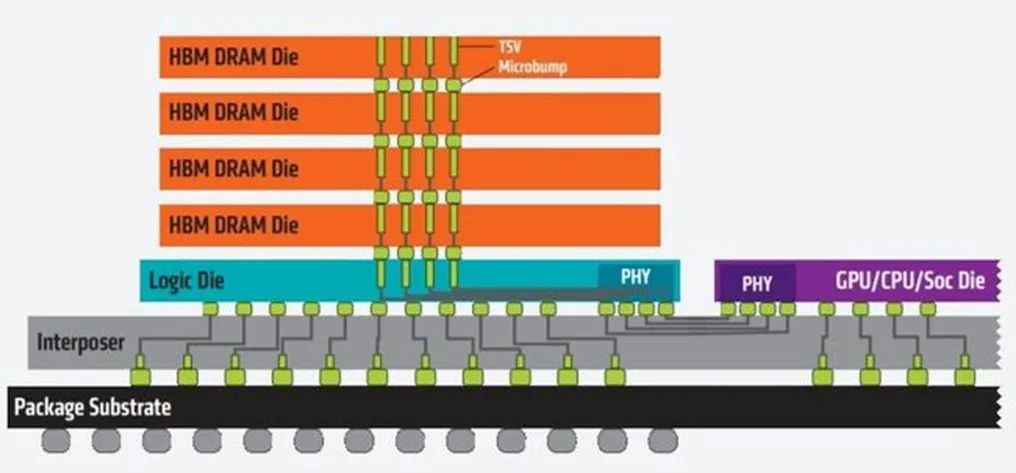

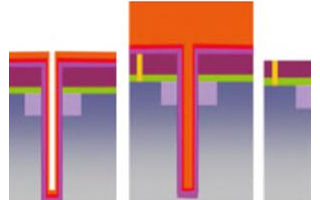

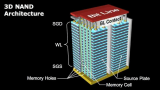

从英特尔所揭露的技术资料可看出,Foveros本身就是一种3D IC技术,透过硅穿孔(Through-Silicon Via, TSV)技术与微凸块(micro-bumps)搭配,把不同的逻辑芯片堆叠起来。

其架构概念就是在一块基础的运算微芯片(compute chiplet)上,以TSV加上微凸块的方式,堆叠其他的运算晶粒(die)和微芯片(chiplets),例如GPU和记忆体,甚至是RF元件等,最后再把整个结构打包封装。

而英特尔目前所使用的制程已达到10纳米,预计也可以顺利推进至7纳米,也此透过此3D封装技术,将可在单一芯片中达成绝佳的运算效能,并持续推进摩尔定律。

英特尔更特别把此技术称为「脸贴脸(Face-to-Face)」的封装,强调它芯片对芯片封装的特点。而要达成此技术,TSV与微凸块(μbumps)的先进制程技术就是关键,尤其是凸块接点的间距(pitch)仅有约36微米(micron),如何透过优异的打线流程来达成,就非常考验英特尔的生产技术了。

图六: Foveros的TSV与微凸块叠合示意(source: intel)

但是英特尔也指出,Foveros技术仍存在三个挑战,分别为散热、供电、以及良率。由于多芯片的堆叠,势必会大幅加大热源密度;而上下层逻辑芯片的供电性能也会受到挑战;而如何克服上述的问题,并在合理的成本内进行量产供货,则是最后的一道关卡。

依照英特尔先前发布的时程,「Lakefield」处理器应该会在今年稍晚推出,但由于英特尔没有在COMPUTEX更新此一产品的进度,是否能顺利推出仍有待观察。

-

英特尔

+关注

关注

61文章

10049浏览量

172757 -

逻辑芯片

+关注

关注

1文章

156浏览量

30723

原文标题:其他「小钢炮」都一边玩去吧

文章出处:【微信号:eda365wx,微信公众号:EDA365电子论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于TSV的3D-IC关键集成技术

芯片先进封装硅通孔(TSV)技术说明

成功量产!德明利实现SATA SSD存储控制芯片关键IP和技术平台全自研

TSV三维堆叠芯片的可靠性问题

先进封装中的TSV/硅通孔技术介绍

先进封装中互连工艺凸块、RDL、TSV、混合键合的新进展

一文了解硅通孔(TSV)及玻璃通孔(TGV)技术

开启高性能芯片新纪元:TSV与TGV技术解析

HBM:突破AI算力内存瓶颈,技术迭代引领高性能存储新纪元

TSV 制程关键工艺设备技术及发展

TSV与μbumps技术是量产关键

TSV与μbumps技术是量产关键

评论