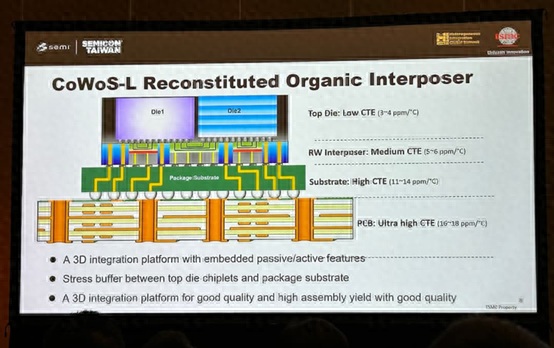

针对HPC芯片封装技术,台积电已在2019年6月于日本VLSI技术及电路研讨会(2019 Symposia on VLSI Technology & Circuits)中,提出新型态SoIC(System on Integrated Chips)之3D封装技术论文;透过微缩凸块(Bumping)密度,提升CPU/GPU处理器与存储器间整体运算速度。

整体而言,期望借由SoIC封装技术持续延伸,并作为台积电于InFO(Integrated Fan-out)、CoWoS(Chip on Wafer on Substrate)后端先进封装之全新解决方案。

运用垂直叠合与微缩体积方法,3D封装成功提升HPC工作效率

由于半导体发展技术的突破、元件尺寸逐渐微缩之际,驱使HPC芯片封装发展必须考量封装所需之体积与芯片效能的提升,因此对HPC芯片封装技术的未来发展趋势,除了现有的扇出型晶圆级封装(FOWLP)与2.5D封装外,将朝向技术难度更高的3D封装技术为开发目标。

所谓的3D封装技术,主要为求再次提升AI之HPC芯片的运算速度及能力,试图将HBM高频宽存储器与CPU/GPU/FPGA/NPU处理器彼此整合,并藉由高端TSV(硅穿孔)技术,同时将两者垂直叠合于一起,减小彼此的传输路径、加速处理与运算速度,提高整体HPC芯片的工作效率。

台积电与Intel积极推出3D封装,将引领代工封测厂一并跟进

依现行3D封装技术,由于必须垂直叠合HPC芯片内的处理器及存储器,因此就开发成本而言,比其他两者封装技术(FOWLP、2.5D封装)高出许多,制程难度上也更复杂、成品良率较低。

目前3D封装技术已对外公告的最新成果,现阶段除了半导体代工制造龙头台积电最积极,已宣布预计于2020年导入量产SoIC和WoW(Wafer on Wafer)等3D封装技术外,另有IDM大厂Intel也提出Foveros之3D封装概念,将于2019下半年迎战后续处理器与HPC芯片之封装市场。

随着半导体代工制造商与IDM厂陆续针对3D封装技术投入研发资源,也将引领另一波3D封测技术风潮,相信代工封测厂(如日月光、Amkor等)也将加紧脚步,跟上此波3D封装技术的发展趋势。

-

台积电

+关注

关注

44文章

5629浏览量

166378 -

intel

+关注

关注

19文章

3481浏览量

185897

原文标题:OnePlus 7 Pro评测:诠释快的新定义

文章出处:【微信号:Qualcomm_China,微信公众号:高通中国】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

台积电、Intel推出3D封装,引领代工封测厂跟进

台积电、Intel推出3D封装,引领代工封测厂跟进

评论